Таким образом, чтобы обратится блочному устройству на мастер диску к первой primary таблице нужно обратится к специальному файлу в директории /dev

/dev/hda1 c 3 номером ядра и адресом 0xf000

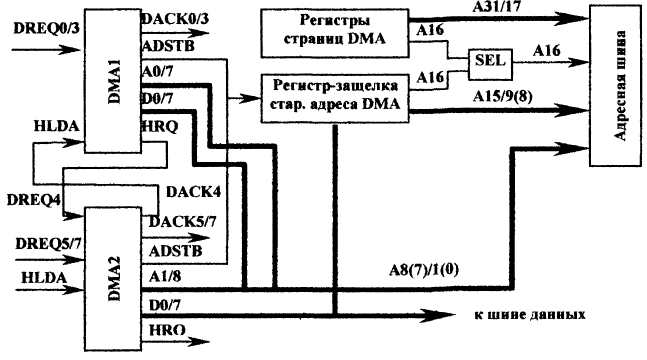

Direct Memory Access Controller (DMAC),

Современные платы имеют вспомогательный процессор Direct Memory Access Controller (DMAC), который контролирует передачу данных от низкоуровневых драйвером устройства в оперативную память. Его наличие позволяет использовать адресацию более 32бит и, следовательно, подключать большее количество портов для обслуживания оборудования.

Контролер имеет 4 канала. Для IBM PC XT

Память-память

Свободен

Обмен с контролером гибких дисков

Обмен с контролером жесткого диска.

Дальнейшее развитие – появление дополнительных контролеров в каскаде. Пример IBM PC

В работе DMA различают два режима – цикл ожидания и активный цикл.

S0 – ожидание до появление сигнала DREQi

S1 - первое состояние обслуживания. Наступает когда приходит запрос DREQi Контролер запрашивает разрешение у процессора на захват системной шины. После получения подтверждения, переходит в рабочее состояние

S2…-Sn – рабочее состояние (циклы DMA) идет передача

SW – состояние ожидания, по сигналу READY от устойств

Из цикла ожидания котроллер может быть переведен в состояние программирования. ( Chip Select). В процессе программирования контролеру передается :

- Начальный адрес памяти для обмена

- Уменьшенное на 1 количество передаваемых байтов

- Направление обмена

- Режим работы

- Направление изменения адреса

После программирования канал «демаскируется» и ожидает появление сигнала.

Обмен данными может идти в 4 редимах

- режим одиночной передачи. После каждой передачи системная шина отпускается.

- режим блочной передачи. Шина не освобождается до тех пор пока не будет передан весь блок.

- передача по требованию. Передача идет непрерывно, пока активен сигнал запроса. Режим для медленных устройств.

- Каскадный режим. Режим позволяет использовать дополнительные контролеры. Когда недостаточно 4 каналов DMA.

Типы передач

- Память – память использовался в XT для переноса больших областей данных. Теперь 0 канал используется для каскадного обмена.

- Автоинициализация – После завершения передачи – канал маскируется и парепрограммируется.

- режим фиксирования приоритета. Каскадный режим 0 – всегда маскирован 3 имеет минимальный приоритет. Первый ведомый контролер подключается сначала к 0 и имеет максимальный приоритет. Далее второй контролер к 1 ( при этом он тоже маскируется) и т.д.

- Циклический сдвиг приоритетов. Каждому каналу на котором произошла передача назначается наименьший приоритет.

- Сжатие времени. Если характеристики быстродействия двух устройств совпадают DMA убирает 2 цикла CLK (такты ожидания).

Подсистема прерываний

Дата добавления: 2017-06-13; просмотров: 1678;