Запоминающие устройства цифровой техники

ЗУ предназначены для записи, хранения и выдачи информации, представленной в виде цифрового кода. Основными характеристиками ЗУ являются: информационная емкость и быстродействие. Эти характеристики противоречивы – при улучшении одного параметра неизбежно ухудшается другой. Поэтому используется несколько ЗУ с различными характеристиками:

СОЗУ – сверхоперативные с малой емкостью (несколько слов), но с большим быстродействием.

ОЗУ – емкостью в тысячи слов и быстродействием  с.

с.

ВЗУ – внешние ЗУ - емкостью в миллионы слов r =  с.

с.

СОЗУ и ОЗУ – это как правило БИС, а ВЗУ – это электромеханические устройства с магнитным носителем информации (т.е. магнитофоны, магнитные диски, ленты, барабаны, флеш-карты и т.д.).

В процессе работы информация изменяется (считывается и записывается) в ОЗУ, СОЗУ и ВЗУ. Однако есть и такая информация, которая не должна меняться, например различные константы, цифровые коды букв алфавита, таблицы функций и т.д. Такую информацию записывают в ПЗУ - постоянные запоминающие устройства.

ОЗУ – типичный пример ОЗУ – параллельный регистр на триггерах.

При увеличении емкости ОЗУ возникает проблема доступа к каждому элементу памяти. Эта задача решается с помощью адресной организации ЗУ с использованием дешифратора кода адреса. Дешифратор с n входами дешифрирует  состояний регистра. Поэтому при четырех входах можно обратиться к 16 элементам памяти, а при десяти входах – к 1024 элементам и т.д.

состояний регистра. Поэтому при четырех входах можно обратиться к 16 элементам памяти, а при десяти входах – к 1024 элементам и т.д.

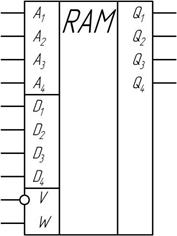

Пример ОЗУ в интегральном исполнении приведен на рис. 2.27.

Рис. 2.27 ОЗУ К155РУ2

К155РУ2 – ОЗУ с произвольным доступом.

адресные входы;

адресные входы;

информационные входы;

информационные входы;

– выходы;

– выходы;

V и W – управляющие входы.

Схема содержит 4 адресных входа, позволяющие создать  - адресов, в каждый из которых можно поместить 4 бита информации, то есть четырех разрядное слово. Полная емкость составляет 64 бита.

- адресов, в каждый из которых можно поместить 4 бита информации, то есть четырех разрядное слово. Полная емкость составляет 64 бита.

Если V = 0 и W = 0 – то обеспечивается режим записи с информационных входов  в ячейку, соответствующую коду адреса

в ячейку, соответствующую коду адреса

При V = 0 и W = 1 микросхема переходит в режим считывания информации на  с ячейки, соответствующую коду адреса

с ячейки, соответствующую коду адреса

Если V = 1 и W = 0 – то осуществляется режим сквозного переноса информации с  на

на  .

.

V = 1 и W = 1 – режим хранения информации.

Микросхемы позволяют наращивать емкость, то есть

два ИС – 32 слова, три – 48 и т.д.

К155РЕ21 – преобразователь двоичного кода в код знаков русского алфавита.

К155РЕ22 – латинский алфавит.

К155РЕ23 – код арифметических знаков и цифр.

3. Последовательностные устройства

Триггер (trigger – с англ. спусковой крючок огнестрельного оружия).

Это устройство, обладающее двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего кратковременного управляющего сигнала.

Триггеры в современной электронике могут быть созданы как из отдельных логических элементов, так и в виде специализированных интегральных микросхем, присутствующих во всех сериях.

Основное назначение триггеров в цифровых схемах – хранить выработанные логическими схемами результаты – биты информации.

Классификация триггеров:

1. По характеру изменения сигналов:

· Потенциальные (статические)

· Импульсные (динамические)

Потенциальные реагируют на изменение потенциала на входах, изменением потенциала на выходах (уровни логического нуля и единицы)

Импульсные реагируют на перепады потенциала, т.е. управляется фронтами импульсов (передним или задним, т.е. переходом с 0 на 1 или с 1 на 0).

2. По способу управления:

· Асинхронные

· Синхронные

Асинхронные – это триггеры, переходящие из одного состояния в другое в темпе поступления сигналов на входы.

Синхронные - это триггеры, переходящие из одного состояния в другое только при наличии синхронизирующего (стробирующего) тактового сигнала.

3. По функциональному признаку:

· RS, T, D, JK и т.д.

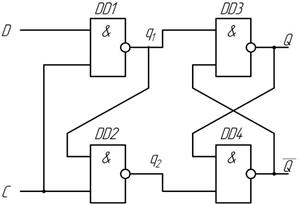

Триггерная ячейка

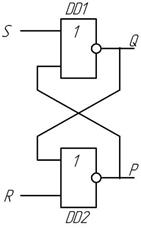

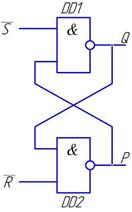

Триггерная ячейка это симметричная структура из двух инвертирующих элементов (рис. 3.1).

Рис. 3.1 Триггерная ячейка

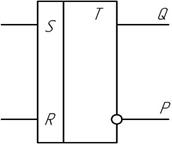

В момент включения питания с вероятностью 50/50 включенным (выключенным) окажется элемент U1. Такая ячейка имеет два устойчивых состояния, но не имеет входов управления, поэтому более совершенной является ячейка, состоящая из пары двухвходовых логических элементов ИЛИ-НЕ либо И-НЕ, охваченных перекрестной положительной обратной связью. На рис 3.2(а) приведена схема триггера, имеющая входы управления R и S, а также выходы Q и P, а на рис. 3.2(в) его условное обозначение на схемах.

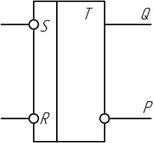

а в

Рис. 3.2 Схема RS-триггера на элементах ИЛИ-НЕ (а) и его условное изображение (в)

Симметрия схемы не означает симметрии электрических режимов обоих каскадов. За счет перекрестного соединения выходов и входов создаются условия, при которых при отсутствии входных сигналов один из логических элементов будет закрыт, а другой – открыт.

Одному из выходов триггера присваивают наименование прямого Q, а другому наименование инверсного  или Р.

или Р.

Состояние триггера отождествляют с сигналом на выходе Q. Перевод триггера в единичное состояние называют установкой (set) триггера, а устанавливающий сигнал и вход, на который он воздействует обозначают S.

Перевод триггера в нулевое состояние называют сбросом (reset), а сигнал и вход обозначают R.

Работа схемы

Пока на R и S сигналы равны 0, триггер находится в одном из двух устойчивых состояний. Предположим, что Q = 1 (триггер установился при включении). Эта логическая 1 по цепи обратной связи поступает на вход DD2 и вызывает появление на выходе  нулевого логического уровня. В свою очередь, нулевой уровень с выхода

нулевого логического уровня. В свою очередь, нулевой уровень с выхода  , поступая по цепи обратной связи на вход DD1, поддерживает выходной сигнал Q в состоянии 1.

, поступая по цепи обратной связи на вход DD1, поддерживает выходной сигнал Q в состоянии 1.

При первоначальном включении триггер может остаться и в сброшенном состоянии, т.е. Q = 0. Это состояние также является устойчивым, т.к. можно показать, что второй элемент триггера будет при этом вырабатывать логическую 1.

Режим RS-триггера, когда оба управляющих сигнала R и S неактивны, называют режимом хранения.

Временная диаграмма работы триггера приведена на рис 3.3.

Рис. 3.3. Диаграмма работы триггера на элементах ИЛИ-НЕ

Оба элемента триггера DD1 и DD2 переключаются не одновременно, а последовательно друг за другом. Из диаграммы видно, что есть моменты незаконного состояния выходов, когда  . Поэтому управляемая триггером схема, получив на вход не предусмотренную комбинацию сигналов, сформирует на своих выходах также нечто совершено не предусмотренное алгоритмом ее работы.

. Поэтому управляемая триггером схема, получив на вход не предусмотренную комбинацию сигналов, сформирует на своих выходах также нечто совершено не предусмотренное алгоритмом ее работы.

Время задержки распространения сигнала  , где

, где  – максимальное время распространения сигнала через один логический элемент.

– максимальное время распространения сигнала через один логический элемент.

Запускающие импульсы S и R не должны быть слишком короткими, так как обратная связь в триггере может не успеть замкнуться, поэтому длительность входного импульса активная

Если на RS-триггер подать одновременно оба входных сигнала, т.е. сделать S = R = 1, то на обоих выходах Q и  появятся нули. Если теперь одновременно снять единицы с входов R и S, то оба элемента начнут переключаться в единичное состояние. Какой элемент одержит в этом поединке победу, будет зависеть от их коэффициентов усиления, несимметричности элементов и других неизвестных заранее факторов.

появятся нули. Если теперь одновременно снять единицы с входов R и S, то оба элемента начнут переключаться в единичное состояние. Какой элемент одержит в этом поединке победу, будет зависеть от их коэффициентов усиления, несимметричности элементов и других неизвестных заранее факторов.

В результате триггер установится в неопределенное, неуправляемое состояние. Поэтому комбинация R = S = 1 считается запрещенной.

Дискретное время

Переключения триггера происходит через определенные отрезки времени. В интервалах между срабатываниями его состояния сохраняются неизменными. За произвольный промежуток времени, в течение которого работает триггер, может произойти только конечное количество срабатываний. Поэтому работу триггера рассматривают в дискретном времени, для чего реальное время разбивается на интервалы, которые нумеруются, начиная с какого-то момента. Каждый интервал времени называют тактом. Смена тактов происходит скачками.

Дискретное время складывается из отдельных тактов, т.е. учитываются не секунды, минуты и т.д., а соседние такты, длительность которых для описания работы устройства не имеет значения. Функция внешних переходов определяется состоянием входов и выходов в двух соседних тактах – до и после срабатывания. Эту пару тактов обозначают  и

и  .

.

шкала дискретного времени

В промежутках между срабатываниями триггер сохраняет свое состояние до следующего такта.

RS-триггеры

RS-триггеры – это триггеры с раздельными входами.

S (set – включение, взведение, установка единицы)

R (reset – сброс, установка нуля)

Q – основной – прямой выход

P – инверсный выход

Соблюдается условие:

если Q = 1, то P = 0

Q = 0, то P = 1

т.е. P =  , а Q =

, а Q =  или P· Q = 0.

или P· Q = 0.

Qn – предыдущее состояние на выходе Q;

Qn+1 – новое состояние триггера после прихода Sn или Rn сигнала.

Поведение триггера можно описать следующими логическими выражениями:

Qn+1 = (Sn + Qn)

, где Qn

, где Qn  =

=

Составим таблицу функционирования RS-триггера. Учитывая, что Qn - предыдущее состояние триггера относится к входным воздействиям, получим три независимых аргумента и 23 = 8 строк таблицы 3.1.

Таблица 3.1

Состояния RS-триггера с прямым управлением

| Входные воздействия | Выход | Примечание | ||

| Sn |

| Qn | Qn+1 | Режим |

| хранение | ||||

| запись нуля | ||||

| запись единицы | ||||

| X | ||||

| X | н/о |

Из таблицы можно сделать следующие выводы:

1. Состояние триггера не изменяется, если управляющие сигналы на входах отсутствуют Sn = 0,  = 0, что обеспечивает режим хранения информации.

= 0, что обеспечивает режим хранения информации.

2. Сигнал  = 1 при Sn = 0 устанавливает на выходе Q в n+1 такте Qn+1 уровень логического «0» независимо от предыдущего состояния Qn – это режим записи нуля (сброс, обнуление, очистка, гашение).

= 1 при Sn = 0 устанавливает на выходе Q в n+1 такте Qn+1 уровень логического «0» независимо от предыдущего состояния Qn – это режим записи нуля (сброс, обнуление, очистка, гашение).

3. Сигнал Sn = 1 при  = 0 устанавливает на выходе Q уровень логической «1», независимо от предыдущего состояния Qn, что соответствует записи единицы (установка, взведение).

= 0 устанавливает на выходе Q уровень логической «1», независимо от предыдущего состояния Qn, что соответствует записи единицы (установка, взведение).

4. Состояние триггера при Sn = 1 и  = 1 неопределенно и является запрещенным, т.е. должно выполняться условие

= 1 неопределенно и является запрещенным, т.е. должно выполняться условие  S = 0.

S = 0.

S-триггер можно построить и на элементах И-НЕ.

S-триггер можно построить и на элементах И-НЕ.

a в с

Рис. 3.4. Структура RS-триггера на элементах И-НЕ (а), его условное обозначение на схемах (в), и диаграмма включения (с)

Как видно из рис. 3.4а структура триггера повторяет структуру триггера из рис. 3.2а, но закон функционирования имеет иной, поскольку элементы И-НЕ переключаются сигналами логического нуля. Этот вариант триггера называют RS-триггером с инверсными входами (на рис 3.2а – с прямыми входами), а в условном обозначении входов добавляются знаки инверсии (рис. 3.4в). Процесс включения триггера (рис. 3.4с) не отличается от предыдущего, только всё наоборот, что отражено в таблице 3.2.

Таблица 3.2

Состояния RS-триггера с инверсным управлением

| Входные воздействия | Выход | Примечание | ||

| Sn |

| Qn | Qn+1 | Режим |

| н/о | ||||

| запись единицы | ||||

| запись нуля | ||||

| X | хранение | |||

| X |

Например: К155ТР2 содержит 4 асинхронных триггера, причем два из них имеют по два входа  .

.

Рассмотренные  S-триггеры относятся к асинхронным, т.к. переход их из одного состояния в другое происходит в темпе поступления сигналов на информационные (RS) входы и не связан (переход) с тактовыми сигналами.

S-триггеры относятся к асинхронным, т.к. переход их из одного состояния в другое происходит в темпе поступления сигналов на информационные (RS) входы и не связан (переход) с тактовыми сигналами.

Основной недостаток асинхронных триггеров – незащищенность перед опасными состязаниями сигналов, когда сигналы проходят разными путями, имеют разную задержку и могут вызвать ложные срабатывания схемы.

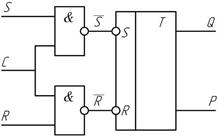

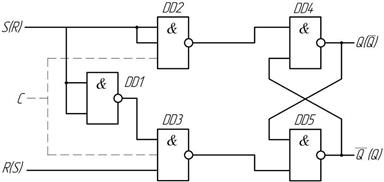

В синхронном триггере помимо информационных имеется вход тактовых (синхронизирующих) сигналов и переключения триггера происходят только при наличии тактового сигнала, т.е. при с = 1 (рис. 3.5).

Рис.3.5. Структура синхронного RS-триггера

Характерно, что двойное инвертирование входных сигналов превратили инверсный триггер в триггер с прямым управлением.

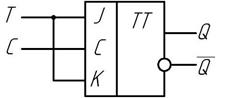

Двухступенчатый триггер (MS – структура)

Master-slave (ведущий – ведомый, хозяин – слуга).

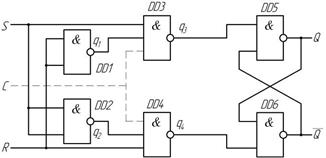

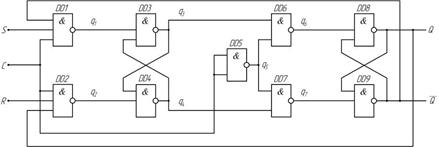

MS триггер состоит из двух одинаковых синхронных триггеров со статическим управлением, запись информации в которые происходит в разные моменты времени (рис. 3.6).

Рис. 3.6. Структура двухступенчатого триггера

Ведущий триггер М образован элементами DD1 – DD4.

Ведомый триггер S образован элементами DD6 – DD9.

Тактовый вход ведущего триггера связан со входом ведомого инвертором DD5. До прихода тактового импульса С = 0 входные элементы DD1 и DD2 заперты,  и M-триггер хранит информацию от предыдущего такта.

и M-триггер хранит информацию от предыдущего такта.

Ведомый S-триггер, на тактовом входе которого действует  , открыт и повторяет состояние ведущего: Qn = q3,

, открыт и повторяет состояние ведущего: Qn = q3,  .

.

С приходом тактового импульса С = 1 в ведущий триггер заносится информация со входов S и R. Ведомый S-триггер в это время блокирован, поскольку  . С прекращением тактового импульса запирается ведущий триггер, а ведомый открывается и принимает состояние ведущего. С этого момента сигналы на выходах будут:

. С прекращением тактового импульса запирается ведущий триггер, а ведомый открывается и принимает состояние ведущего. С этого момента сигналы на выходах будут:  ,

,  .

.

Таким образом, у двухступенчатых триггеров формирование нового состояния происходит за два такта, поэтому иногда их называют двухтактными. Двухступенчатые триггеры MS-структуры условно обозначают двумя буквами ТТ, что отображает их внутреннее устройство.

На рис.3.6 штриховыми линиями показаны также входы Sa̅ и R̅a, предназначенные для асинхронной установки триггера в единичное и нулевое состояние, минуя информационные и тактирующий входы. Существенно, что эти входы обладают приоритетом по отношению к другим входам триггера, т. к. дают возможность обратиться непосредственно к логическим элементам выходной триггерной ячейки.

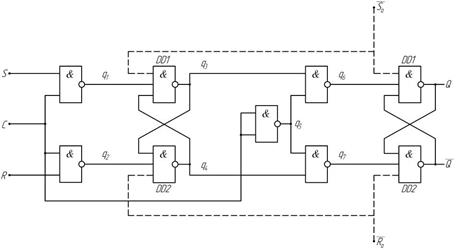

На рис. 3.7 приведена диаграмма переключений двухступенчатого триггера, поясняющая работу его элементов.

Рис. 3.7. Временная диаграмма работы двухступенчатого триггера MS-структуры

Вывод: Допускается смена входной информации и во время действия тактового импульса, так как перезапись сигналов из первой ступени во вторую происходит с окончанием тактового импульса, то есть по принципу внутренней задержки.

Из структурной схемы следует, что переключение ведущей ступени М происходит с задержкой

Длительность тактового импульса должна быть такой же  так как при подаче переключающего сигнала, например S последовательно меняют свое состояние 1,2 и 3 элементы.

так как при подаче переключающего сигнала, например S последовательно меняют свое состояние 1,2 и 3 элементы.

Время задержки переключения ведомой ступени S больше  на время переключения инвертора

на время переключения инвертора  . Следовательно

. Следовательно  , а общее разрешающее время:

, а общее разрешающее время:

Достоинство МS триггера: Он непрозрачен по управляющим R и S входам ни при С = 0, ни при С = 1. Каждая ступень его сама по себе прозрачна, но включены ступени последовательно, и какая-нибудь одна из них всегда оказывается закрытой – или синхросигналом, или его отсутствием. Таким образом, в этом МS триггере при С = 1 (и тем более при С = 0) никакое изменение на управляющем входе не может само по себе, без переключения С – сигнала, проникнуть на вход. Триггер может изменить состояние выхода только по срезу С – сигнала.

В зарубежной литературе непрозрачные триггеры называют flip-flop (щелчок-хлопок) в отличие от прозрачных – latch (защелка).

Разновидности RS триггеров

Наличие неопределенных состояний (R = S) ограничивает функциональные возможности RS триггеров.

Подключая ко входам RS-триггера схему управления (создавая триггерную систему), можно обеспечить такое положение, что при всех входных комбинациях (в том числе и S = R = 1 или S = R = 0 для  триггера), сигналы на выходе триггера будут иметь определенные, наперед известные значения.

триггера), сигналы на выходе триггера будут иметь определенные, наперед известные значения.

Возможны 4 варианта неопределенности:

При всех сочетаниях входных сигналов триггер функционирует подобно исходному RS или  триггеру.

триггеру.

Каждая такая разновидность считается самостоятельным типом триггера и имеет свое наименование.

1. Триггер, после снятия запрещенной комбинации входных сигналов принимающий единичное состояние  называют S-триггер.

называют S-триггер.

2. Триггер, принимающий нулевое состояние  называют R-триггер.

называют R-триггер.

3. Триггер, сохраняющий свое предыдущее состояние  называют E-триггер (exelusive – исключающий, особенный).

называют E-триггер (exelusive – исключающий, особенный).

4. Триггер, меняющий состояние на противоположное  называют JK триггером.

называют JK триггером.

Каждый из этих триггеров может быть асинхронным и синхронным.

Схема S или (R) триггера приведена на рис. 3.8.

Рис. 3.8. Схема S (R) триггера

Работа: Когда S = 1, на выходах DD1 и DD2 установятся нули. Логический нуль с выхода DD1 запретит работу элементу DD3, установив на его выходе логическую единицу независимо от сигналов на входе R.

Нулевой уровень на выходе DD2 и единичный – на выходе DD3 обеспечивают появление единицы в новом такте  независимо от сигнала на входе R. Это S-триггер.

независимо от сигнала на входе R. Это S-триггер.

Та же схема будет работать как R-триггер, если поменять местами метки R и S и  и

и  .

.

Состояния S и R триггеров описывает табл. 3.3

Таблица 3.3

Функционирование S и R триггеров

| Такт n | Такт

| ||

|

| S-триггер | R-триггер |

|

| ||

Схема Е-триггера приведена на рис. 3.9.

Рис. 3.9 Структура Е-триггера

Работа: При одновременном сочетании на входах сигналов  на выходах элементов DD3 и DD4 будет

на выходах элементов DD3 и DD4 будет  , которые обеспечат режим хранения информации выходной ячейки, то есть ее состояние сохранится неизменным.

, которые обеспечат режим хранения информации выходной ячейки, то есть ее состояние сохранится неизменным.

Таблица истинности для Е-триггера подтверждает это положение (табл.3.4).

Таблица 3.4

Функционирование Е-триггера

| Такт n | Такт n+1 | |

|

|

|

| ||

|

Схема асинхронного JK-триггера приведена на рис. 3.10.

Рис. 3.10. Структура асинхронного JK-триггера

Этот тип триггеров не имеет неопределенных состояний, т.к. при комбинации входных сигналов Jn = Kn = 1 происходит опрокидывание триггера и выходные сигналы меняют свои значения:

Вход J (Joker) играет роль входа S, а вход К (Kill) соответствует входу R.

Работа: При Jn = Kn = 0 сигналы на выходах U1 и U2 независимо от сигналов обратной связи Q и P будут q1 = q2 = 1, что представляет нейтральную комбинацию для выходной триггерной ячейки (U5 и U6), которая хранит ранее записанную информацию. Элементы U3 и U4 играют роль линий задержки и не оказывают логического действия (без этих элементов возможно возникновение т.н. автогенерации из-за разницы моментов прихода сигналов.

При Jn = Kn = 1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свои значения на противоположные. Порядок переключения состояний JK триггера приведен в табл. 3.5.

Таблица 3.5

Состояния JK-триггера

| Такт n | Такт n+1 | ||||||

|

|

|

| ||||

0 0

| |||||||

0 0

1 1

| |||||||

1 1

| |||||||

I. При J = K = 0. Триггер сохраняет свое предыдущее состояние (режим хранения).

II. J = 0, K = 1. Триггер переходит в нулевое состояние, независимо от предыдущего. Следовательно, K равносильно R.

III. J = 1, K = 0. Триггер устанавливается в единичное состояние, независимо от предыдущего. Следовательно, J равносильно S.

IV. J = K = 1. Триггер меняет свое состояние на противоположное, то есть

n.

n.

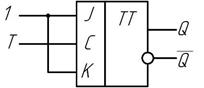

Двухступенчатый JK-триггер.

Предупреждение автогенерации просто и эффективно обеспечивается в триггерах с двухступенчатым управлением, поскольку обе ступени триггера тактируются отдельно (рис. 3.11).

Рис. 3.11. Структура двухступенчатого JK-триггера

Ведущий триггер образован элементами DD1 – DD4, ведомый DD6 – DD9. Элемент DD5 выполняет роль инвертора и разделителя ступеней.

JK-триггеры относятся к универсальным устройствам, т.к. путем определенного соединения выводов они легко превращаются в триггеры других типов:

1) Если добавить инвертор, то получим D-триггер.

2) Асинхронный счетный триггер.

3) Синхронный счетный триггер.

D-триггер (Delay – задержка)

D-триггеры имеют один информационный вход D по которому можно установить триггер в единичное или нулевое состояние, правда с задержкой на один такт.

Схема  –триггера со статическим управлением приведена на рис. 3.12.

–триггера со статическим управлением приведена на рис. 3.12.

Рис. 3.12. D-триггер со статическим управлением

Функциональная особенность этого типа триггеров состоит в том, что сигнал на выходе  в такте n+1 повторяет значение входного сигнала

в такте n+1 повторяет значение входного сигнала

в предыдущем такте n и сохраняет это состояние до следующего такта.

в предыдущем такте n и сохраняет это состояние до следующего такта.

При  , а при

, а при

| |

Таблица переходов  –триггера представлена в табл. 3.6

–триггера представлена в табл. 3.6

Таблица 3.6

Таблица переходов D-триггера

| Такт n | Такт n+1 | ||||||

| Сn |

|

|

| ||||

0 0

| |||||||

0 0

| |||||||

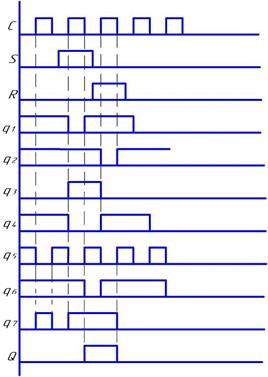

На рис. 3.13 приведена временная диаграмма переключений «прозрачного» D-триггера.

Рис. 3.13 Временная диаграмма работы «прозрачной» защелки

Это «прозрачный» триггер или «прозрачная защелка». Элементы DD3 и DD4 образуют ячейку памяти, а DD1 и DD2 – схему управления. В паузах между тактовыми импульсами элементы DD1 и DD2 закрыты и на их выходах существуют сигналы q1 = q2 = 1, что служит нейтральной комбинацией для основной ячейки памяти.

Такт импульса №3 еще не закончен, а  , то есть триггер не защелкнул эту информацию, поэтому длительность информационного импульса

, то есть триггер не защелкнул эту информацию, поэтому длительность информационного импульса  (

(  ) должна быть не меньше длительности тактового сигнала

) должна быть не меньше длительности тактового сигнала  (С). При С = 1 защелка становится прозрачной, поэтому любые изменения на информационном входе D немедленно отражаются на выходах триггера.

(С). При С = 1 защелка становится прозрачной, поэтому любые изменения на информационном входе D немедленно отражаются на выходах триггера.

С приходом тактового импульса С состояние элементов DD1 и DD2 определяется значением сигнала на входе  . Во всех случаях сигналы

. Во всех случаях сигналы  =

=  . По отношению к собственно триггеру (DD3 и DD4) сигналы

. По отношению к собственно триггеру (DD3 и DD4) сигналы  и

и  играют роль переключающих. Когда

играют роль переключающих. Когда  = 0 то при С = 1,

= 0 то при С = 1,  = 1,

= 1,  = 0, DD4 запирается и на его выходе установится

= 0, DD4 запирается и на его выходе установится  тогда как на входе DD3 действует

тогда как на входе DD3 действует  = 1 и

= 1 и  , отчего на выходе формируется

, отчего на выходе формируется  .

.

С окончанием тактового импульса (С = 0) на  =

=  = 1, что соответствует режиму хранения информации для ячейки памяти на элементах И-НЕ.

= 1, что соответствует режиму хранения информации для ячейки памяти на элементах И-НЕ.

Разрешающее время между двумя тактовыми импульсами, при котором триггер работает без сбоев:

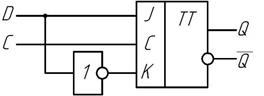

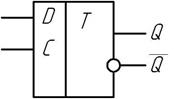

Условное обозначение «прозрачного» D-триггера приведено на рис 3.14.

Рис. 3.14. Условное обозначение D-триггера со статическим управлением

Представтели: К155ТМ7 (ТМ5) – 4 триггера с прямым статическим управлением.

Вывод:

Рассмотренный «прозрачный» триггер со статическим управлением имеет недостаток: информация на входе-D по времени действия должна перекрывать тактовый импульс-С. Это ограничивает круг его применений, не позволяет, в частности, использовать его в качестве Т-триггера.

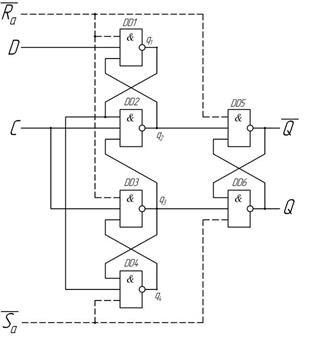

D-триггер с прямым динамическим управлением (рис. 3.15).

Известен также под названиями: триггер Вебба, триггер с самоблокировкой, схема трех триггеров, шестиэлементный триггер. Функциональные возможности триггера расширены за счет добавления асинхронных потенциальных входов R и S, обладающих приоритетом по отношению к другим входам.

Рис. 3.15. Схема 6-ти элементного D-триггера

Схема содержит 6 элементов И-НЕ, на которых собраны 3 триггера. Запись информации происходит по фронту перехода тактового импульса «С» от 0 к 1. Для асинхронного управления триггер оснащен входами  и

и  .

.

Как и в схеме «прозрачной» защелки информация на вход D должна быть подана до прихода переднего фронта сигнала С.

DD1 - DD4 – коммутирующие ячейки

DD5 – DD6 – ячейка памяти

Ячейка DD1 и DD2 работает при записи в основную ячейку памяти 0, а ячейка DD3 и DD4 при записи в основную ячейку памяти 1.

В паузах между тактовыми импульсами (С = 0) элементы DD2 и DD3 закрыты и  =

=  , что соответствует режиму хранения информации в выходной ячейке.

, что соответствует режиму хранения информации в выходной ячейке.

Состояние элементов DD1 и DD4 определяется сигналом D.

При

= 1, а

= 1, а  = 0 (на обоих входах DD4 присутствует логическая единица).

= 0 (на обоих входах DD4 присутствует логическая единица).

При

= 0, а

= 0, а  = 1 то есть

= 1 то есть  =

=  (но при С = 0).

(но при С = 0).

Если до прихода тактового импульса сигнал на входе D изменится, это отразится на элементах DD1 и DD4, но не скажется на состоянии элементов DD2 и DD3 (т.к. С = 0), а следовательно не изменится и на выходах триггера. С приходом тактового импульса (с = 1) снимается блокировка с элементов DD2 и DD3 и возникает такая комбинация  и

и  , которая приводит выходную ячейку в состояние

, которая приводит выходную ячейку в состояние  .

.

Пусть  , тогда до прихода такт. импульса (С = 0)

, тогда до прихода такт. импульса (С = 0)  = 1 и

= 1 и  =

=  . С началом тактового импульса состояние ячеек DD3 и DD4 не изменится (на обоих входах нейтральная комбинация), а выход элемента DD2 станет

. С началом тактового импульса состояние ячеек DD3 и DD4 не изменится (на обоих входах нейтральная комбинация), а выход элемента DD2 станет  = 0 (на всех входах логическая 1). Под воздействием сигнала

= 0 (на всех входах логическая 1). Под воздействием сигнала  = 0 выходная ячейка перейдет в состояние

= 0 выходная ячейка перейдет в состояние  или, если оно было таким, сохранит его. При

или, если оно было таким, сохранит его. При  состояния выходов будут

состояния выходов будут  = 0,

= 0,  = 1, элемент DD2 закрыт (

= 1, элемент DD2 закрыт (  = 1). С приходом тактового импульса (С = 1) элемент DD3 открывается (

= 1). С приходом тактового импульса (С = 1) элемент DD3 открывается (  , то есть возникнут условия опрокидывания выходной ячейки в состояние

, то есть возникнут условия опрокидывания выходной ячейки в состояние  .

.

С окончанием тактового импульса (С = 0) элементы DD2 и DD3 блокируются (  =

=  , обеспечивая режим хранения информации для выходной ячейки до следующего такта. Изменение информации на входе D в паузах между тактовыми импульсами будет отражаться на элементах DD1 и DD4, но не скажется на DD2 и DD3.

, обеспечивая режим хранения информации для выходной ячейки до следующего такта. Изменение информации на входе D в паузах между тактовыми импульсами будет отражаться на элементах DD1 и DD4, но не скажется на DD2 и DD3.

Выходная ячейка реагирует на состояние входа D только в момент перехода тактового импульса из 0 в 1. Допустим, во время действия тактового импульсного сигнала информация на D изменится и вместо  станет

станет  . На схеме это не отразится, так как элемент DD1 сохранит свое состояние

. На схеме это не отразится, так как элемент DD1 сохранит свое состояние  = 1, поскольку на его нижнем входе действует сигнал

= 1, поскольку на его нижнем входе действует сигнал  = 0. Изменение входного сигнала с

= 0. Изменение входного сигнала с  на

на  приведет к запиранию элемента DD1 (

приведет к запиранию элемента DD1 (  = 1). Однако изменение состояния

= 1). Однако изменение состояния  не отразиться на элементе DD2 в виду того, что сигнал

не отразиться на элементе DD2 в виду того, что сигнал  на нижнем входе удерживает элемент DD2 закрытым (

на нижнем входе удерживает элемент DD2 закрытым (  = 1).

= 1).

При этом уровень  = 1 в этом случае не скажется на элементе DD4, который останется закрытым благодаря

= 1 в этом случае не скажется на элементе DD4, который останется закрытым благодаря

Запись новой информации в триггер станет возможной только с окончанием текущего тактового импульса.

Типичными представителями этого класса триггеров являются триггеры: К155ТМ2, К561ТМ2.

На рис. 3.16 приведено условное графическое обозначение триггера К155ТМ2, а в табл. 3.7 описание его функциональных возможностей.

Дата добавления: 2017-05-02; просмотров: 2745;