Накопительные (параллельные) регистры

Назначение этого типа регистров – хранить двоичную информацию небольшого объёма в течение короткого промежутка времени. Объём хранимой информации определяется количеством триггеров, организованных в регистр, т.к. каждый триггер регистра хранит только один бит.

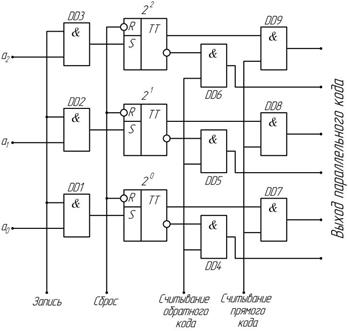

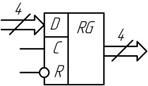

Схема параллельного регистра на 3 входаприведена на рис. 3.26.

Рис. 3.26 Регистр хранения на RS-триггерах

1. Перед началом работы триггеры регистра могут быть установлены в нулевое начальное состояние путём подачи импульса на шину «Сброс», соединенную с входами R всех триггеров.

Подготовленная для хранения информация может быть внесена в регистр при наличии импульса «Запись», который открывает входные конъюнкторы DD1 – DD3. Логические уровни входной информации установят триггеры регистра в состояние 1 или 0 на выходах Q.

2. Для считывания записанного числа подается импульс на вход «Считывание прямого кода». Во время считывающего импульса на выходах схем DD7 – DD9 получается набор , соответствующий прямым состояниям триггеров, повторяющих входной код. Существенно то, что после считывания, информация в триггерах сохраняется, поэтому считывание можно производить сколь угодно раз (при условии поддержания  и не подачи на вход

и не подачи на вход  импульса сброса).

импульса сброса).

Кроме того, регистр позволяет получить код обратный введенному коду. Обратный код используется, например, для вычитания чисел в двоичном коде. Обратный код – когда 1 превращается в 0, а 0 в 1. Обратный код числа получается на инверсных выходах триггеров, поэтому, подав на шину регистра «Считывание обратного кода» мы откроем конъюнкторы DD4 - DD6 и на их выходах получим обратный код числа.

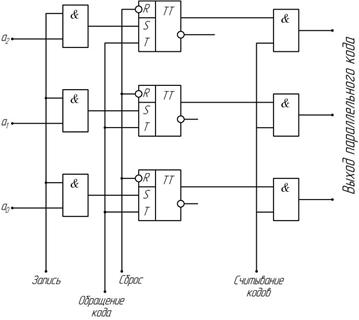

Эту же задачу можно решить применяя триггеры с дополнительным счетным Т входом рис. 3.27.

Рис. 3.27. Регистр на счетных триггерах

1.Процесс записи и считывания кода в регистр такой же как и в предыдущем примере.

2.При подаче импульса на входы «Обращение кода» все триггеры регистра меняют свое состояние на противоположное.

Преимуществом этого типа регистров является возможность получения как прямого так и обратного кода на одних и тех же выходных клеммах.

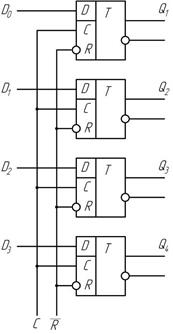

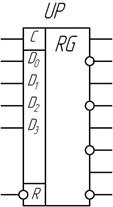

Регистровая память

Для запоминания многоразрядных слов можно использовать и прозрачный триггер-защелку, изображенный на рис. 3.12 на стр. 13. Набрав некоторое количество триггеров и объединив их тактовые входы и входы обнуления, получим многоразрядный регистр-защелку (рис. 3.28-а). По такому принципу устроены микросхемы К155ТМ5, К155ТМ7, К561ТМ3 и др. Изображение таких регистров на схемах приведено на рис. 3.28-в, а на рис. 3.28-с показано и вовсе упрощенное изображение такого регистра, когда вместо отдельных входов-выходов изображаются входные и выходные шины, в данном случае четырехразрядные. Например, триггеры 155ТМ5, ТМ7, 561ТМ3 можно рассматривать не только как четверки  -триггеров-защелок, но и как

-триггеров-защелок, но и как  - разрядные регистры-защелки.

- разрядные регистры-защелки.

а в с

Рис. 3.28. Регистр памяти а – развернутое изображение, в – УГО на схемах, с – упрощенное изображение с шинами

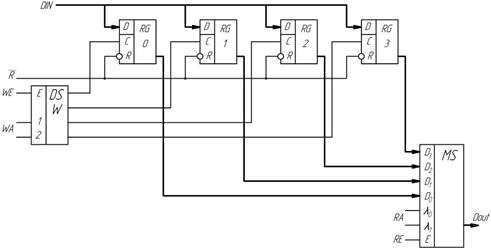

Сразу несколько регистров содержат микросхемы регистровой памяти, схема которой показана на рис. 3. 29.

Рис. 3.29. Схема регистровой памяти

DIN – шина входных данных (data in)

С – вход сигнала записи или загрузки (cloc)

R̅ - вход очистки регистра (reset)

шины выходов регистров

шины выходов регистров

WE – вход разрешения записи (write enable)

WA – вход адреса записи (write address)

DCW – дешифратор записи (decoder write)

RA – адрес чтения (read address)

RE – разрешение чтения (read enable)

DOUT – шина выходных данных (data out)

MS – мультиплексор чтения

Дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющие автономные адресные входы  и RA, поэтому можно одновременно записывать число в один из регистров и читать число из другого.

и RA, поэтому можно одновременно записывать число в один из регистров и читать число из другого.

Дата добавления: 2017-05-02; просмотров: 2800;