Дешифраторы и шифраторы

В общем виде дешифраторами и шифраторами называют устройства, предназначенные для распознавания различных кодовых комбинаций (слов), т.е. по сути, это одно и тоже логическое устройство, предназначенное для преобразования произвольного кода в произвольный.

Чтобы как то различать эти устройства, договорились, что дешифраторами будут являться преобразователи двоичного n-разрядного слова в унитарный 2n – разрядный код, все разряды которого, за исключением одного, равны нулю, а шифраторами будут называться устройства, выполняющие обратную задачу, т.е. из унитарного кода можно получить соответствующий двоичный. Надо заметить, что эта договоренность успешно нарушена, поэтому единственной практически приемлемой формой задания преобразователя становится таблица. Поскольку таблица воплощает в себе идею полного перебора вариантов, она способна задавать абсолютно любой закон.

Дешифратор (decoder)

Основой для построения дешифратора является логическая схема И (конъюнктор). Число входов каждого конъюнктора должно быть равно

n- количеству разрядов двоичного числа, а число требуемых схем «И» равно

N =

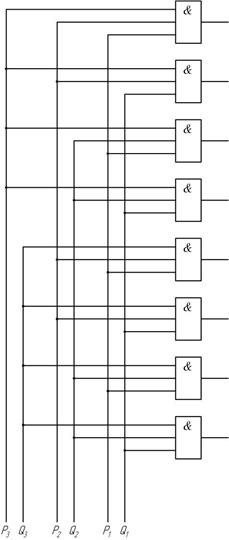

Рассмотрим дешифратор трехразрядного двоичного числа, схема которого изображена на рис. 2.1.

Q1, Q2, Q3 – прямые значения разрядов

P1, P2, P3 - инверсные значения разрядов, т.е. P = Q̅

N =  конъюнкторов, каждый на n = 3 входа.

конъюнкторов, каждый на n = 3 входа.

Построение дешифратора начнем со вспомогательной таблицы соответствия десятичных и двоичных чисел (табл. 2.1).

Таблица 2.1

Таблица перевода 10 - 2

| Десятичные числа | Двоичные числа | ||

| разряд | разряд | ||

| 100 | 22 | 21 | 20 |

| |

|

|

Рис. 2.1 Простейший дешифратор вида 3-8

Из всех N выходов дешифратора активный уровень имеется только на одном, а именно на том, номер которого равен поданному на вход двоичному числу, называемым кодом адреса. На всех остальных выходах дешифратора уровни напряжения неактивные. Формально описать работу дешифратора можно, задав список функций, отрабатываемых каждым из его выходов:

0 = P3 P2 P1 1 = P3 P2 Q1 2 = P3 Q2 P1 3 = P3 Q2 Q1

4 = Q3P2 P1 5 = Q3 P2 Q1 6 = Q3 Q2 P1 7 = Q3 Q2 Q1

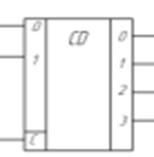

Реализация эти восьми выражений с помощью восьми трехвходовых конъюнкторов даёт наиболее простой по структуре дешифратор, называемый линейным. Дешифраторы часто имеют разрешающий (управляющий) вход Е (от enable – давать возможность). При Е = 1 дешифратор работает как обычно, при Е = 0 на всех выходах устанавливаются неактивные уровни, независимо от поступившего кода адреса. На рис. 2.2 приведено условное изображение дешифраторов (декодеров) на схемах электрических принципиальных.

Рис. 2.2 Дешифратор 2 – 4

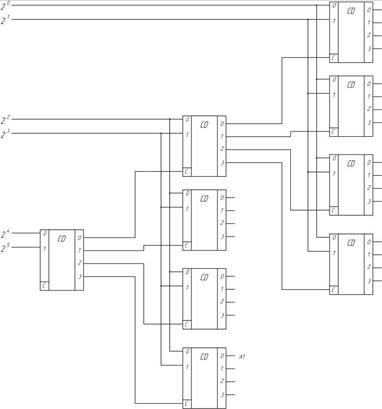

Разработано несколько схем организации структуры и наращивания разрядности дешифраторов: линейная, пирамидальная, матричная, прямоугольная, каскадная, различающиеся аппаратными затратами и временем задержки установления дешифрации входного кода. Для примера, на рис. 2.3 показана схема каскадного соединения дешифраторов вида 2-4 из которых образован дешифратор вида 6-64.

Рис. 2.3 Каскадное соединение дешифраторов

Дешифраторы широко применяются для обслуживания всевозможных средств отображения информации, например, линейных, матричных и 7-сегментных знакосинтезирующих индикаторов различного принципа действия (газоразрядных, электролюминисцентных, светодиодных, жидкокристаллических).

Шифратор

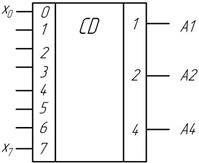

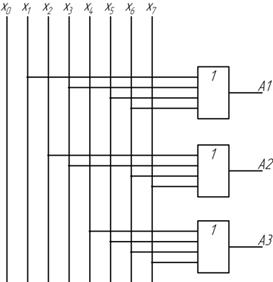

Шифраторы предназначены для преобразования десятичного кода в двоичный. Условное обозначение и схема простейшего шифратора, имеющего восемь входов и три выхода, показан на рис. 2.4.

а в

Рис. 2.4 Условное обозначение (а) и функциональная схема шифратора (в)

При подаче сигнала (лог. 1) на один из входов Х0 – Х7, на его выходах А1 – А3 появляется двоичный код номера возбужденного выхода в соответствии с таблицей соответствия между десятичными и двоичными числами (табл. 2.1).

Поскольку вход Х0 никуда не подключен, схема не различает две ситуации:

а – «подан сигнал на вход Х0»

в – «не подано ни одного сигнала вообще»

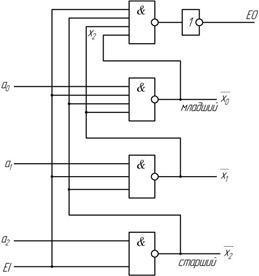

Кроме того, жесткие ограничения накладываются на количество входных сигналов – не более одной единицы и семь нулей, а это означает, что шифратор может преобразовывать только единичный код. Гораздо чаще применяется т.н. унитарный код, представляющий собой неразрывную цепочку из некоторого количества нулей и единиц, поэтому в реальных шифраторах применяют схему выделения старшей единицы (рис. 2.5).

Рис. 2.5 Блок выделения старшей единицы

Эта схема работает так: все старшие нули и самая старшая единица входного кода пропускается на выход без изменения; все разряды, более младшие, чем старшая единица, заменяется нулями.

При EI = 1 любое число старших нулей порождает на выходах своих разрядов 1 и никак не влияет на работу элементов И-НЕ более младших разрядов. Любая самая старшая 1 порождает на соответствующем выходе 0. При этом низкий уровень появится и на ЕО – выходе разрешения.

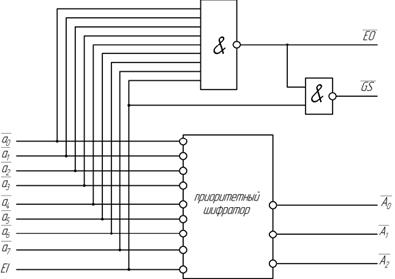

Если к выходу схемы выделения старшей единицы подключить шифратор, то получится приоритетный шифратор, формирующий в двоичном коде номер самой старшей 1 из всех, присутствующих во входном слове. Типичным представителем является К155ИВ1 (рис. 2.6).

Рис. 2.6 Структура приоритетного шифратора К155 ИВ1

EI – разрешение входа

ЕО – разрешение выхода

GS – групповой сигнал

входной унитарный код

входной унитарный код

двоичный выходной код

двоичный выходной код

ЕО отражает ситуацию - в данной группе нет ни одной единицы.

GS отражает ситуацию - в группе есть хотя бы одна единица.

Сигнал EI=0 запирает не только выходы адреса  но и выходы ЕО и GS.

но и выходы ЕО и GS.

Дата добавления: 2017-05-02; просмотров: 4938;