VI. КОМБИНАЦИОННЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

ТИПОВЫЕ КЦУ.

В цифровой технике при построении сложных устройств широко применяются не только отдельные логические элементы, реализующие элементарные булевы функции, но и их комбинации в виде типовых структур, выполняемых как единое целое в виде интегральных микросхем. На входы таких структур могут подаваться информационные логические сигналы и сигналы управления. Последние могут определять, например, порядок передачи информационных входных сигналов на выход или играть роль сигналов синхронизации. Во многих случаях, особенно при использовании в устройствах выходных цепей с тремя состояниями, в качестве сигналов синхронизации выступают сигналы «Выбор микросхемы» (CS). Наличие активного значения такого сигнала управления (в одних схемах это логический нуль, в других — логическая единица) разрешает устройству выполнение заданных функций, отсутствие его переводит схему в «невыбранное» состояние, при котором она не выполняет обработку информации, а ее выходы отключены от нагрузки. Рассмотрим типовые КЦУ.

ШИФРАТОРЫ

Шифратор (называемый также кодером) — устройство, осуществляющее преобразование десятичных чисел в двоичную систему счисления. Пусть в шифраторе имеется m входов, последовательно пронумерованных десятичными числами (0, 1, 2, 3, ... ..., m — 1), и n выходов. Подача сигнала на один из входов приводит к появлению на выходах n-разрядного двоичного числа, соответствующего номеру возбужденного входа.

Очевидно, трудно строить шифраторы с очень большим числом входов т, поэтому они используются для преобразования в двоичную систему счисления относительно небольших десятичных чисел.

Шифраторы широко используются в разнообразных устройствах ввода информации в цифровые системы. Такие устройства могут снабжаться клавиатурой, каждая клавиша которой связана с определенным входом шифратора. При нажатии выбранной клавиши подается сигнал на определенный вход шифратора, и на его выходе возникав двоичное число, соответствующее выгравированному на клавише символу.

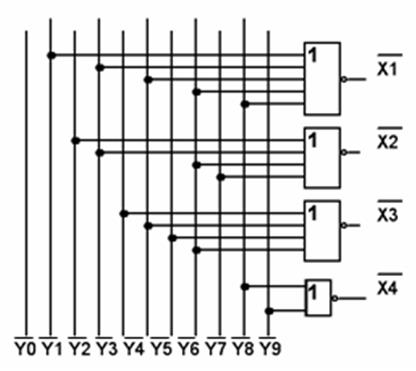

Рис. 22.

На рис. 22 приведено символическое изображение шифратора, преобразующего десятичные числа 0, 1, 2, ..., 9 в двоичную. Символ CD образован из букв, входящих в английское слово CODER. Слева показано 10 входов, обозначенных десятичными цифрами 0, 1, ..., 9. Справа показаны выходы шифратора: цифрами 1, 2, 4, 8 обозначены весовые коэффициенты двоичных разрядов, соответствующих отдельным выходам.

Из приведенной таблицы истинности (табл. 3) следует, что переменная х1 на выходной шине 1 имеет уровень лог. 1, если возбуждается один из нечетных входов.

Таблица 3

| Номер возб. входа | Выходы | |||

| Х1 | Х2 | Х4 | Х8 | |

Следовательно:

X1 = y1 + y3 + y5 + y7 + y9.

Аналогично для остальных выходов:

x2 = y2 + y3 + y6 +y7 ,

x4 = y4 + y5 + y6 + y7 ,

x8 = y8 + y9 .

Этой системе логических выражений соответствует схема шифратора, реализованная на элементах ИЛИ (рис. 23-а). Аналогичным образом можно реализовать шифратор в другом элементном базисе, например, в базисе И-НЕ (рис. 23-б).

.

.

Рис. 23-а

Рис. 23-б

При выполнении шифратора на элементах И-НЕ должна быть предусмотрена подача на входы инверсных значений, т. е. для получения на выходе двоичного представления некоторой десятичной цифры необходимо на соответствующий вход подать лог. 0, а на остальные входы—лог.1.

Изложенным способом могут быть построены шифраторы, выполняющие преобразование десятичных чисел в двоичное представление с использованием любого двоичного кода.

ДЕШИФРАТОРЫ.

Для обратного преобразования двоичных чисел в небольшие по значению десятичные числа используются дешифраторы (называемые также декодерами). Входы дешифратора предназначаются для подачи двоичных чисел, выходы последовательно нумеруются десятичными числами. При подаче на входы двоичного числа появляется сигнал на определенном выходе, номер которого соответствует входному числу.

Дешифраторы имеют широкое применение. В частности, они используются в устройствах, печатающих на бумаге выводимые из цифрового устройства числа или текст. В таких устройствах двоичное число, поступая на вход дешифратора, вызывает появление сигнала на определенном его выходе. С помощью этого сигнала производится печать символа, соответствующего входному двоичному числу.

На рис. 24, а приведено символическое изображение дешифратора. Символ DC образован из букв английского слова DECODER. Слева показаны входы, на которых отмечены весовые коэффициенты двоичного кода. Справа — выходы, пронумерованные десятичными числами, соответствующими отдельным комбинациям входного двоичного кода. На каждом выходе образуется уровень лог. 1 при строго определенной комбинации входного кода.

Дешифратор может иметь парафазные входы для подачи наряду с прямыми входными переменными и их инверсий, как показано на рис. 24,б.

По способу построения различают линейные и прямоугольные дешифраторы.

|  |

а) б)

Рис. 24.

МУЛЬТИПЛЕКСОРЫ

Мультиплексор является устройством, которое осуществляет коммутацию одного из нескольких информационных входных сигналов на выход в соответствии с заданным кодом на входах управления. Мультиплексор имеет несколько информационных входов (D0, D1,...),, входы управления(A0, A1, ...) и один выход Q. На рис. 25, а показано символическое изображение типичного мультиплексора с четырьмя информационными входами и входом синхронизации С.

Рис. 25.

а)

б)

Рис. 25.

Каждому информационному входу мультиплексора присваивается номер, называемый адресом. При подаче сигнала на вход С мультиплексор выбирает один из входов, адрес которого задается двоичным кодом на входах управления, и подключает его к выходу.

Таким образом, подавая на адресные входы адреса различных информационных входов, можно передавать цифровые сигналы с этих входов на выход Q.

Таблица 4.

| Входы управления | Выход | |

| A1 | A2 | Q |

| D0 | ||

| D1 | ||

| D2 | ||

| D3 |

Функционирование мультиплексора определяется табл. 4 (при С=1).. При отсутствии стробирующего сигнала (С=0) связь между информационными входами и выходом отсутствует (Q=0). При подаче стробирующего сигнала (С=1) на выход передается логический уровень того из информационных входов Di, номер которого i в двоичной форме задан на адресных входах.

Принципиальная схема мультиплексора показана на рис. 25, б.

В тех случаях, когда требуется передавать на выходы многоразрядные входные данные в параллельной форме, используется параллельное включение мультиплексоров по числу разрядов передаваемых данных.

ДЕМУЛЬТИПЛЕКСОРЫ.

Демультиплексор имеет один информационный вход и несколько выходов. Он представляет собой устройство, которое осуществляет коммутацию информационного входного сигнала на один из выходов, имеющему адрес (номер), задаваемый на входах управления. На рис. 26 показано символическое изображение демультиплексора с четырьмя выходами. Функционирование этого демультиплексора определяется табл. 5.

Рис. 26.

Таблица 5

| Входы управления | Выходы | ||||

| X1 | X2 | Y0 | Y1 | Y2 | Y3 |

| D | |||||

| D | |||||

| D | |||||

| D |

Структурные формулы, определяющие формирование выходных сигналов такого демультиплексора, имеют вид:

y0 = x1 * x2 * D, y2 = x1 * x2 * D ,

y0 = x1 * x2 * D, y0 = x1 * x2 * D .

; ;

; .

Использование демультиплексора может существенно упростить построение логического устройства, имеющего несколько выходов, на которых формируются различные логические функции одних и тех же переменных.

ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР.

Из рассмотренного ранее принципа сложения многоразрядных двоичных чисел следует, что в каждом из разрядов производятся однотипные действия: определяется цифра суммы путем сложения по модулю 2 цифр слагаемых и поступающего в данный разряд переноса и формируется перенос, передаваемый в следующий разряд. Эти действия реализуются одноразрядным двоичным сумматором. Символическое изображение такого сумматора показано на рис. 27, а. Он имеет три входа для подачи цифр разрядов слагаемых ai , bi и переноса рi ; на выходах формируются сумма si, и перенос pi + 1 ,i предназначенный для передачи в следующий разряд.

Рис. 27.

В одноразрядном сумматоре могут предусматриваться входы для подачи как прямых значений разрядов слагаемых ai , bi и переноса рi, так и инверсных значений, а также выходы, на которых формируются инверсные значения выходных переменных.

В таблице 6 показан закон функционирования одноразрядного сумматора.

Таблица 6.

| Входы | Выходы | |||

| Слагаемые | Перенос | Сумма | Перенос | |

| ai | bi | рi | si | рi+1 |

МНОГОРАЗРЯДНЫЕ ДВОИЧНЫЕ СУММАТОРЫ.

В зависимости от способа ввода разрядов слагаемых сумматоры делятся на два типа: последовательного и параллельного действия. В сумматоры первого типа разряды чисел вводятся в последовательной форме, т. е. разряд за разрядом (младшим разрядом вперед), в сумматоры второго типа каждое из слагаемых подается в параллельной форме, т. е. одновременно всеми разрядами.

Сумматор последовательного действия. Состоит из одноразрядного

сумматора, выход pi+1 которого соединен с входом pi через элемент задержки, параметры которого согласованы со скоростью поступления разрядов слагаемых на входы сумматора. Операция суммирования во всех разрядах слагаемых осуществляется с помощью одного и того же одноразрядного сумматора, но последовательно во времени, начиная с младших разрядов. Такое построение сумматора возможно за счет того, что слагаемые поступают в последовательной форме.

Очевидное достоинство сумматора последовательного действия заключается в малом объеме оборудования, требуемого для его построения. Однако связанная с этим необходимость в последовательной обработке разрядов приводит к крайне низкому быстродействию. Поэтому , сумматоры такого типа в настоящее время используются очень редко.

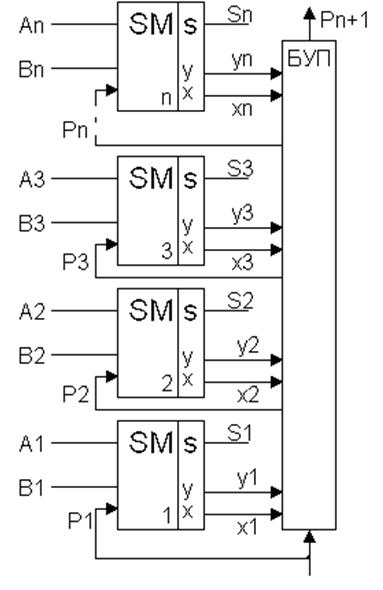

Сумматор параллельного действия. Состоит из отдельных разрядов, каждый из которых содержит одноразрядный сумматор (рис. 28).

При подаче слагаемых цифры их разрядов поступают на соответствующие одноразрядные сумматоры. Каждый из одноразрядных сумматоров формирует на своих выходах цифру соответствующего разряда суммы и перенос, передаваемый на вход одноразрядного сумматора следующего (более старшего) разряда.

Такая организация процесса организации переноса, называемая последовательным переносом, снижает быстродействие многоразрядных сумматоров, т.к. получение результата в старшем разряде сумматора обеспечивается только после завершения распространения переноса по всем разрядам.

Рис. 28.

Повышение быстродействия параллельных сумматоров. Для обеспечения высокого быстродействия параллельные сумматоры должны строиться на элементах, обладающих высоким быстродействием.

В наиболее неблагоприятном случае возникший в младшем разряде перенос может последовательно вызывать переносы во всех остальных разрядах. При этом время передачи переносов t = t1 * n, где t1 —задержка распространения переноса в одном разряде.

Уменьшение t достигается следующими приемами.

1. При построении схем одноразрядных сумматоров стремятся к уменьшению числа элементов в цепи между входом, на который поступает импульс переноса рi и .выходом, на котором формируется передаваемый в следующий разряд импульс переноса pi+i.

2. В цепях от pi к pi+1 применяют элементы с повышенным быстродействием.

3. Схемы сумматоров следует строить таким образом, чтобы сигналы с выхода каждого логического элемента в цепи от рi, к pi+i поступали на возможно меньшее число других логических элементов, так как присоединение каждого дополнительного элемента к той или иной точке цепи переносов, как правило, приводит к увеличению паразитной емкости, удлинению фронтов сигналов и, следовательно, к увеличению задержки распространения сигнала и снижению быстродействия сумматора.

4. Применяют устройства формирования переносов в параллельной форме. В показанном на рис. 29 сумматоре с помощью устройства, называемого блоком ускоренного переноса, производится формирование переносов в параллельной форме, т. е. одновременно для всех разрядов. Переносы из этого блока поступают во все разрядные сумматоры одновременно. При этом разрядные сумматоры не содержат цепей формирования переносов, они формируют только сумму Si и величины Yi и Xi, для получения которых переносы не требуются. Эти величины Yi и Xi необходимы для формирования переносов в блоке ускоренного переноса, они определяют следующие ситуации: Yi=1 означает, что в i-м разряде перенос pi+1 в следующий (p+1)-й разряд необходимо формировать независимо от поступления в данный разряд переноса из предыдущего разряда; Xi=1 означает, что в i-м разряде перенос рi+i должен формироваться только при условии поступления переноса рi, из предыдущего разряда:

Yi = a1 * b1; X1 = (a1 + b1) * p1.

Рис. 29.

Величины Yi и Xi формируются одновременно во всех разрядных сумматорах, одновременно поступают на входы блока ускоренного переноса и, следовательно, в этом блоке одновременно формируются переносы, подаваемые в разрядные сумматоры. После поступления переносов из блока ускоренного переноса в разрядных сумматорах формируются суммы Si.

БЫСТРОДЕЙСТВИЕ КЦУ.

Так как логические элементы, входящие в состав КЦУ, переключаются с задержкой tзад., то при изменении в некоторый момент времени комбинации входных сигналов выходные сигналы устройства (если они изменяются в результате этого) примут установившиеся значения только после того, как закончатся переходные процессы в соответствующих логических элементах. На пути от входов устройства к его выходам отдельные логические элементы включены последовательно. Поэтому длительность переходных процессов будет зависеть от числа логических элементов, которые включены в такой цепочке. Применяемая в настоящее время методика определения tзад в логических элементах, предусматривающая использование при измерении цепочки включенных друг за другом однотипных логических элементов, позволяет при оценке общей задержки в такой цепочке суммировать задержки отдельных логических элементов. При оценке быстродействия КЦУ необходимо выявить ту цепочку логических элементов между входами и выходами устройства, которая будет задавать наибольшую задержку, и сложить между собой задержки логических элементов этой цепочки. Обычно она содержит наибольшее число включенных друг за другом от входов до выходов логических элементов. Но могут быть исключения, связанные, например, с наличием в более короткой цепочке отдельных инерционных логических элементов с большим tзад. Поэтому в общем случае необходимо проанализировать все цепочки логических элементов от входов до выходов и выявить такую, которая дает наибольшую задержку.

СОСТЯЗАНИЯ В КЦУ.

Неодинаковую задержку прохождения сигнала в отдельных частях КЦУ иногда ассоциируют с «состязаниями» в скорости переключения логических элементов. В результате этого явления на выходах некоторых элементов могут появляться импульсные помехи. В некоторых случаях неодинаковая задержка прохождения сигнала в отдельных цепочках логических элементов может привести к импульсной помехе и на выходе КЦУ. Покажем это на примере.

Рассмотрим КЦУ представленную на рис. 30, а. Входной сигнал изменяется с кода 1000 на код 1111. Задержка в каждом логическом элементе tзад. Структурная схема КЦУ и временные диаграммы для данного примера приведены на рис. 30, б. В данном случае на выходе КЦУ при изменении кода входного сигнала 1000 на код 1111 кратковременно устанавливается нулевое значение (на время 3 * tздр), хотя по условиям работы выходное значение должно было сохраниться на единичном уровне.

Это непосредственно вытекает из временных диаграмм, если пренебречь задержками переключения логических элементов Когда длительность помехи превысит определенную величину, возможно нарушение работоспособности подключенных к выходу КЦУ устройств (триггеров, счетчиков и т. д.). В подобных случаях «состязания» называют «опасными».

а) б)

Рис. 30.

Для борьбы с «опасными состязаниями» можно принять различные меры. Во-первых, иногда можно предусмотреть такой порядок смены входных кодов, при котором либо импульсные помехи не будут появляться на выходе вообще, либо их длительность уменьшится до безопасной величины. В необходимых случаях такую задержку можно ввести искусственно включением цепочки из четного числа инверторов. Во-вторых, при синтезе соответствующего КЦУ можно иногда найти такой вариант структурной формулы (а следовательно, и структурной схемы), при котором удается уменьшить величину импульсной помехи.

В подобных случаях «состязания» называют «опасными». Для борьбы с «опасными состязаниями» можно принять различные меры. Во-первых, иногда можно предусмотреть такой порядок смены входных кодов, при котором либо импульсные помехи не будут появляться на выходе вообще, либо их длительность уменьшится до безопасной величины. В необходимых случаях такую задержку можно ввести искусственно включением цепочки из четного числа инверторов. Во-вторых, при синтезе соответствующего КЦУ можно иногда найти такой вариант структурной формулы (а следовательно, и структурной схемы), при котором удается уменьшить величину импульсной помехи.

В-третьих, можно организовать синхронную передачу сигналов от одного устройства к другому. Для этого вводятся специальные импульсы синхронизации, которые задают моменты передачи информации между отдельными устройствами. Пауза между импульсами синхронизации может быть выбрана такой, чтобы за ее время закончились переходные процессы и на выходах устройств установились стационарные значения.

Синхронная передача информации в современных цифровых устройствах применяется очень широко. Этот вопрос уже обсуждался ранее, например при рассмотрении типовых КЦУ, в том числе мультиплексоров. Отметим, что наличие «состязаний» и возникающие при этом импульсные помехи влияют на надежность цифровых устройств.

Дата добавления: 2016-05-31; просмотров: 2878;