Сдвигающие регистры (shift register)

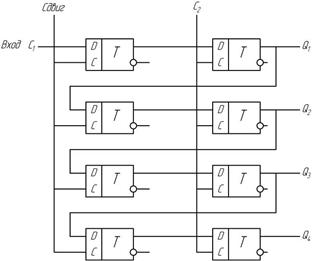

Это регистр, содержимое которого при подаче управляющего сигнала «Сдвиг» может сдвигаться в сторону старших или младших разрядов. На рис. 3.36 приведена схема однонаправленного сдвигового регистра, выполненного на «прозрачных» триггерах-защелках.

Рис. 3.36. Сдвиговый регистр на «прозрачных» защелках

Когда на вход С1 или С2 поступает активный уровень импульса, выход каждого триггера принимает состояние своего младшего соседа и таким образом, информация, содержащаяся в регистре сдвигается на один разряд в сторону старших разрядов, влево.

Недостатком такой структуры является обязательная двухфазная синхронизация триггеров, иначе, если  , то входные данные успеют перейти через сколько-то триггеров, поэтому должно выполняться условие

, то входные данные успеют перейти через сколько-то триггеров, поэтому должно выполняться условие  .

.

Эту схему можно выполнить на прозрачных триггерах типа 155ТМ5, К155ТМ7.

Применение «непрозрачных» триггеров существенно упрощает схему регистра. Регистр состоит из цепочки «непрозрачных» триггеров, тактовые входы которых объединены, а D-вход (кроме самого младшего) подключен к выходу соседнего младшего триггера (рис. 3.37).

Когда на  вход поступает активный отрицательный фронт «Сдвиг», выход каждого триггера принимает состояние своего младшего соседа и, таким образом, информация, содержащаяся в регистре, сдвигается на один разряд в сторону старших разрядов, влево.

вход поступает активный отрицательный фронт «Сдвиг», выход каждого триггера принимает состояние своего младшего соседа и, таким образом, информация, содержащаяся в регистре, сдвигается на один разряд в сторону старших разрядов, влево.

Рис. 3.37. Сдвиговый регистр на «непрозрачных» триггерах

Подобную структуру имеет регистр К561ИР2, условное обозначение которого приведено на рис. 3.38.

Рис. 3.38 Регистр К561 ИР2

Как видно из УГО этой микросхемы, в одном корпусе имеется два независимых регистра, каждый из которых дополнен входом R-предварительной очистки.

Наращивание однонаправленных регистров простое – достаточно вход D0 каждого последующего регистра соединить с выходом старшего разряда Q3 предыдущего, а тактовые входы и входы сброса (если они имеются) объединить (рис. 3.39).

Рис. 3.39. Схема наращивания однонаправленных регистров

Двунаправленный регистр сдвига (bidirectional register)

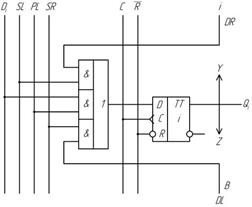

На рис. 3.40 приведена схема ячейки регистра, способного сдвигать данные как в сторону старших, так и в сторону младших разрядов, т.е. ячейка двунаправленного регистра сдвига.

Рис. 3.40. Ячейка двунаправленного сдвигового регистра

Конечно, по сути это всё тот же «непрозрачный» триггер, информационный вход которого соединен с выходом трехвходового мультиплексора, управляя которым можно подавать на вход триггера информацию от старших, младших триггеров этого регистра или вносить независимую внешнюю информацию.

Ознакомимся с назначением входов этого регистра:

DR – вход, принимающий данные, вдвигаемые в регистр со стороны младшего разряда справа (data right)

DL– вход со стороны старшего разряда слева (data left)

SL – сдвиг влево (shift left)

SR – сдвиг вправо (shift right)

PL – параллельная загрузка (parallel load)

С – тактовый сигнал, по которому происходит сдвиг

Di – входы параллельной загрузки информации

R̅ - очистка триггера (как правило, обладает приоритетом по отношению к другим сигналам)

Выход каждого  -го триггера подключен к входам мультиплексоров соседних разрядов (направления Y и

-го триггера подключен к входам мультиплексоров соседних разрядов (направления Y и  ).

).

По  сигналам триггеры регистра принимают информацию с направлений, диктуемых мультиплексорами.

сигналам триггеры регистра принимают информацию с направлений, диктуемых мультиплексорами.

Зачастую управляющие входы SL, SR, PL не выводят из корпуса, а управляют ими через небольшой дешифратор режимов, как сделано, например, в регистре К155ИР13 (рис. 3.41). В условном обозначении двунаправленный регистр маркируется двунаправленной стрелкой.

Зачастую управляющие входы SL, SR, PL не выводят из корпуса, а управляют ими через небольшой дешифратор режимов, как сделано, например, в регистре К155ИР13 (рис. 3.41). В условном обозначении двунаправленный регистр маркируется двунаправленной стрелкой.

Рис. 3.41. УГО двунаправленного регистра К155ИР13

Описание поведения такого сложного устройства дает табл. 3.8 в которой перечислены пять режимов, в которых может находиться этот регистр.

Таблица 3.8

Состояния микросхемы К155ИР13

| входы | выходы | Режим работы | ||||||

| R | C | S1 | S0 | DR | DL | Di | Q1 Q2 . . . Q7 Q8 | |

| ↑ | Х | Din | D1n D2n . . . D7n D8n | Параллельный ввод | ||||

| ↑ | Х | Х | x | Q1n Q2n . . . Q7n Q8n | Хранение | |||

| ↑ | Х | x | Q2n Q3n . . . Q8n 0 | Сдвиг влево | ||||

| ↑ | Х | X | Q2n Q3n . . . Q8n 1 | |||||

| ↑ | Х | X | 0 Q1n. . . Q6n Q7n | Сдвиг вправо | ||||

| ↑ | Х | X | 1 Q1n. . . Q6n Q7n | |||||

| х | х | х | х | Х | X | 0 0 . . . 0 0 | Сброс |

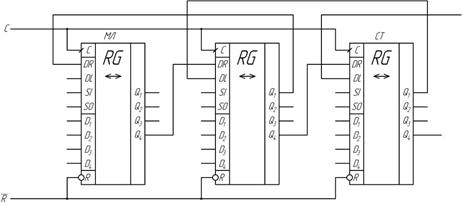

Наращивание двунаправленных регистров может быть осуществлено по схеме, показанной на рис. 3.42.

Рис. 3.42. Схема наращивания двунаправленного регистра

Дата добавления: 2017-05-02; просмотров: 3872;