Регистры и организация памяти.

2.1.Регистры

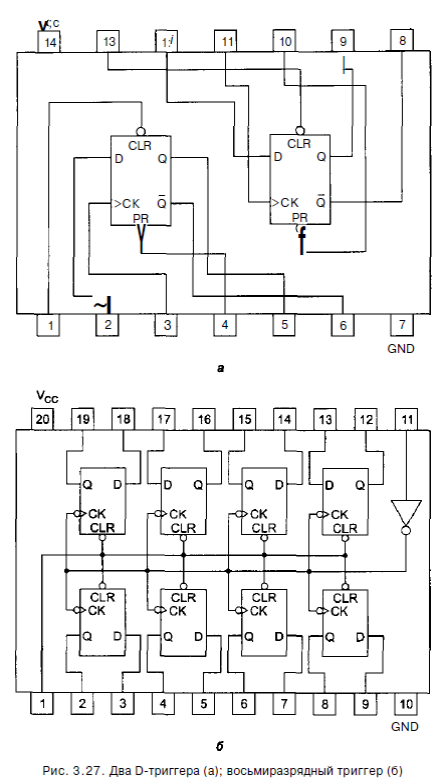

Существуют различные конфигурации триггеров. На рисунке 3.27, а изображена схема, содержащая два независимых D-триггера с сигналами предварительной установки и очистки. Хотя эти два триггера находятся на одной микросхеме с 14 выводами, они не связаны между собой. Совершенно по-другому устроен восьмиразрядный триггер, изображенный на рис. 3.27, б. Здесь, в отличие от предыдущей схемы, у восьми триггеров нет выхода (J и линий предварительной установки и все синхронизирующие линии связаны вместе и управляются выводом 11. Сами триггеры того же типа, что на рис. 3.26, г, но инвертирующие входы аннулируются инвертором, связанным с выводом 11, поэтому триггеры запускаются при переходе от 0 к 1. Все восемь сигналов очистки также объединены, поэтому когда вывод 1 переходит в состояние 0, все триггеры также переходят в состояние 0. Если вам не понятно, почему вывод 11 инвертируется на входе, а затем инвертируется снова при каждом сигнале СК, то ответ прост: входной сигнал не имеет достаточной мощности, чтобы запустить все восемь триггеров; входной инвертор на самом деле используется в качестве усилителя.

Одна из причин объединения линий синхронизации и линий очистки в микросхеме на рис. 3.27, б ~ экономия выводов. С другой стороны, микросхема данной конфигурации несколько отличается от восьми несвязанных триггеров. Эта микросхема используется в качестве одного 8-разрядного регистра. Две такие микросхемы могут работать параллельно, образуя 16-разрядный регистр. Для этого нужно связать соответствующие выводы 1 и 11. Регистры и их применение мы рассмотрим более подробно в главе 4.

2.2.Организация памяти

Хотя мы и совершили переход от простой памяти в 1 бит (см. рис. 3.23) к 8-разрядной памяти (см. рис. 3.27, б), чтобы построить память большого объема, требуется другой способ организации, при котором можно обращаться к отдельным словам.

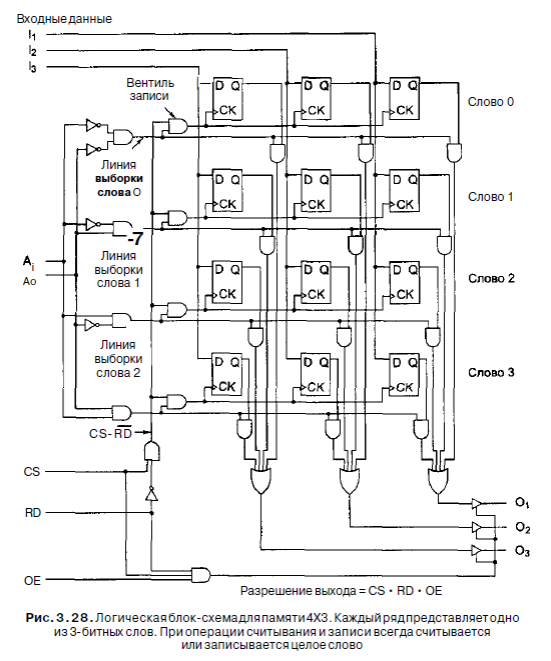

Пример организации памяти, которая удовлетворяет этому критерию, показан на рис. 3.28. Эта память содержит четыре 3-битных слова. Каждая операция считывает или записывает целое 3-битное слово. Хотя общий объем памяти (12 битов) не намного больше, чем у нашего 8-разрядного триггера, такая память требует меньшего количества выводов, и, что особенно важно, подобная организация применима при построении памяти большого объема.

Хотя структура памяти, изображенная на рис. 3.28, может на первый взгляд показаться сложной, на самом деле она очень проста благодаря своей регулярной структуре. Она содержит 8 входных линий (3 входа для данных - 10, Ь и 12; 2 входа для адресов - Ао и А,; 3 входа для управления - CS (Chip Select - выбор элемента памяти), RD (для различия между считыванием и записью) и ОЕ (Output Enable - разрешение выдачи выходных сигналов)) и 3 выходные линии для данных - Оо, Ot и Ог- Такую память в принципе можно поместить в корпус с 14 выводами (включая питание и «землю»), а 8-разрядный триггер требует наличия 20 выводов.

Чтобы выбрать микросхему памяти, внешняя логика должна установить CS на 1, а также установить RD на 1 для чтения и на 0 для записи. Две адресные линии должны указывать, какое из четырех 3-битных слов нужно считывать или записывать. При операции считывания входные линии для данных не используются. Выбирается слово и помещается на выходные линии для данных. При операции записи биты, находящиеся на входных линиях для данных, загружаются в выбранное слово памяти; выходные линии при этом не используются. А теперь давайте посмотрим, как работает память, изображенная на рис. 3.28. Четыре вентиля И для выбора слов в левой части схемы формируют декодер. Входные инверторы расположены так, что каждый вентиль запускается определенным адресом. Каждый вентиль приводит в действие линию выбора слов (для слов 0, 1, 2 и 3). Когда микросхема должна производить запись, вертикальная линия CS • 1Ш

получает значение 1, запуская один из 4 вентилей записи. Выбор вентиля зависит от того, какая именно линия выбора слов равна 1. Выходной сигнал вентиля записи приводит в действие все сигналы СК для выбранного слова, загружая входные данные в триггеры для этого слова. Запись производится только в том случае, если CS равно 1, a RD равно 0, при этом записывается только слово, выбранное адресами Ао и Аь остальные слова не меняются.

Процесс считывания сходен с процессом записи. Декодирование адреса происходит точно так же, как и при записи. Но в данном случае линия CS • RD принимает значение 0, поэтому все вентили записи блокируются и ни один из триггеров не меняется. Вместо этого линия выбора слов запускает вентили И, связанные с битами Q выбранного слова Таким образом, выбранное слово передает свои данные в четырехвходовые вентили ИЛИ, расположенные в нижней части схемы, а остальные три слова выдают 0. Следовательно, выход вентилей ИЛИ идентичен значению, сохраненному в данном слове. Остальные три слова никак не влияют на выходные данные.

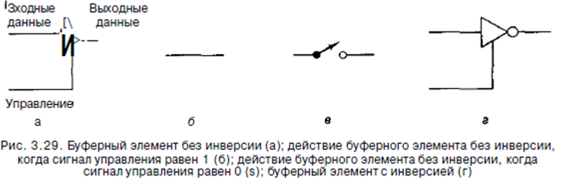

Мы могли бы разработать схему, в которой три вентиля ИЛИ соединялись бы с тремя линиями вывода данных, но это вызвало бы некоторые проблемы. Мы рассматривали линии ввода данных и линии вывода данных как разные линии. На практике же используются одни и те же линии. Если бы мы связали вентили ИЛИ с линиями вывода данных, микросхема пыталась бы выводить данные (то есть задавать каждой линии определенную величину) даже в процессе записи, мешая нормальному вводу данных. По этой причине желательно каким-то образом соединять вентили ИЛИ с линиями вывода данных при считывании и полностью разъединять их при записи. Все, что нам нужно, - электронный переключатель, который может устанавливать и разрушать связь за несколько наносекунд. К счастью, такие переключатели существуют На рис. 3 29, а показано символическое изображение так называемого буферного элемента без инверсии. Он содержит вход для данных, выход для данных и вход управления. Когда вход управления равен 1, буферный элемент работает как провод (см. рис. 3.29, б).

Когда вход управления равен 0, буферный элемент работает как разомкнутая цепь (см рис. 3.29, б), как будто кто-то отрезал выход для данных от остальной части схемы кусачками. Соединение может быть восстановлено за несколько наносекунд, если сделать сигнал управления равным 1.

На рис. 3.29, г показан буферный элемент с инверсией, который действует

как обычный инвертор, когда сигнал управления равен 1, и отделяет выход от остальной части схемы, когда сигнал управления равен 0. Оба буферных элемента представляют собой устройства с тремя состояниями, поскольку они могут выдавать 0,1 или вообще не выдавать сигнала (в случае с разомкнутой цепью). Буферные элементы, кроме того, усиливают сигналы, поэтому они могут справляться с большим количеством сигналов одновременно. Иногда они используются в схемах именно по этой причине, даже если их свойства переключателя не нужны.

Сейчас уже должно быть понятно, для чего нужны три буферных элемента без инверсии на линиях вывода данных. Когда CS, RD и ОЕ все равны 1, то сигнал разрешения выдачи выходных данных также равен 1, в результате чего запускаются буферные элементы и слово помещается на выходные линии. Когда один из сигналов CS, RD и ОЕ равен 0, выходы отсоединяются от остальной части схемы.

Дата добавления: 2016-10-26; просмотров: 3152;