Шины и принципы их работы.

2.1.Шины

Шина - это группа проводников, соединяющих различные устройства. Шины

можно разделить на группы в соответствии с выполняемыми функциями. Они могут быть внутренними по отношению к процессору и служить для передачи данных в АЛУ и из АЛУ, а могут быть внешними по отношению к процессору и связывать процессор с памятью или устройствами ввода-вывода. Каждый тип шины обладает определенными свойствами, и к каждому из них предъявляются определенные требования. В этом и следующих разделах мы сосредоточимся на шинах, которые связывают центральный процессор с памятью и устройствами ввода-вывода. В следующей главе мы подробно рассмотрим внутренние шины процессора.

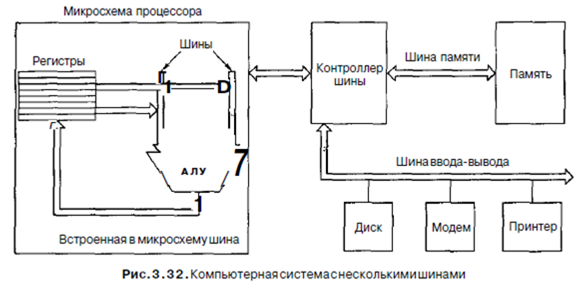

Первые персональные компьютеры имели одну внешнюю шину, которая называлась системной шиной. Она состояла из нескольких медных проводов (от 50 до 100), которые встраивались в материнскую плату. На материнской плате находились разъемы на одинаковых расстояниях друг от друга для микросхем памяти и устройств ввода-вывода. Современные персональные компьютеры обычно содержат специальную шину между центральным процессором и памятью и по крайней мере еще одну шину для устройств ввода-вывода. На рис. 3.32 изображена система с одной шиной памяти и одной шиной ввода-вывода.

В литературе шины обычно изображаются в виде жирных стрелок, как показано на этом рисунке. Разница между жирной и нежирной стрелкой небольшая. Когда все биты одного типа, например адресные или информационные, рисуется обычная стрелка. Когда включаются адресные линии, линии данных и управления, используется жирная стрелка.

Хотя разработчики процессоров могут использовать любой тип шины для микросхемы, должны быть введены четкие правила о том, как работает шина, и все устройства, связанные с шиной, должны подчиняться этим правилам, чтобы платы, которые выпускаются третьими лицами, подходили к системной шине. Эти правила называются протоколом шины. Кроме того, должны существовать определенные технические требования, чтобы платы от третьих производителей подходили к каркасу для печатных плат и имели разъемы, соответствующие материнской плате механически и с точки зрения мощностей, синхронизации и т. д.

Существует ряд широко используемых в компьютерном мире шин. Приведем

несколько примеров: Omnibus (PDP-8), Unibus (PDP-11), IBM PC (PC/XT), ISA (PC/AT), EISA (80386), MicroChannel (PC/2), PCI (различные персональные компьютеры), SCSI (различные персональные компьютеры и рабочие станции), Nubus (Macintosh), Universal Serial Bus (современные персональные компьютеры), FireWire (бытовая электроника), VME (оборудование в кабинетах физики) и Сагаас (физика высоких энергий). Может быть, все стало бы намного проще, если бы все шины, кроме одной, исчезли с поверхности Земли (или кроме двух). К сожалению, стандартизация в этой области кажется маловероятной, и уже вложено слишком много средств во все эти несовместимые системы.

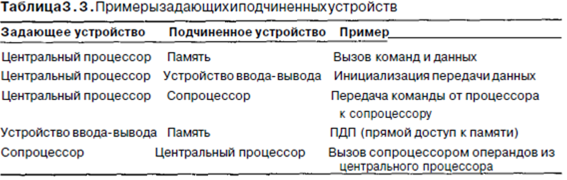

Давайте начнем с того, как работают шины. Некоторые устройства, связанные с шиной, являются активными и могут инициировать передачу информации по шине, тогда как другие являются пассивными и ждут запросов. Активное устройство называется задающим устройством, пассивное - подчиненным устройством.

Когда центральный процессор требует от контроллера диска считать или записать блок информации, центральный процессор действует как задающее устройство, а контроллер диска - как подчиненное устройство. Контроллер диска может действовать как задающее устройство, когда он командует памяти принять слова, которые считал с диска. Несколько типичных комбинаций задающего и подчиненного устройств указаны в табл. 3.3. Память ни при каких обстоятельствах не может быть задающим устройством.

Двоичные сигналы, которые выдают устройства компьютера, часто недостаточно интенсивны, чтобы активизировать шину, особенно если она достаточно длинная и если к ней подсоединено много устройств. По этой причине большинство задающих устройств шины обычно связаны с ней через микросхему, которая называется драйвером шины, по существу являющуюся двоичным усилителем.

Сходным образом большинство подчиненных устройств связаны с шиной приемником шины. Для устройств, которые могут быть и задающим, и подчиненным устройством, используется приемопередатчик шины. Эти микросхемы взаимодействия с шиной часто являются устройствами с тремя состояниями, что дает им возможность отсоединяться, когда они не нужны. Иногда они подключаются через открытый коллектор, что дает сходный эффект. Когда одно или несколько устройств на открытом коллекторе требуют доступа к шине в одно и то же время, результатом является булева операция ИЛИ над всеми этими сигналами. Такое соглашение называется монтажным ИЛИ. В большинстве шин одни линии являются устройствами с тремя состояниями, а другие, которым требуется свойство монтажного ИЛИ, - открытым коллектором.

Как и процессор, шина имеет адресные линии, информационные линии и линии управления. Тем не менее между выводами процессора и сигналами шины может и не быть взаимно однозначного соответствия. Например, некоторые процессоры содержат три вывода, которые выдают сигнал чтения из памяти или записи в память, или чтения устройства ввода-вывода, или записи на устройство ввода-вывода, или какой-либо другой операции. Обычная шина может содержать одну линию для чтения из памяти, вторую линию для записи в память, третью – для чтения устройства ввода-вывода, четвертую - для записи на устройство ввода-вывода и т. д. Микросхема-декодер должна тогда связывать данный процессор с такой шиной, чтобы преобразовывать 3-битный кодированный сигнал в отдельные сигналы, которые могут управлять линиями шины.

Разработка шин и принципы действия шин - это достаточно сложные вопросы и по этому поводу написан ряд книг [128, 135,136]. Принципиальными вопросами в разработке являются ширина шины, синхронизация шины, арбитраж шины и функционирование шины. Все эти параметры существенно влияют на скорость и пропускную способность шины. В следующих четырех разделах мы рассмотрим каждый из них.

2.2.Принципы работы шины

До этого момента мы обсуждали только обычные циклы шины, когда задающее устройство (обычно центральный процессор) считывает информацию из подчиненного устройства (обычно из памяти) или записывает в него информацию. Однако существует еще несколько типов циклов шины. Давайте рассмотрим некоторые из них.

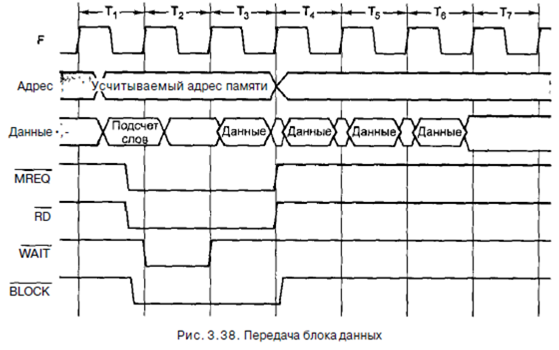

Обычно за раз передается одно слово. При использовании кэш-памяти жела-

тельно сразу вызывать всю строку кэш-памяти (то есть 16 последовательных 32-битных слов). Часто передача блоками может быть более эффективна, чем такая последовательная передача информации. Когда начинается чтение блока, задающее устройство сообщает подчиненному устройству, сколько слов нужно передать (например, помещая общее число слов на информационные линии в период Ti).

Вместо того чтобы выдать в ответ одно слово, задающее устройство выдает одно слово в течение каждого цикла до тех пор, пока не будет передано требуемое количество слов. На рис. 3.38 изображена такая же схема, как и на рис. 3.34, только здесь появился дополнительный сигнал BLOCK, который указывает, что запрашивается передача блока. В данном примере считывание блока из 4 слов занимает 6 циклов вместо 12.

Существуют также другие типы циклов шины. Например, если речь идет о системах с двумя или несколькими центральными процессорами на одной шине, нужно быть уверенным, что в конкретный момент только один центральный процессор может использовать определенную структуру данных в памяти. Чтобы упорядочить этот процесс, в памяти должна содержаться переменная, которая принимает значение 0, когда центральный процессор использует структуру данных, и 1, когда структура данных не используется. Если центральному процессору нужно получить доступ к структуре данных, он должен считать переменную, и если она равна О,

придать ей значение 1. Проблема заключается в том, что два центральных процессора могут считать переменную на последовательных циклах шины. Если каждый процессор видит, что переменная равна 0, а затем каждый процессор меняет значение переменной на 1, как будто только он один использует эту структуру данных, то такая последовательность событий ведет к хаосу.

Чтобы предотвратить такую ситуацию, в многопроцессорных системах предусмотрен специальный цикл шины, который дает возможность любому процессору считать слово из памяти, проверить и изменить его, а затем записать обратно в память; весь этот процесс происходит без освобождения шины. Такой цикл не дает возможности другим центральным процессорам использовать шину и, следовательно, мешать работе первого процессора.

Еще один важный цикл шины - цикл для осуществления прерываний. Когда

центральный процессор командует устройству ввода-вывода произвести какое-то действие, он ожидает прерывания после завершения работы. Для сигнала прерывания нужна шина.

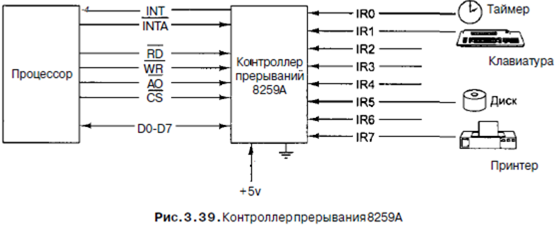

Поскольку может сложиться ситуация, когда несколько устройств одновременно хотят произвести прерывание, здесь имеют место те же проблемы разрешения конфликтных ситуаций, что и в обычных циклах шины. Чтобы избежать таких проблем, нужно каждому устройству приписать определенный приоритет и использовать централизованный арбитр для распределения приоритетов. Существует стандартный контроллер прерываний, который широко используется. В компьютерах IBM PC и последующих моделях применяется микросхема Intel 8259А. Она изображена на рис. 3.39.

До восьми контроллеров ввода-вывода могут быть непосредственно связаны с восемью входами IRx (Interrupt Request - запрос прерывания) микросхемы 8259А. Когда любое из этих устройств хочет произвести прерывание, оно запускает свою линию входа Если активизируется один или несколько входов, контроллер 8259А выдает сигнал INT (INTerrupt - прерывание), который подается на соответствующий вход центрального процессора Когда центральный процессор способен произвести прерывание, он посылает микросхеме 8259А импульс через вывод INTA (INTerrupt Acknowledge - подтверждение прерывания) В этот момент микросхема 8259А должна определить, на какой именно вход поступил сигнал прерывания. Для этого она помещает номер входа на информационную шину. Эта операция

требует наличия особого цикла шины. Центральный процессор использует этот номер для обращения в таблицу указателей, которую называют таблицей векторов прерывания, чтобы найти адрес процедуры, производящей соответствующее прерывание

Микросхема 8259А содержит несколько регистров, которые центральный процессор может считывать и записывать, используя обычные циклы шины и выводы RD (ReaD - чтение), WR (WRite - запись), CS (Chip Select - выбор элемента памяти) и Xfl. Когда программное обеспечение обработало прерывание и готово получить следующее, оно записывает специальный код в один из регистров, который вызывает сброс сигнала INT микросхемой 8259А, если не появляется другая задержка прерывания Регистры также могут записываться для того, чтобы ввести микросхему 8259А в один из нескольких режимов, и для выполнения некоторых других функций

Когда присутствует более восьми устройств ввода-вывода, микросхемы 8259А могут быть соединены каскадно. В самой экстремальной ситуации все восемь входов могут быть связаны с выходами еще восьми микросхем 8259 А, соединяя до 64 устройств ввода-вывода в двухступенчатую систему прерывания Микросхема 8259А содержит несколько выводов для управления каскадированием, но мы их опустили ради простоты.

Хотя мы никоим образом не исчерпали все вопросы разработки шин, материал, изложенный выше, дает достаточно информации для общего понимания принципов работы шины и того, как центральный процессор взаимодействует с шиной А теперь мы перейдем от общего к частному и рассмотрим несколько конкретных примеров процессоров и их шин.

Дата добавления: 2016-10-26; просмотров: 8677;