Поэтому ключ хорошо проводит как аналоговые, так и импульсные сигналы и в прямом и в обратном направлениях. В связи с этим мультиплексоры можно использовать как демультиплексоры.

Микросхема К564КП1 (рисунок 11.6) – двойной четырехканальный мультиплексор. Функциональная схема состоит из общей схемы управления, представляющий собой преобразователь логических уровней входных управляющих сигналов, дешифратора 2:4 и восьми двунаправленных ключей, разделенных на две синхронно работающих группы по четыре ключа в каждой.

Управление осуществляется по двум адресным входам А и В и разрешающему входу  . При наличии на входе

. При наличии на входе  низкого уровня любой из четырех возможных комбинаций на входах А и В соответствует один открытый канал в каждом мультиплексоре одновременно. При подаче на вход

низкого уровня любой из четырех возможных комбинаций на входах А и В соответствует один открытый канал в каждом мультиплексоре одновременно. При подаче на вход  высокого уровня все ключи размыкаются, каналы – закрыты. Вход

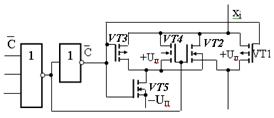

высокого уровня все ключи размыкаются, каналы – закрыты. Вход  имеет абсолютный приоритет перед любым другим входом управления. В мультиплексорах использован модифицированный ключ (рисунок 11.7). Кроме основных транзисторов VT1 и VT2 в ней введен дополнительный ключ VT3, VT4 и управляющий транзистор VT5. Благодаря использованию в мультиплексоре модифицированного ключа сопротивление открытого канала мало и имеет слабую зависимость от изменения входного сигнала в диапазон коммутируемых напряжений UП1…UП2. Питание осуществляется от двух источников питания. Разность напряжения UП2 – UП1 должна быть не более 15 В. Это позволяет коммутировать сигналы с амплитудой до 15 В, лежащие в диапазоне UП2 ¸ UП1.

имеет абсолютный приоритет перед любым другим входом управления. В мультиплексорах использован модифицированный ключ (рисунок 11.7). Кроме основных транзисторов VT1 и VT2 в ней введен дополнительный ключ VT3, VT4 и управляющий транзистор VT5. Благодаря использованию в мультиплексоре модифицированного ключа сопротивление открытого канала мало и имеет слабую зависимость от изменения входного сигнала в диапазон коммутируемых напряжений UП1…UП2. Питание осуществляется от двух источников питания. Разность напряжения UП2 – UП1 должна быть не более 15 В. Это позволяет коммутировать сигналы с амплитудой до 15 В, лежащие в диапазоне UП2 ¸ UП1.

Например, питание может быть «0 ¸ +15 В», « – 7, 5 В ¸ +7, 5 В», « – 3 В ¸ +3 В», « ‑10 В ¸ +5 В». В диапазоне этих питающих напряжений можно располагать коммутируемый сигнал. Максимальный допустимый ток через открытый ключ не более 10 мА.

Рисунок 11.6 –Условное графическое обозначение:

а − ИС К564КП1; б − функциональная схема

Рисунок 11.7 – Принципиальная схема канала

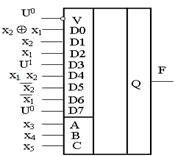

Микросхема К564КП2– восьмиканальный мульти-плексор, предназначенный для переключения цифровых и аналоговых сигналов (рисунок 11.8).Функциональная схема состоит из преобразователя логических уровней, дешифраторов и восьми двунаправленных аналоговых ключей. Управление вентильными ключами производится выходными сигналами дешифратора, которые вырабатываются под воздействием трехразрядного двоичного кода А В С. Нормальная работа микросхемы обеспечивается при нулевом напряжении на разрешающем входе V, при лог. 1 выходные ключи разомкнуты. Неискаженная передача аналоговых сигналов обеспечивается выбором питающих напряжений и схемой их подключения. Для питания микросхемы имеются три вывода. Ножка 8 служит общим выводом, 16 – «+ЕП» и 7 – «– ЕП».

Максимальное напряжение, прикладываемое к двум выводам микросхемы, не должно превышать 15 В.

Рисунок 11.8 – Условное обозначение К564КП2

11.5 Синтез комбинационных схем на мультиплексорах

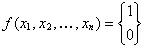

Мультиплексор является универсальным логическим элементом. Эта особенность основана на использовании общих свойств переключательных функций равняться логической единице или нулю при любом числе аргументов:

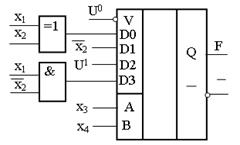

Если на адресные входы мультиплексора подать входные переменные, на информационные входы – значения лог. 0 или лог. 1 в соответствии с переключательной таблицей, то на входе получим значение нулей и единиц в соответствии с программой. Например, необходимо реализовать на мультиплексорах функцию «равнозначности»:

|

Функция имеет уровень лог. 1 на наборах x2 x1 = 00 и x2 x1 = 11 и уровень лог. 0 на наборах x2 x1 = 01 и x2 x1 = 10 (таблица 11.1). Для реализации данной функции необходимо подать на адресные входы мультиплексора сигнала x2x1, на входы D0 и D3 – потенциал высокого уровня U1, на входы D1 и D2 - потенциалы низкого уровня U0 и на разрешающий вход V – уровень логического нуля U0, как показано на рисунке 11.9. При переборе входных адресов на выходе будет формироваться заданная переключательная функция.

Рисунок 11.9 – Реализация функции «равнозначность»

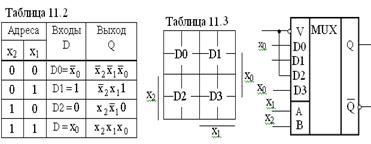

При синтезе схем с тремя аргументами f (x2 x1 x0) в качестве адресных сигналов можно взять любые две переменные, например, x2 x1, тогда выходная функция будет определяться третьей переменной x0, принимающей значения лог. 0 или лог.1 (const 0 или const 1). При этом возможны всего лишь четыре значения входной функции:  . В качестве примера рассмотрим реализацию переключательной функции трех переменных, представленной в таблице 11.2. Поскольку переменные x2 x1 определяют номер подключаемого входа (D0 D1 D2 D3), то сигнал, действующий на данном входе, определяется информацией, расположенной в двух соседних клетках. Как показано в таблице 11.3, на входе D0 действует сигнал

. В качестве примера рассмотрим реализацию переключательной функции трех переменных, представленной в таблице 11.2. Поскольку переменные x2 x1 определяют номер подключаемого входа (D0 D1 D2 D3), то сигнал, действующий на данном входе, определяется информацией, расположенной в двух соседних клетках. Как показано в таблице 11.3, на входе D0 действует сигнал  , на входе D1 – const 1, на входе D2 – const 0 и на входе D3 – x0. Схемная реализация этой переключательной функции приведена на рисунке 11.10. В общем случае при реализации функции n переменных n-1 аргумент является адресной частью и определяет требуемое количество входов мультиплексора – 2n – 1. Следовательно, функция четырех переменных может быть реализована на восьмивходовых мультиплексорах, пяти переменных – на шеснадцативходовых мультиплексорах и т.д.

, на входе D1 – const 1, на входе D2 – const 0 и на входе D3 – x0. Схемная реализация этой переключательной функции приведена на рисунке 11.10. В общем случае при реализации функции n переменных n-1 аргумент является адресной частью и определяет требуемое количество входов мультиплексора – 2n – 1. Следовательно, функция четырех переменных может быть реализована на восьмивходовых мультиплексорах, пяти переменных – на шеснадцативходовых мультиплексорах и т.д.

Рисунок 11.10 – Схемная реализация

При большом числе переменных (n ≥ 4) такой формализованный подход вряд ли оправдан, т.к. аппаратные затраты возрастают, а выигрыш необоснован. Более целесообразно в этих случаях синтез комбинационных на мультиплексорах производить с использованием элементов некоторого базиса, например, И, ИЛИ, НЕ и т.д.

В этом случае часть переменных nадр используют в качестве адресов мультиплексора, остальные n – nадр служат для формирования управляющих сигналов по информационным входам.

Пусть задана переключательная функция четырех переменных f(x4x3x2x1) в виде суммы суммы минтермов:

Если переменные x4 x3 будут являться адресами выбора входа мультиплексора, тогда карта Вейча для данной переключательной функции будет выглядеть, как показано в таблице 11.4.

Квадрат, описанный произведением  , будет определять вход D0,

, будет определять вход D0,  – первый,

– первый,  – второй и

– второй и  – третий вход мультиплексора. Минимизация функции по каждому входу производится для каждого квадрата индивидуально. Анализ информации, расположенной в еречисленных квадратах, дает следующие результаты:

– третий вход мультиплексора. Минимизация функции по каждому входу производится для каждого квадрата индивидуально. Анализ информации, расположенной в еречисленных квадратах, дает следующие результаты:

Схемная реализация этой функции приведена на рисунке 11.11

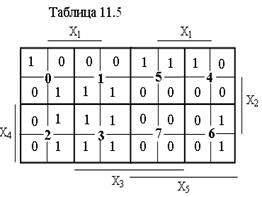

Минимизированное выражение для данной функции, полученное обычным образом, выглядит следующим образом:  . Для схемной реализации данного выражения требуется пять трехвходовых ЛЭ типа И (два корпуса К555ЛА4 – 3И-НЕ´3) и один корпус К555ЛА3 для реализации логического сложения. Сравнение ранее полученного решения с данным показывает, что первый вариант выигрывает по сравнению со вторым по числу используемых корпусов МСХ и сложности монтажа. Синтез комбинированных схем с пятью переменными x5, x4, x3, x2, x1 можно вести на восьмивходовых мультиплексорах. В качестве адресных сигналов можно выбирать переменные x5, x4, x3, а информационные сигналы формировать из переменных x2, x1. Рассмотрим пример схемной реализации переключательной функции, представленной в таблице 11.5, на восьмивходовом мультиплексоре. Адресные переменные x5, x4, x3 задают номер квадрата, который соответствует такому же номеру информационного входа. Логическое выражение, описывающее функцию внутри каждого квадрата, определяет характер входного сигнала на данном входе. При диагональном расположении единиц описывающая функция является «равнозначностью» или «неравнозначностью» x2 и x1, одна «единица» в квадрате описывается логическим произведением входных переменных (x2 x1), а горизонтальное или вертикальное расположение двух «единиц» дает прямое или инверсное значение одной из входных переменных.

. Для схемной реализации данного выражения требуется пять трехвходовых ЛЭ типа И (два корпуса К555ЛА4 – 3И-НЕ´3) и один корпус К555ЛА3 для реализации логического сложения. Сравнение ранее полученного решения с данным показывает, что первый вариант выигрывает по сравнению со вторым по числу используемых корпусов МСХ и сложности монтажа. Синтез комбинированных схем с пятью переменными x5, x4, x3, x2, x1 можно вести на восьмивходовых мультиплексорах. В качестве адресных сигналов можно выбирать переменные x5, x4, x3, а информационные сигналы формировать из переменных x2, x1. Рассмотрим пример схемной реализации переключательной функции, представленной в таблице 11.5, на восьмивходовом мультиплексоре. Адресные переменные x5, x4, x3 задают номер квадрата, который соответствует такому же номеру информационного входа. Логическое выражение, описывающее функцию внутри каждого квадрата, определяет характер входного сигнала на данном входе. При диагональном расположении единиц описывающая функция является «равнозначностью» или «неравнозначностью» x2 и x1, одна «единица» в квадрате описывается логическим произведением входных переменных (x2 x1), а горизонтальное или вертикальное расположение двух «единиц» дает прямое или инверсное значение одной из входных переменных.

В результате анализа таблицы 11.5 получим следующие значения функций по входам мультиплексора:

D0 – Х1 Å Х2 ; D1 – Х2 ; D2 – Х1 ; D3 –U1 ;

D4 – Х1 Х2 ; D5 –  ; D6 –

; D6 –  ; D7 – U0.

; D7 – U0.

Реализация этой функции на восьмивходовом мультиплексоре приведена на рисунке 11.12.

Минимизированное выражение для данной переключательной функции, полученное традиционным способом, дает следующий результат:

Рисунок 11.11 – Схемная реализация

Рисунок 11.12 – Схемная реализация на восьмивходовом мультиплексоре

Релизация этого выражения на логических элементах типа И, ИЛИ, НЕ окажется весьма громоздкой. Сравнение полученных результатов показывает, что использование мультиплексоров для реализации логических функций во многих случаях оказывается оправданным.

12 АРИФМЕТИЧЕСКИЕ УСТРОЙСТВА

12.1 Комбинационные двоичные сумматоры

Сумматор – это узел, в котором выполняется арифметическая операция суммирования цифровых кодов двух двоичных чисел. Числа в любой позиционной системе счисления складываются поразрядно. Поэтому сложить двоичные числа можно при наличии узлов, реализующих суммирование цифр одного разряда слагаемых с учетом возможного переноса из соседнего младшего разряда. К таким узлам относят одноразрядные комбинационные полусумматоры и сумматоры.

Комбинационный полусумматор HS предназначен для суммирования двух одноразрядных двоичных чисел. Он имеет два входа  , и

, и  , два выхода – Si и Pi+1. Выход Si является выходом суммы, а выход Pi+1 – выходом переноса.

, два выхода – Si и Pi+1. Выход Si является выходом суммы, а выход Pi+1 – выходом переноса.

На основании таблицы 12.1 переключательные функции для Si, и Pi+1 в СДНФ будут иметь следующий вид:

Полусумма  является функцией неравнозначности входных сигналов

является функцией неравнозначности входных сигналов  и

и  («исключающее ИЛИ» )

(«исключающее ИЛИ» )

, (12.1)

, (12.1)

которая инверсна по отношению к функции равнозначности

. (12.2)

. (12.2)

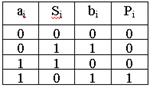

Таблица 12.1

Рисунок 12.1 – Полусумматор: а − функциональная схема;

б − условное графическое изображение

Устройство можно реализовать на логических элементах И, ИЛИ (рисунок 12.1). Основным требованием, предъявляемым к нему, является получение максимального быстродействия при минимальном числе последовательно включенных элементов.

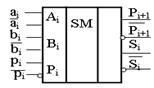

Одноразрядный комбинационный сумматор  предназначен для суммирования трех одноразрядных двоичных чисел. Он имеет три входа:

предназначен для суммирования трех одноразрядных двоичных чисел. Он имеет три входа:  ,

,  ,

,  и два выхода: Si и Pi+1. На входы

и два выхода: Si и Pi+1. На входы  и

и  поступают значения суммируемых цифр данного разряда, на вход

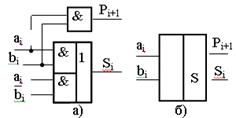

поступают значения суммируемых цифр данного разряда, на вход  – значение переноса из соседнего младшего разряда. Порядок переключения трехвходового сумматора представлен в таблице 12.2, условное графическое обозначение на рисунке 12.2. На основе таблицы истинности (таблица 12.2) переключательные функции в СДНФ для Si и Pi+1 будут иметь следующий вид:

– значение переноса из соседнего младшего разряда. Порядок переключения трехвходового сумматора представлен в таблице 12.2, условное графическое обозначение на рисунке 12.2. На основе таблицы истинности (таблица 12.2) переключательные функции в СДНФ для Si и Pi+1 будут иметь следующий вид:

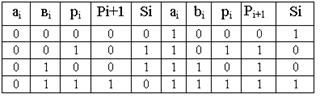

Таблица 12.2

Рисунок 12.2 – Одноразрядный комбинационный сумматор

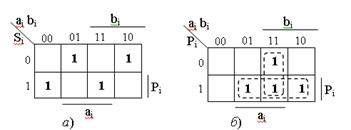

Минимизируем полученные выражения с помощью карт Карно (рисунок 12.3). Анализ таблицы для Si показывает, что переключательная функция упрощению не поддается. Тогда преобразуем это выражение с помощью правил алгебры логики. Объединим первый и четвертый, второй и третий минтермы, а их общие сомножители (Pi и  ) вынесем за скобки:

) вынесем за скобки:

.

.

С учетом (12.1) и (12.2) это выражение запишется в виде  .

.

Оригинальное выражение для суммы Si можно получить непосредственно из таблицы 12.2

.

.

Минимизированное логическое выражение для результата переноса в следующий разряд Pi+1 найдем по карте Карно:

Pi+1 = ai bi + ai Pi + bi Pi = ai bi + Pi (ai + bi).

Введем обозначения:

Gi = ai bi и Ti = (ai + bi),

получим

Pi+1 = Gi + Pi Ti.

Рисунок 12.3 – Карты Карно: а − переключательных функций Si; б − переключательных функцийPi

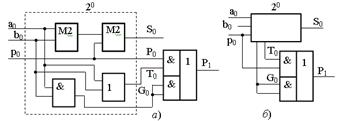

Функцию Gi называют функцией генерации (формирования) поразрядного переноса i-го разряда, а Ti – функцией передачи (распространения) переноса для i- го разряда. Реализация устройства суммирования трехразрядного сумматора может выполняться как показано на рисунке 12.4.

Рисунок 12.4 – Сумматор: а − одноразрядный сумматор; б− упрощенное изображение

МикросхемаК555ИМ5 – два одноразрядных полных сумматора. Она выполняет операцию сложения трех одноразрядных чисел в двоичном коде с учетом переноса младшего разряда в старший (рисунок 12.5).

Состояние выходных уровней схемы в зависимости от состояний на входах  ,

,  и

и  соответствует показанным в таблице 12.2.

соответствует показанным в таблице 12.2.

Высокий и низкий уровни сигнала на выходах схемы Sn и Pn+1 устанавливаются при наличии высокого и низкого уровней на всех входах микросхемы.

Рисунок 12.5 – Условное графическое изображение ИС К555ИМ5

Дата добавления: 2020-03-17; просмотров: 1386;