Микросхема К564 ТМ3

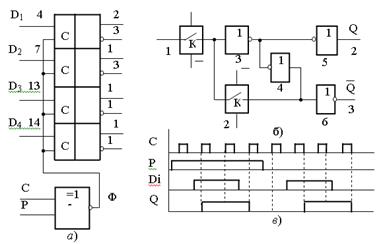

МСХ состоит из четырех D-триггеров со статическим управлением записью. Синхронизация осуществляется единым для всех триггеров управляющим устройством, что показано на функциональной схеме (рисунок 15.11, а). Запись информации по входам D1 – D4 возможна только в случае равенства уровней сигналов синхронизации С (Сlock) и полярности Р (Рolarity), т.е. при С = Р= 1 или С = Р= 0. В случае неравенства уровней С ≠ Р – режим хранения записанной информации. Такая организация управления применяется широко в устройствах КМОП, придавая им дополнительные функциональные возможности.

Функциональные схема одной триггерной ячейки приведена на рисунке 15.11, б. Ее основу составляют два двунаправленных ключа (ячейки 1, 5) и четыре инвертора D3 – D6.

Собственно бистабильную ячейку, которая хранит одно из двух стабильных состояний, образуют инверторы D3, D4. При этом ключ 2 открыт, а ключ 1 заперт. В режиме записи открыт входной ключ 1, а заперт ключ 2, и цепь положительной обратной связи между ячейками D3, D4 разорвана. Эти ячейки работают как два последовательно включенных инвертора. При переходе от режима записи к режиму хранения ключ 2 в цепи обратной связи замыкается быстрее, чем запирается ключ 1 во входной цепи, что обеспечивает режим запоминания информационного сигнала. Временные диаграммы, поясняющие работу триггера, приведены на рисунке 15.11, в.

Следует обратить внимание на то, что с помощью входа Р переключается полярность действия синхроимпульса и запись информации производится как единичными, так и нулевыми уровнями сигналов C и P. Если на входе Р присутствует лог.1, то запись происходит по положительному перепаду синхроимпульса. При нулевом уровне на входе Р запись информации с входов D1 – D4 будет производиться по срезу (отрицательному перепаду положительного импульса) синхроимпульса.

а − функциональная схема; б − функциональная схема одного триггера; в − временные диаграммы работы триггера

Рисунок 15.11 – Микросхема К564ТМ3

15.7 D-триггеры, тактируемые фронтом

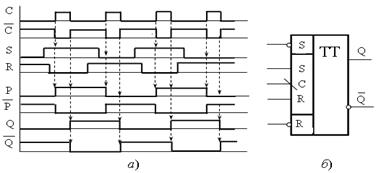

Синхронные триггеры типа D c динамическим управлением по входу C воспринимают входную иинформацию лишь в моменты перехода сигнала на C-входе с уровня лог. 0 на высокий уровень, что существенно улучшает функциональные характеристики триггера. Один из вариантов построения такого триггера на шести логических ячейках И-НЕ приведен на рисунке 15.12.

Собственно запоминающая ячейка собрана на логических элементах 5, 6. В цепях управления триггером  , RT стоят бистабильные ячейки 1, 2, 3, 4. Синхроимпульсы положительной полярности поступают на входы ячеек 2, 3. В отсутствие синхроимпульса

, RT стоят бистабильные ячейки 1, 2, 3, 4. Синхроимпульсы положительной полярности поступают на входы ячеек 2, 3. В отсутствие синхроимпульса  и выходной триггер находится в режиме хранения информации.

и выходной триггер находится в режиме хранения информации.

Пусть на входе D установлен логический уровень 1. На выходе b ячейки 4 установится лог. 0, поскольку входные сигналы D =  =

=  имеют высокий уровень. Далее сигнал b поступает на вход ячейки 1, что приводит к установлению уровня «1» на ее выходе (а = 1), так как b×

имеют высокий уровень. Далее сигнал b поступает на вход ячейки 1, что приводит к установлению уровня «1» на ее выходе (а = 1), так как b×  = 0. С приходом положительного фронта синхроимпульса на выходе ячейки 2 установится нулевой уровень:

= 0. С приходом положительного фронта синхроимпульса на выходе ячейки 2 установится нулевой уровень:  , в результате чего на выходе появится уровень лог.1:

, в результате чего на выходе появится уровень лог.1:

D n+1 = Dn .

На выходе ячейки 3 будет удерживаться уровень лог. 1:

,

,

где  , а C = 1.

, а C = 1.

Такая ситуация будет сохраняться до конца действия синхроимпульса. При этом любые возможные изменения информации на входе D не проходят далее выхода ячейки 4, потому что на входах ячеек 1 и 3 стоит уровень 0 сигнала  . Подобным образом происходит запись уровня 0 на вход D с приходом очередного фронта тактирующего импульса.

. Подобным образом происходит запись уровня 0 на вход D с приходом очередного фронта тактирующего импульса.

Таким образом, время записи информации в триггер D с динамическим управлением определяется длительностью фронта тактирующего импульса и временем задержки распространения на двух логических элементах 2tЗ1.

Триггер оснащается дополнительными входами асинхронной установки  (на рисунке 15.12, а показаны пунктиром). Сигналы заводятся на основной триггер и входы бистабильных управляющих ячеек.

(на рисунке 15.12, а показаны пунктиром). Сигналы заводятся на основной триггер и входы бистабильных управляющих ячеек.

Способ записи информации в D-триггеры фронтом импульса реализован в триггерах ТМ2 в любой из выпускаемых серий, например, ТТЛШ 1531ТМ2, КМОП – К564ТМ2, ЭСТЛ – К500ТМ2. В каждом корпусе МСХ размещены два D-триггера с динамическим управлением и со входами асинхронной установки  .

.

Способы обозначения динамических входов триггеров показаны на рисунке 15.13.

Рисунок 15.12 – D-триггер с динамическим управлением:

а − логическая структура; б − функциональное обозначение;

в − временные диаграммы

Рисунок 15.13 − Обозначения динамических входов триггеров:

а − при управлении положительным фронтом; б − при управлении отрицательным фронтом

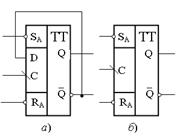

Счетные триггеры

Счетный триггер или триггер типа Т имеет один счетный (информационный) вход Т и один или два входа начальной установки. Триггер переходит в состояние противоположное исходному с приходом каждого импульса на счетный вход Т (от англ. Toggle – релаксатор). Строятся счетные триггеры на основе триггеров типа D с динамическим управлением или двухступенчатых синхронных триггеров.

Двухступенчатый триггер строится на основе двух одноступенчатых синхронных триггеров, включенных последовательно. Такая схема построения триггера получила название «M-S» (master-slave = хозяин-раб) или в русской интерпретации ведущий – ведомый. Логическая схема двухступенчатого триггера SR-типа, построенного по схеме M-S, и его структурное изображение приведено на рисунке 15.14. Причем на первый триггер синхронизирующие импульсы C поступают в прямой форме, на вход второго – в инверсной форме.

Когда на вход синхронизации С приходит положительный импульс, происходит запись информации в ведущий триггер. В это время на входе ведомого триггера действует нулевой уровень сигнала  , триггер находится в неактивном состоянии и не воспринимает информацию с выходов P и

, триггер находится в неактивном состоянии и не воспринимает информацию с выходов P и  ведущего триггера. В момент перехода импульса C с единицы на нуль (1/0) ведущий триггер переходит в пассивное состояние, зафиксировав на своих выходах Р,

ведущего триггера. В момент перехода импульса C с единицы на нуль (1/0) ведущий триггер переходит в пассивное состояние, зафиксировав на своих выходах Р,  принятую информацию. Спустя время t31, равное времени задержки переключения инвертора 5, единичное напряжение

принятую информацию. Спустя время t31, равное времени задержки переключения инвертора 5, единичное напряжение  установится на выходных логических ячейках ведомого триггера. Последний перейдет в активный режим записи входной информации, имеющейся на выходах ведущего триггера. Сигналы на выходах Q и

установится на выходных логических ячейках ведомого триггера. Последний перейдет в активный режим записи входной информации, имеющейся на выходах ведущего триггера. Сигналы на выходах Q и  триггера появятся еще через 2t31, поэтому суммарная задержка составит 3t31 после поступления отрицательного фронта тактирующего импульса С. Временные диаграммы работы двухступенчатого триггера приведены на рисунке 15.15.

триггера появятся еще через 2t31, поэтому суммарная задержка составит 3t31 после поступления отрицательного фронта тактирующего импульса С. Временные диаграммы работы двухступенчатого триггера приведены на рисунке 15.15.

На функциональной схеме синхронизирующий вход С обозначен как инверсный динамический, принадлежность триггера к классу двухступенчатых отмечено сдвоенной буквой Т. Кроме того, показаны асинхронные входы начальной установки триггера (SA, RA), которые могут быть заведены непосредственно на входы ячеек ведущего и ведомого триггеров.

Как самостоятельные изделия двухступенчатые синхронные триггеры не выпускаются, но они являются базой для построения счетных Т-триггеров и универсальных JK - триггеров.

Рисунок 15.4 – Логическая схема:

а − JK-триггера; б − Функциональное обозначение

Рисунок 15.15 – Синхронный двухступенчатый триггер:

а − временные диаграммы; б − функциональное значение

Счетный триггер на базе синхронного двухступенчатого триггера строится следующим образом: выход  соединяется со входом S, а выход Q – со входом R. Пусть на выходах триггера Q = 0,

соединяется со входом S, а выход Q – со входом R. Пусть на выходах триггера Q = 0,  = 1. После прохождения первого тактирующего импульса (по его срезу) на входе Q установится высокий уровень, на входе

= 1. После прохождения первого тактирующего импульса (по его срезу) на входе Q установится высокий уровень, на входе  – уровень лог. 0.

– уровень лог. 0.

После второго импульса триггер вновь возвратится к исходному состоянию, потому что нулевое напряжение с выхода  по входу S запишется на прямой выход триггера. Следовательно, текущее состояние триггера определяется его состоянием на предыдущем такте и информацией на входе:

по входу S запишется на прямой выход триггера. Следовательно, текущее состояние триггера определяется его состоянием на предыдущем такте и информацией на входе:

Qn+1 = Qn  Ú

Ú  n Tn.

n Tn.

Это выражение соответствует функции «исключающее ИЛИ» или «сумма по mod 2», отчего он получил название «счетный». Его второе название – «делитель частоты на 2», т.к. на два входных положительных синхроимпульса на выходе Q формируется один положительный импульс, как показано на рисунке 15.16, б. В счетный режим можно перевести триггер типа-D, тактируемый фронтом. Для этого достаточно инверсный вход  триггера соединить с его информационным входом D (рисунок 15.17, а). С приходом каждого тактирующего импульса триггер переключается в противоположное состояние. Функциональное обозначение триггера Т-типа приведено на рисунке 18.17, б.

триггера соединить с его информационным входом D (рисунок 15.17, а). С приходом каждого тактирующего импульса триггер переключается в противоположное состояние. Функциональное обозначение триггера Т-типа приведено на рисунке 18.17, б.

а − функциональная схема; б − временные диаграммы

Рисунок15.16 –Т-триггер на основе двухступенчатого триггера

Универсальный синхронный JK-триггер, как правило, строится на основе триггера MS-типа, переведенного в счетный режим. На входы управляющей ячейки 1 ведущего триггера М вводятся дополнительные логически связанные входы J (J = J1 = J2 = J3), аналогичные входам S синхронного триггера, а на вход ячейки 2 – входы К (К = К1 = К2 = К3) подобные входам R (рисунок 15.18).

Рисунок 15.17 – Счетный триггер:

а − на базе D-триггера; б − Функциональное обозначение

15.9 Универсальные JK-триггеры

Особенностью универсального JK-триггера является способность работать в любом из известных режимов.

Асинхронный режим управления по входам S, R заключается в том, что независимо от состояний входов J, K, C на выходе триггера может быть установлен уровень «0» (  = 1,

= 1,  = 0), либо «1» (

= 0), либо «1» (  = 0,

= 0,  = 1). Пассивное состояние обеспечивается при

= 1). Пассивное состояние обеспечивается при  =

=  = 1, а «запрещенная» комбинация – при

= 1, а «запрещенная» комбинация – при  =

=  = 0.

= 0.

В счетный режим триггер переходит при J = K =  =

=  = 1, переключение триггера в противоположное состояние при этом осуществляется по перепаду 1/0 на тактовом входе С.

= 1, переключение триггера в противоположное состояние при этом осуществляется по перепаду 1/0 на тактовом входе С.

При J= 0, K= 1 первый тактовый импульс по срезу (перепад 1/0 ) установит на выходе Q низкое напряжение (Q = 0) – режим управления нулем.

При J= 1, K= 0 перепад 1/0 на входе С установит на выходе Q единичное напряжение(Q = 1) – режим управления единицей.

При J = 0, K = 0 триггер переходит в режим хранения информации (Qn+1= Qn ) и не реагирует на тактовые импульсы.

Полное функционирование триггера описано в таблице 15.8.

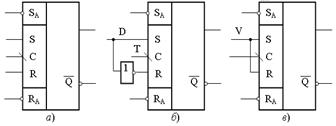

Рисунок 15.18 – Логическая схема:

а − JK − триггера; б − функциональное обозначение

При анализе таблицы 15.8 можно заметить, что переход триггера из состояния «0» в состояние «1» происходит при J = 1 и любом состоянии входа К (строки 1, 3), при этом сигнал на входе К обозначается символом Ф или X. Переключение триггера из «1» в «0» произойдет при К = 1 и любом уровне на входе J (строки 6 и 7). Триггер сохраняет единичное напряжение на выходе при К = 0 и безразличном состоянии входа J (строки 4, 5), а нулевое – при J = 0, К = 0 (строки 0, 2). Это позволяет перейти к минимизированной таблице переходов универсального JK-триггера (таблица 15.8 – сокращенная форма).

Синхронный режим работы JK-триггера в режиме RS осуществляется при использовании входа J в качестве входа S, входа К в качестве входа R (рисунок 15.19, а). Как и в одноступенчатом синхронном RS-триггере при S=1, R=0, по срезу тактового импульса С на выходе Q будет установлена «1», при S=0, R=1 на выходе установится «0», при S=0 – режим хранения предыдущей информации. В отличие от одноступенчатого триггера управляющая комбинация S=R=1 является не незапрещенной: она переводит универсальный триггер в счетный режим.

Универсальный JK-триггер можно перевести в режим работы триггера типа D. Для этого необходимо информацию (данные D) подать на один из входов J, ее инверсное значение – на вход К, как показано на рисунке 15.19, б.

Таблица 15.8 – Таблица истинности универсального

JK-триггера

| tn | tn+1 | tn | tn+1 | tn | tn+1 | ||||||||||||||||

| N | Jn | Kn | Qn | Qn+1 | N | Jn | Kn | Qn | Qn+1 | N | Jn | Kn | Qn | Qn+1 | |||||||

| X | |||||||||||||||||||||

| X | |||||||||||||||||||||

| X | |||||||||||||||||||||

| X | |||||||||||||||||||||

JK-триггер можно перевести в любой из известных режимов с дополнительным управлением по входу V (V – разрешающий, управляющий вход). Для этого объединяются J и К и на них подается разрешающее управляющее напряжение V (рисунок 15.19, в). Входы V и Т являются равноценными, их можно менять местами.

Триггеры JK-типа имеются во многих интегральных сериях микросхем ТТЛ, ТТЛШ, КМОП. В серии К155 триггер ТВ1 со входной логикой на 3И по входам J и К, со входами асинхронной установки  ,

,  , как изображено на рисунке 15.18. В корпусе размещен один триггер, он имеет максимальную скорость переключения 15 МГц, потребляет ток 15 мА при питающем напряжении +5В.

, как изображено на рисунке 15.18. В корпусе размещен один триггер, он имеет максимальную скорость переключения 15 МГц, потребляет ток 15 мА при питающем напряжении +5В.

В быстродействующей серии ТТЛШ К531 имеются триггеры ТВ9, ТВ10, ТВ11. Микросхема ТВ9 – два JK-триггера со сбросом и установкой, ТВ10 – два JK-триггера с установкой, ТВ11 – два JK-триггера со сбросом и установкой, причем входы синхронизации и установки сдвоены.

а − синхронный RS-триггер; б − D-триггер; в − VT-триггер

Рисунок 15.19 – Варианты схем включения JK-триггеров

Усовершенствованная серия ТТЛШ КР1531 имеет микросхему ТВ15, содержащую два JK-триггера со сбросом и установкой, причем вход К проинвертирован. Вход С прямой динамический, информация на выходе появляется в момент действия положительного фронта импульса синхронизации. Поскольку К вход проинвертирован, то такие триггеры легко превращать в D-триггеры.

Частота переключения данных триггеров 100 МГц, средний ток потребления 6,5 мА, напряжение питания + 5 В.

РЕГИСТРЫ

Регистры – это цифровые устройства, служащие для приема, хранения, преобразования и выдачи информации, представленной в виде многоразрядных двоичных слов. Они представляют собой цифровые автоматы Мили, выполненные на синхронных триггерах того или иного типа, со схемами управления входными и выходными сигналами. Элементами структуры регистров являются синхронные триггеры D-типа или SR (JK)-типа со статическим либо динамическим управлением. Одна триггерная ячейка может принять и хранить один двоичный бит информации. Количество разрядов в регистре определяется длиной многоразрядного двоичного слова, подлежащего обработке. При этом «вес», «весовой коэффициент» каждого разряда определяется только содержанием записанной в регистр информации. Занесение информации в регистр обычно называют операцией «ввода» или «записи», а выдачу информации именуют «выводом» или «считыванием». Основные функции, выполняемые регистрами, сводятся к следующим:

– установка триггеров регистра в исходное состояние «0» или «1»;

– прием информации в параллельном или последовательном кодах;

– хранение n-разрядного кода в течение заданного времени;

– сдвиг информации на определенное число разрядов влево или вправо;

– преобразование двоичного параллельного кода в последовательный и наоборот;

– поразрядные логические операции.

В зависимости от функциональных свойств регистры делятся на две категории: накопительные (регистры памяти и хранения) и сдвигающие (сдвиговые). Сдвигающие регистры обладают большими функциональными возможностями по сравнению с простейшими накопительными регистрами. По способу ввода и вывода информации они делятся на параллельные, последовательные и комбинированные.По направлению передачи информации они подразделяются на однонаправленные и реверсивные.

16.1 Параллельные регистры

Двоичное n-разрядное число, предназначенное для хранения, поступает на вход регистра памяти в параллельной форме, т.е. все разряды подаются одновременно. Рационально в качестве регистра использовать простейшие триггеры типа D, управляемые потенциалом или фронтом. В одном корпусе может быть размещено четыре, шесть или восемь отдельных триггеров, связанных общими цепями синхронизации и управления.

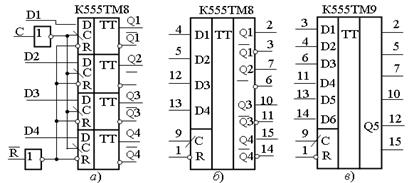

Микросхемы К555ТМ8 и К555ТМ9 представляют собой соответственно четыре и шесть D-триггеров, соответственно, с общим входом синхронизации и общим входом сброса (рисунок 16.1). ИС К555ТМ8 имеет внешние выводы с прямого и инверсного выхода, а ИС К555ТМ9 – только прямой выход.

Схемы выполнены на двухступенчатых, синхронных, динамических D-триггерах. Вход сброса управляется инверсным сигналом, а вход синхронизации – прямым сигналом.

Регистры характеризуются минимальной длительностью импульса для записи информации и определенными временными соотношениями по времени установления tуст и времени удержания tуд на входах управления регистров относительно входов информации. Время установления сигнала – это интервал времени, который необходим для установки сигнала информации с опережением сигнала синхронизации (разрешения) при записи информации.

а − функциональная схема К555ТМ8; б − условное обозначение ИС К555ТМ8; в − функциональное обозначение ИС К555ТМ9

Рисунок 16.1 − D-триггер

Время удержания сигнала – интервал времени, который необходим для завершения записи при удержании сигнала информации на заданном уровне после воздействия сигнала синхронизации. Следует обратить внимание на то, что информационный сигнал единичного или нулевого уровня на входе D должен установиться до прихода переднего фронта импульса за время, превышающее минимальное значение tуст, и должен сохранять свой уровень в течение некоторого времени, превышающего минимальное значение tуд. Следовательно, для обеспечения надежной работы регистра памяти необходимо, чтобы длительность импульса синхронизации Ти превышала tуд минимум в 2¸3 раза. Длительность паузы Тп между импульсами синхронизации также должна существенно превышать минимальное значение tуст. Необходимо отметить, что для записи информации в регистр нет необходимости в очистке регистра, т.е. в его обнулении с помощью сигнала начальной установки.

Временные диаграммы, поясняющие работу триггерной ячейки регистра памяти, приведены на рисунке 16.2. Значительный интерес для разработчиков радиоэлектронной аппаратуры представляют восьмиразрядные регистры памяти серий К555, К531, 1533: ИР22, ИР23, ИР27, ИР33, ИР34, ИР35, ИР37.

Рисунок 16.2 – Временные диаграммы

Все упомянутые регистры имеют достаточно сходную логическую структуру и различаются лишь некоторыми частностями в организации ввода и вывода информации.

Микросхема 1533ИР37 представляет собой восьмиразрядный буферный регистр. Логическая структура и условное обозначение приведены на рисунке 16.3, а, б. Регистр построен на D-триггерах с импульсным управлением, вход прямой динамический, переключение производится положительным фронтом тактового импульса. Регистр имеет восемь входов данных D0 – D7 и восемь выходов Q0 – Q7. Когда на специальный вход  подается низкий уровень, то после поступления положительного перепада на тактовый вход С входная информация появляется на выходах Q. Если на

подается низкий уровень, то после поступления положительного перепада на тактовый вход С входная информация появляется на выходах Q. Если на  установлен высокий уровень, то выходные буферные каскады переводятся в высокоимпедансное состояние (состояние Z). При низком уровне тактового сигнала С триггеры регистра находятся в режиме хранения информации, зафиксированной при прохождении предыдущего положительного фронта импульса С.

установлен высокий уровень, то выходные буферные каскады переводятся в высокоимпедансное состояние (состояние Z). При низком уровне тактового сигнала С триггеры регистра находятся в режиме хранения информации, зафиксированной при прохождении предыдущего положительного фронта импульса С.

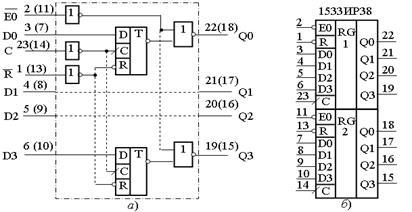

Микросхема 1533ИР38содержит два одинаковых четырехразрядных регистра, построенных на синхронных D-триггерах с тремя состояниями выхода. Логическая структура одного регистра и условное графическое обозначение ИР38 приведены на рисунке 16.4. Каждый регистр имеет четыре входа и выхода, вход  , тактовый вход С и вывод

, тактовый вход С и вывод  для управления Z-состоянием выходов. Если на вывод

для управления Z-состоянием выходов. Если на вывод  подать уровень лог. 1, то выходные буферы окажутся в третьем (разомкнутом) состоянии. Обнуление регистров происходит при подаче на вход

подать уровень лог. 1, то выходные буферы окажутся в третьем (разомкнутом) состоянии. Обнуление регистров происходит при подаче на вход  низкого уровня напряжения.

низкого уровня напряжения.

Рисунок 16.3 – Регистр: а − структура 1533ИР37; б− уловное обозначение

Данные со входов Di поступят на выходы Qi при поступлении переднего фронта (перепад 0/1) тактового импульса на вход С.

Рисунок 16.4 – Структура и условное обозначение регистра 1533ИР38

16.2 Сдвигающие регистры

Сдвигающие регистры представляют собой цепочку последовательно стоящих триггеров, логически определенным образом связанных между собой. Сдвигающие регистры могут выполнять следующие операции: сдвиг информации вправо; сдвиг информации влево; прием и выдача информации последовательным или параллельным кодом; хранение.

Сдвиг информации заключается в том, что цифра, хранившаяся в i-ом разряде регистра до сдвига, после каждого тактового импульса передается в (i+1)-й разряд при сдвиге вправо или в соседний (i–1)-й разряд при сдвиге влево. На функциональных схемах регистры обозначаются буквенным символом RG. Под символом ставится стрелка, указывающая направление сдвига: ® вправо, влево, « двунаправленный (реверсивный). Выше указывалось, что понятие «весовых коэффициентов» к разрядам регистра не применяется и вес каждого разряда считается равным единице или определяется записанной в регистр информацией.

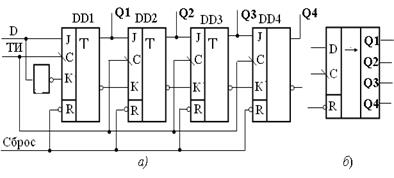

16.2.1 Последовательный регистр сдвига вправо

Принципиальными особенностями такого регистра являются следующие: информационные входы каждого последующего триггера соединены с выходами предыдущего, синхронизирующие входы триггеров объединены, вход начальной установки регистров общий. На рисунке 16.5 приведена схема четырехразрядного сдвигающего регистра с последовательным вводом, выполненного на универсальных JK-триггерах, например, K555TB6. Первый триггер при помощи инвертора включен по схеме D-триггера и служит для приема входной информации по входу D. К исходному состоянию, когда все триггеры регистра включены, регистр приводится с помощью импульса начальной установки нулевого уровня У0, подаваемого на вход R. Пусть на вход D первого триггера установлен уровень лог. 1. С приходом первого после У0 тактирующего импульса ТИ произойдет запись единицы в первый триггер.

а − функциональная схема; б − условное изображение

Рисунок 16.5 – Четырехразрядный сдвигающий регистр с последовательным вводом

Уровень 1 на прямом выходе Q1 этого триггера устанавливается после прохождения заднего фронта ТИ (перепад 1/0) через время tзад (рисунок 16.6), определяемое быстродействием данного типа триггера. Содержимое второго, третьего и четвертого триггеров при этом не изменится, т.к. во время прохождения среза первого ТИ на выходах первого, второго и третьего триггеров был нулевой уровень. Допустим, к приходу второго тактового импульса ТИ2 на входе первого триггера был установлен нуль, тогда после окончания второго импульса на выходе Q1 будет нуль, на выходе Q2 – лог. 1, на выходах Q3, Q4 будут по прежнему низкие уровни напряжения. Пусть в третьем и четвертом тактах (t3 и t4 соответственно) на вход первого триггера поступает высокий уровень напряжения – единица. Третий тактирующий импульс запишет эту единицу в первый триггер, а нуль с выхода Q1 запишется во второй триггер. Единица с выхода Q2 перепишется в третий триггер, а четвертый триггер останется в нулевом состоянии. Четвертый ТИ запишет входную единицу в первый триггер, включит второй триггер и выключит третий, единицу с выхода Q3 перепишет в четвертый триггер.

Рисунок 16.6 – Временные диаграммы последовательного

Дата добавления: 2020-03-17; просмотров: 2442;