Дешифраторы-демультиплексоры ТТЛ

Устройства типа дешифратор-демультиплексор достаточно широко представлены во многих сериях ТТЛ и ТТЛШ (К155, К133, К555, К1530…). Они отличаются по количеству адресных входов, набору управляющих сигналов, организации выхода, потребляемой мощности и способны решать многие задачи, выдвигаемые практикой. Дешифраторы выпускаются на два, три и четыре входа.

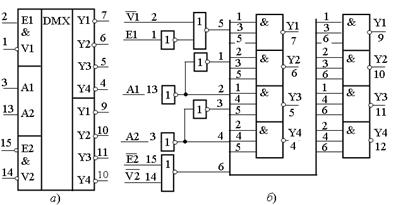

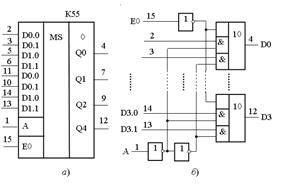

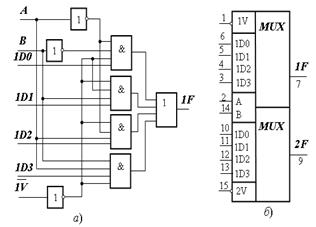

Микросхема К155ИД4 – сдвоенный дешифратор-демуль-типлексор 2  4 с общими входами дешифрируемого кода и раздельным управлением шинами разрешения E1, V1 и E2 и V2 (рисунок 10.4).

4 с общими входами дешифрируемого кода и раздельным управлением шинами разрешения E1, V1 и E2 и V2 (рисунок 10.4).

Активным уровнем выходных сигналов является лог. 0. В зависимости от схемы включения микросхема может быть использована в следующих режимах: два дешифратора с двух каналов на четыре; два демультиплексора с одного канала на четыре; дешифратор с трех каналов на восемь; демультиплексор с одного канала на восемь.

а − дешифратор К155ИД4; б − функциональная схема

Рисунок 10.4 –Условное графическое изображение

Два дешифратора 2´4 получаются, когда входы А1 и А2 служат как адресные, на разрешающих входах первого дешифратора устанавливают Е1 – лог. 1,  - лог. 0, на разрешающих входах второго дешифратора

- лог. 0, на разрешающих входах второго дешифратора  и

и  – лог. 0. При построении двух демультиплексоров с одного канала на четыре можно подать разрешающие сигналы Е1 – лог. 0,

– лог. 0. При построении двух демультиплексоров с одного канала на четыре можно подать разрешающие сигналы Е1 – лог. 0,  - лог. 0, а входы

- лог. 0, а входы  и

и  использовать в качестве информационных. В этом случае фаза (полярность) входных и выходных сигналов будет совпадать. Микросхему можно использовать в качестве дешифратора трехразрядного кода на восемь выходов и как демультиплексор от одного входа на восемь выходов. Для получения третьего адресного входа А3 соединим входы

использовать в качестве информационных. В этом случае фаза (полярность) входных и выходных сигналов будет совпадать. Микросхему можно использовать в качестве дешифратора трехразрядного кода на восемь выходов и как демультиплексор от одного входа на восемь выходов. Для получения третьего адресного входа А3 соединим входы  и Е1 и на объединенный вход подадим старший разряд (А3) адреса (рисунок 10.5).

и Е1 и на объединенный вход подадим старший разряд (А3) адреса (рисунок 10.5).

При нулевом значении А3 работает верхний канал дешифратора (  ), т. к. на входе Е1 устанавливается высокий уровень напряжения. При высоком уровне третьего адреса активизируются выходы нижнего канала (

), т. к. на входе Е1 устанавливается высокий уровень напряжения. При высоком уровне третьего адреса активизируются выходы нижнего канала (  ), поскольку на

), поскольку на  – активный нулевой уровень. При использовании дешифратора как демультиплексора 1: 8 информацию (D –Data) следует подавать одновременно на входы

– активный нулевой уровень. При использовании дешифратора как демультиплексора 1: 8 информацию (D –Data) следует подавать одновременно на входы  и

и  .

.

Рисунок 10.5 – Дешифратор 3:8 на К155ИД4

Активные уровни информационных сигналов при этом будут совпадать с активными уровнями выходных сигналов дешифратора. Структура микросхемы позволяет производить дальнейшее наращивание разрядности демультиплексора.

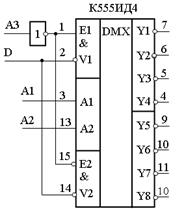

Микросхема К555ИД19 служит для преобразования двоичного четырехразрядного кода в унитарный 16-разрядный код. Микросхема имеет четыре адресных входа А3А2А1А0 два входа управления  ,

,  и 16 выходов 0,1,…,15 с активными низкими уровнями напряжения (рисунок 10.6, а).

и 16 выходов 0,1,…,15 с активными низкими уровнями напряжения (рисунок 10.6, а).

Для создания режима демультиплексора 1:16 один из входов V заземляют (создают уровень лог. 0), а другой используют в качестве информационного. Кодовая комбинация на адресных входах переводит один из шестнадцати выходов в активное состояние, которому соответствует  . Остальные пятнадцать выходов при этом сохраняют уровень лог. 1. Сигналы на активном выходе повторяют в прямом виде сигналы, поступающие на информационный вход (

. Остальные пятнадцать выходов при этом сохраняют уровень лог. 1. Сигналы на активном выходе повторяют в прямом виде сигналы, поступающие на информационный вход (  или

или  ).

).

Рисунок 10.6 – Условное изображение микросхемы:

а − К555ИД19; б − схема дешифратора 5:32

Если на обоих разрешающих входах поддерживать уровень

V0 = V1 = 0 микросхема работает как дешифратор четыре входа – шестнадцать выходов. Потенциал U1 на любом разрешающем входе установит уровень лог. 1 на всех выходах независимо от состояния адресных входов.

Микросхемы К555ИД19 можно применять для преобразования входных сигналов, разрядность которых больше четырех.

На рисунке 10.6, б показана схема демультиплексора (дешифратора) пятиразрядного двоичного кода, собранного на двух микросхемах.

Шины младших четырех разрядов соединяют с входами А0 - А4 обоих приборов, а сигналы старшего разряда подают в прямом виде на один из разрешающих входов первой микросхемы и в инверсном – на разрешающий вход другой. Вторые разрешающие входы  заземляются (режим дешифратора), либо на них подают информационные сигналы (режим демультиплексора). Пирамидальная система на 17 микросхемах позволяет получить устройство с 256 выходами.

заземляются (режим дешифратора), либо на них подают информационные сигналы (режим демультиплексора). Пирамидальная система на 17 микросхемах позволяет получить устройство с 256 выходами.

Микросхема К555ИД10 – дешифратор классического типа, преобразующий четырехразрядный двоично-десятичный код в десятичный. На рисунке 10.7 приведена функциональная схема дешифратора. Все выходы микросхемы выполнены с открытым коллектором (Ucc до 15 В), и логическая функция выполняется при подключении нагрузки между выходом микросхемы и источником питания.

Рисунок 10.7 − Дешифратор К155ИД10:

а − условное обозначение; б − структурная схема

Если десятичный эквивалент входного кода превышает 9, то на всех выходах дешифратора установится напряжение высоких уровней. Эти устройства могут дешифрировать числа 0 - 8, тогда вход А8 можно использовать как разрешающий с низким активным уровнем. На этот вход можно подавать данные, если использовать ИД10 как демультиплексор на восемь выходов.

В функциональный состав цифровых маломощных КМОП-структур (564, 1564) также включены ряд дешифраторов.

Микросхема К564ИД1 служит для преобразования двоично-десятичного кода в десятичный или двоичного в восьмеричный, как и К555ИД10, но, в отличие, от нее имеет прямые выходы.

Микросхема К564ИД4 – дешифратор возбуждения одноразрядного семисегментного жидкокристаллического индикатора, микросхема К1564ИД3 – дешифратор на четыре входа – шестнадцать выходов.

11 МУЛЬТИПЛЕКСОРЫ

11.1 Назначение и принцип работы

Назначение мультиплексоров (от англ. Multiplexer – MUX – многократный) – коммутировать в нужном порядке входную информацию, поступающую с нескольких шин, на одну выходную. Мультиплексор имеет несколько информационных входов D0, D1,…,DN - 1, адресные входы A0, A1,… AN - 1, вход для подачи стробирующего сигнала C и один выход D0 (  ). Причем количество входов N и число адресных шин n связаны соотношением N = 2n. Входные информационные сигналы DI – Data Input – будем сокращенно именовать D. Стробирующий сигнал мультиплексора выбирает один из входов и подключает его к входу (селектирует входную шину). Основу мультиплексора составляет линейный дешифратор, выходы которого объединены по ИЛИ. Логическая функция, которую реализует мультиплексор:

). Причем количество входов N и число адресных шин n связаны соотношением N = 2n. Входные информационные сигналы DI – Data Input – будем сокращенно именовать D. Стробирующий сигнал мультиплексора выбирает один из входов и подключает его к входу (селектирует входную шину). Основу мультиплексора составляет линейный дешифратор, выходы которого объединены по ИЛИ. Логическая функция, которую реализует мультиплексор:

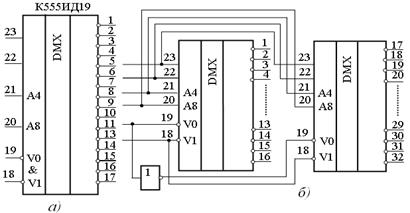

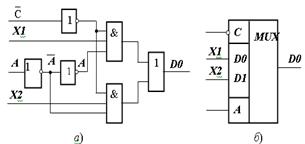

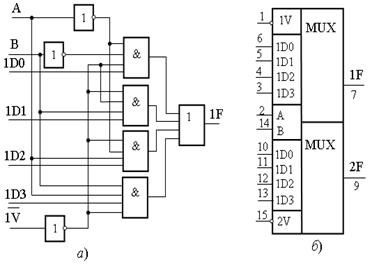

На рисунке 11.1, а приведена принципиальная схема простейшего мультиплексора-селектора вида «две линии к одной» (2:1).

Собственно мультиплексор выполнен на двух логических ячейках И, выполняющих роль дешифратора, и одной ячейки ИЛИ, логически суммирующих выходные сигналы дешифратора. Адрес выбранного направления определяется сигналом А: при А = 0 работает верхняя ячейка И и входной сигнал Х1 появляется на выходе D0, при А = 1 включена нижняя ячейка И и на выходе появляется сигнал Х2. Синхросигнал  управляет работой ячеек в дешифраторе. При

управляет работой ячеек в дешифраторе. При  = 1 работа дешифратора запрещена, на выходе D0 устновлен лог 0. При

= 1 работа дешифратора запрещена, на выходе D0 устновлен лог 0. При  = 0 ячейки дешифратора активизированы. Информация проходит на выход с того входа, двоичный код которого указан на адресных входах. Кроме того, вход

= 0 ячейки дешифратора активизированы. Информация проходит на выход с того входа, двоичный код которого указан на адресных входах. Кроме того, вход  позволяет наращивать разрядность дешифратора по числу входов. Условное графическое изображение простейшего мультиплексора приведено на рисунке 11.1, б.

позволяет наращивать разрядность дешифратора по числу входов. Условное графическое изображение простейшего мультиплексора приведено на рисунке 11.1, б.

а − принципиальная схема; б − условное изображение

Рисунок 11.1 – Мультиплексор – селектор вида 2:1

11.2 Мультиплексоры ТТЛ

Мультиплексоры ТТЛ, как самостоятельные изделия, широко представлены во многих сериях (К155, К133, К555, К531, К1533 и др.). Строятся они на основе линейных дешифраторов, как было показано выше, и отличаются по числу информационных и адресных входов, наличием или отсутствием стробирующего входа, характером выходных сигналов (прямые, инверсные или парные).

Микросхема К555КП11 (КП14, КП16) – четыре мульти-плексора,организованных для мультиплексирования двух каналов в один (  ) с общим дешифратором адреса.

) с общим дешифратором адреса.

Рисунок 11.2 –Условное графическое обозначение ИС:

а − К555КП11; б − функциональная схема

На рисунке 11.2, а, б представлены функциональная схема и условное графическое обозначение ИС К555 КП11. Всостав микросхемы входит четыре мультиплексора  , аналогичных показанному на рисунке 11.1. Отличие состоит в том, что разрешающий вход

, аналогичных показанному на рисунке 11.1. Отличие состоит в том, что разрешающий вход  здесь заменен входом Е, обеспечи-вающим перевод выходов мультиплексора в высокоимпедансное состояние Z. Когда на входе Е уровень лог.1 все выходы находятся в третьем состоянии, рабочий режим обеспечивается уровнем лог. 0 на этом входе. Выбор канала производится с помощью адресной шины А. При нулевом уровне адреса подключены шины D0, при уровне лог. 1 на выход поступают сигналы с шин D1.

здесь заменен входом Е, обеспечи-вающим перевод выходов мультиплексора в высокоимпедансное состояние Z. Когда на входе Е уровень лог.1 все выходы находятся в третьем состоянии, рабочий режим обеспечивается уровнем лог. 0 на этом входе. Выбор канала производится с помощью адресной шины А. При нулевом уровне адреса подключены шины D0, при уровне лог. 1 на выход поступают сигналы с шин D1.

МикросхемаК555КП13– четыре мультиплексора, органи-зованных для мультиплексирования двух каналов в один (  , с общим дешифратором адреса. В отличие от ИС К555 КП11, она имеет на выходе регистр хранения информации, выполненный на двухтактных синхронных триггерах типа «M-S» («ведущий-ведомый»). Запись информации в выходной регистр производится в момент среза тактирующего импульса на входе С (перепад 1/0).

, с общим дешифратором адреса. В отличие от ИС К555 КП11, она имеет на выходе регистр хранения информации, выполненный на двухтактных синхронных триггерах типа «M-S» («ведущий-ведомый»). Запись информации в выходной регистр производится в момент среза тактирующего импульса на входе С (перепад 1/0).

Микросхема К555 КП2 – это два мультиплексора  с общими адресными входами А, В выбора канала и раздельными входами выбора одного из мультиплексоров 1

с общими адресными входами А, В выбора канала и раздельными входами выбора одного из мультиплексоров 1  и 2

и 2  (рисунок 11.3). Каждый мультиплексор реализует следующую функцию:

(рисунок 11.3). Каждый мультиплексор реализует следующую функцию:

.

.

Двоичный код, который набран на адресных входах, разрешающий работу одного из информационных входов каждого мультиплексора. Сигнал с выбранного информационного входа появляется на выходе только при наличии на стробирующем входе  данного мультиплексора сигнала низкого уровня.

данного мультиплексора сигнала низкого уровня.

Рисунок 11.3 – Логическая структура ½ мултиплексора

а −К555КП2; б − условное графическое изображение

Микросхемы К555КП7 и К555КП15– имеют организацию мультиплексирования восьми каналов в один. Они имеют восемь информационных входов D0 – D7, три адресных входа A, B, C, разрешающий вход Е, и прямой D и инверсный выход  . Функциональная схема и условное графическое обозначение ИС К555КП15 приведено на рисунке 11.4, б. В отличие от К555 КП7, этот мультиплексор имеет три состояния выхода. Закон функционирования мультиплексора:

. Функциональная схема и условное графическое обозначение ИС К555КП15 приведено на рисунке 11.4, б. В отличие от К555 КП7, этот мультиплексор имеет три состояния выхода. Закон функционирования мультиплексора:

Сигнал с выбранного информационного входа появится на выходе при низком уровне разрешающего сигнала  , при высоком уровне сигнала

, при высоком уровне сигнала  на обоих выходах установится состояние Z.

на обоих выходах установится состояние Z.

Микросхема К155КП1 имеет 16 информационных входов D0 - D15 и четыре управляющихвхода А, B, C, D, разрешающий вход V и один инверсный выход  (рисунок 11.4, а). В зависимости от цифровой комбинации на управляющих входах сигналы с соответствующего информационного входа проходят в инвертированном виде на выход микросхемы. Передача информации возможна, если на разрешающий вход действует напряжение низкого уровня.

(рисунок 11.4, а). В зависимости от цифровой комбинации на управляющих входах сигналы с соответствующего информационного входа проходят в инвертированном виде на выход микросхемы. Передача информации возможна, если на разрешающий вход действует напряжение низкого уровня.

Рисунок 11.4 – Условное графическое изображение:

а − ИС К155КП1; б − ИС К555КП15

При высоком уровне на разрешающем входе схема блокируется и на выходе микросхемы возникает напряжение высокого уровня.

11.3 Наращивание разрядности мультиплексоров

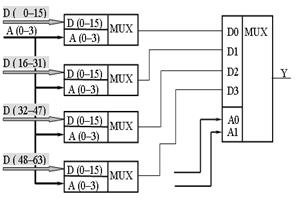

Максимальное число информационных входов одного мультиплексора равно 16. Увеличить число мультиплексируемых линий можно путем наращивания разрядности. Основные способы решения этой задачи: построение мультиплексорной структуры пирамидального типа (мультиплексорное дерево) и объединение нескольких мультиплексоров с помощью внешних логических элементов. На рисунке 11.5 показан вариант мультиплексора 64:1, выполненного на четырех мультиплексорах К555 КП1 и мультиплексоре К555 КП2. Мультиплексоры управляются шестиразрядным адресным кодом A5 - A0. Младшие разряды кода адреса A3A2A1A0 подаются в параллельном виде на адресные входы первой ступени, два старших разряда A5A4 являются адресами выходной ступени. Двоичный код A9 – A0 указывают номер входа, который подключен к выходу каждого входного мультиплексора. Код A5A4 указывает номер той микросхемы первой ступени, выход которой подключен к общему выходу Y мультиплексора.

Рисунок 11.5 – Мультиплексор 64:1 на четырех мультиплексорах К555КП1 и мультиплексоре К555КП2 (1/2)

На приведенной структурной схеме не указаны разрешающие входы V мультиплексоров.Общее число информационных входов Nвх пирамидального мультиплексора равно произведению числа входов одного мультиплексора N1 на количество мультиплексоров n первой ступени: Nвх = n N1. Для получения больших значений Nвх необходимо увеличивать число ступеней преобразования. Рост числа ступеней преобразования приводит к пропорциональному возрастанию времени задержки появления сигнала на выходе.

Дата добавления: 2020-03-17; просмотров: 2459;