Шестнадцатеричные и двоичные коды

| Шестнадцатеричный код | Двоичный код | |||

| A | ||||

| B | ||||

| C | ||||

| D | ||||

| E | ||||

| F |

Адресный код представляется четырьмя шестнадцатеричными цифрами N3N2N1N0, каждая из которых отображает состояние соответствующей тетрады адресных линий (рисунок 6 и таблица 1).

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

N3

N2

N1

N0

Рисунок 6- Формат адресного слова микроконтроллера

Адресное поле системы ввода—вывода кодируется двумя шестнадцатеричными цифрами и находится в пределах 00 ... FF.

Линии шины данных  используются для обмена информацией между МПР и источниками или приемниками сообщений, представленными ячейками системы памяти или регистрами системы ввода—вывода.

используются для обмена информацией между МПР и источниками или приемниками сообщений, представленными ячейками системы памяти или регистрами системы ввода—вывода.

Управляющие сигналы (сигналы линии шины управления) MEMR, W, MEMW, OUT, INP служат для указания направления передачи информации по шине данных, а также для запуска адресованного элемента (ячейки памяти, регистра системы ввода—вывода) на выполнение предписанной функции. Сигналы MEMR и INP означают, что информация принимается, а сигналы W и MEMW или OUT означают, что информация выдается. При обращении МПР к системе памяти используются сигналы MEMR или W и MEMW, при обращении к системе ввода—вывода сигналы OUT или INP.

Сигнал СБР вырабатывается при включении питания и необходим для приведения микроконтроллера в исходное состояние (соответствует ручному режиму работы).

Черта над буквенным обозначением сигналов свидетельствует о том, что уровень логической единицы 1 (активное состояние сигнала) соответствует низкому уровню напряжения (от 0 до 0,4 В; высокий уровень — 2,4—5,25 В).

Как правило, в любой операции обмена данными участвуют управляющее и исполнительное устройства. Управляющим устройством микроконтроллера является модуль процессора, исполнительным — модули систем памяти и ввода— вывода. В зависимости от направления прохождения информации устройство может быть приемником (принимать данные) или источником (выдавать данные).

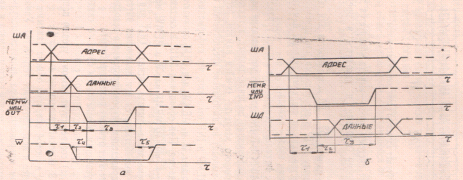

Рисунок 7- Временные диаграммы циклов: а - вывода данных из модуля процессора; б – ввода данных

Последовательностью операций обмена данными между модулем процессора и модулями-исполнителями управляет исполнительная программа. Процедура обмена соответствует определенным логическим условиям, изображаемым в виде временных диаграмм (рисунок 7).

В режиме вывода информации (рисунок 7, а) МПР устанавливает адрес устройства — приемника, размещает на шине данных передаваемое сообщение и по линиям связи W иMEMW или OUT посылает команду записи: В течение времени τ1+τ2каждый из модулей МКП-1 осуществляет сравнение принимаемого от МПР адреса с предписанным ему собственным адресом. Приемник, опознавший на шине адреса (ША) собственный адрес, устанавливает связь с МПР и при наличии сигнала W и MEMW или OUT принимает данные в свою функциональную часть, в качестве которой может выступать ячейка памяти (при получении сигналов W иMEMW) или регистр системы ввода—вывода (при получении сигнала CUT).

В режиме ввода информации в МПР (рисунок 7,б) источник выдает адресные операции и устанавливает связь с процессором аналогично вышеописанному. Получив команду чтения по одной из линий MEMR (для ячеек памяти) или INP (для регистров системы ввода—вывода), адресованное устройство передает на шину данных (ШД) информацию, которая принимается в МПР в течение промежутка времени, равного длительности сигналов приема (τ3).

Формируемые МПР выдержки времени τ1,τ2, τ4, τ5в режиме вывода данных и τ1 τ2в режиме приема необходимы для завершения переходных процессов в линиях связи при смене информации на ША и ШД, а также для окончания выполнения исполнительными устройствами адресных операций.

Длительность τ3 сигналов управления в обоих режимах выбрана достаточной для того, чтобы наиболее медленное из исполнительных устройств успело закончить операцию приема информации или ее выдачи, осуществляемую источником с задержкой τ2.

Дата добавления: 2022-02-05; просмотров: 547;