Интегральные таймеры

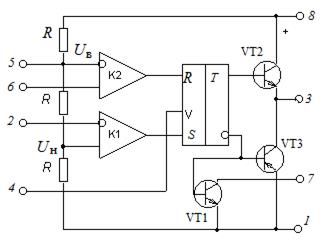

Интегральные таймеры – это многофункциональные элементы в микросхемном исполнении, на основе которых можно решать широкий круг задач: генерировать импульсы в автоколебательном и ждущем режимах в широком интервале длительности (частоты повторения); генерировать линейно-изменяющееся напряжение; преобразовывать напряжение в частоту; регулировать температуру, освещенность (при наличии соответствующих датчиков); преобразовывать постоянное напряжение в постоянное напряжение другого уровня или полярности и т. п. Классическая функциональная схема таймера представлена на рис. 6.7.

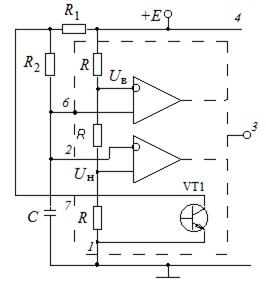

Таймер содержит два компаратора – нижнего уровня (К1) и верхнего уровня (К2), управляющий триггер со входом разрешения V = 0, на выходе 3 триггера принудительно устанавливается логический 0, при V = 1 работа таймера разрешена, разрядный ключ (транзистор VТ1) и выходной усилитель мощности ключевого типа (VТ2, VТ3), обеспечивающий ток нагрузки до 200 мА.

При напряжении на входе 2  компаратор К1 устанавливает триггер в состояние 1, при этом VТ1 заперт, причем это состояние таймера не зависит от состояния компаратора К2, т. е. К1 обладает приоритетом перед К2.

компаратор К1 устанавливает триггер в состояние 1, при этом VТ1 заперт, причем это состояние таймера не зависит от состояния компаратора К2, т. е. К1 обладает приоритетом перед К2.

Рис. 6.7. Функциональная схема таймера

Если на входе 6 напряжение U6>UВ, то К2 устанавливает триггер в 0, при этом VТ1 открывается. Таким образом, вход 2 является входом «запуска» таймера, а вход 6 – входом «сброс». Напряжения  ,

,  . При таком соотношении уровней обеспечивается минимальная нестабильность интервалов времени.

. При таком соотношении уровней обеспечивается минимальная нестабильность интервалов времени.

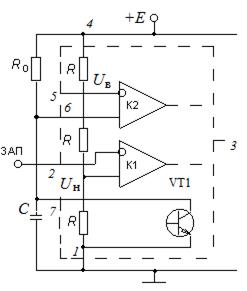

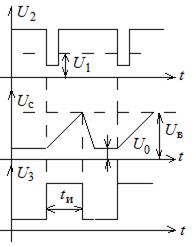

В качестве примера рассмотрим работу таймера в режиме ждущего мультивибратора (см. рис. 6.8). В исходном режиме триггер удерживается в состоянии 0 высоким уровнем U2. Когда на входе 2 напряжение запускающего импульса U2 < UН, то триггер устанавливается в 1, VТ1 запирается , начинается заряд конденсатора С от источника питания Е через резистор R0. При UС ³ UВ триггер устанавливается в 0, VТ1 открывается – происходит быстрый разряд конденсатора до напряжения U0 (напряжение насыщения коллектор-эмиттер VТ1). Длительность импульса рассчитывается по очевидному соотношению

.

.

а б

Рис. 6.8. Таймер в режиме ждущего мультивибратора:

а – принципиальная схема; б – диаграмма напряжений

Если выполнить условие E>>U0, то стабильность tИ будет полностью определяться стабильностью произведения R0C0, которое может быть сделано достаточно высоким выбором качественных элементов.

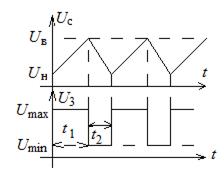

Схема таймера, работающего в режиме автоколебаний, приведена на рис. 6.9. В исходном состоянии UС<UН, компаратор K1 удерживает VT1 в запертом состоянии, проходит заряд конденсатора от источника E через резисторы R1 и R2. При UС³ UВ компаратор K2 переключает триггер в состояние низкого уровня, а VT1 открывается, происходит разряд конденсатора через резистор R2 и VT1 до UС£ UН, после чего начинается процесс разряда конденсатора. В силу разницы постоянных времени заряда t3=C(R1+R2) и разряда  длительность паузы t2 в рассматриваемой схеме получается меньше импульса t1. Такой автогенератор называют несимметричным. На рис. 6.10 изображен вариант использования таймера в качестве датчика, например инфракрасного излучения.

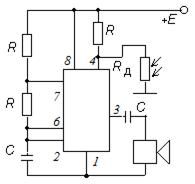

длительность паузы t2 в рассматриваемой схеме получается меньше импульса t1. Такой автогенератор называют несимметричным. На рис. 6.10 изображен вариант использования таймера в качестве датчика, например инфракрасного излучения.

В этой схеме таймер, по аналогии со схемой на рис. 6.9, работает в режиме автогенератора при условии, что сигнал разрешения V имеет высокий потенциал. Значение этого потенциала зависит от сопротивления датчика Rд. При наличии излучения датчик имеет низкое сопротивление, таймер заторможен. При исчезновении излучения таймер начинает генерировать импульсы звуковой частоты, воспроизводимые динамиком. В литературе рассматривается огромное число применений таймера, который по своему функциональному разнообразию не уступает операционному усилителю.

а б

Рис. 6.9. Таймер в режиме автоколебаний:

а – принципиальная схема; б – диаграмма напряжений

Рис. 6.10. Схема датчика

инфракрасного излучения

Для получения высокой стабильности временных интервалов используются цифровые таймеры.

В этих устройствах стабильность цифровых интервалов определяется стабильностью кварцевого генератора фиксированной частоты,

а длительность генерируемых интервалов (импульсов) изменяется программно путем записи в двоичный счетчик большего или меньшего числа. Принципы построения можно продемонстрировать на упрощенной структурной схеме (см. рис. 6.11).

Таймер построен на вычитающем счетчике. Запись исходного кода, присутствующего на входах Д, производится при наличии высокого потенциала на входе разрешения записи V.

Рис. 6.11. Структурная схема цифрового таймера

В исходном состоянии устройство управления УУ задает V=1. С приходом фронта первого синхроимпульса, генерируемого, например, кварцевым генератором, УУ снимает сигнал разрешения записи V = 0 и счетчик производит по фронтам синхроимпульсов вычитание. Обнуление счетчика регистрируется сигналом переноса P = 1, по которому УУ выставляет V=1, происходит очередная запись кода и т. д. Очевидно, что период выходных импульсов таймера TИ связан с периодом синхроимпульсов T0 соотношением

,

,

где А – значение входного кода. Тем самым цифровой таймер выдает временные интервалы, стабильность которых практически не отличается от стабильности кварцевого генератора, и в то же время длительность этих интервалов может изменяться в широких пределах программным способом – заданием входного кода.

Дата добавления: 2016-06-22; просмотров: 3717;