Цифровые компараторы

Устройства, предназначенные для сравнения двух чисел (A и B), представленных в двоичной форме: a1, a2, …, am и b1, b2, …, bm. Результатом сравнения является обнаружение одного из трех возможных состояний: A = B, A > B или A < B.

Таблица состояний одноразрядного компаратора (табл. 4.9).

| Таблица 4.9 | ||||

| a | b | ya>b | ya=b | ya<b |

Логические уравнения, описывающие работу компаратора:

Соответственно структурная схема одноразрядного компаратора рис. 4.19.

Рис. 4.19. Структура одноразрядного компаратора

Для сравнения многоразрядных двоичных чисел используется следующий алгоритм. Сначала сравниваются значения старших разрядов. Если они различны, то эти разряды и определяют результат сравнения. Если они равны, то необходимо сравнивать следующие за ними, более младшие, разряды. Условное изображение цифрового компаратора приведено на рис. 4.20. Входы (A = B, A > B, A < B) служат для наращивания разрядности компаратора (каскадное соединение).

Рис. 4.20. Условное изображение цифрового компаратора

Контрольные вопросы и задания

1. Найдите по справочнику дешифратор К555ИД7. Разберитесь с его работой по таблице состояний.

2. Найдите по справочнику мультиплексор К531КП2. Разберитесь с его работой по таблице состояний. Используя этот мультиплексор, постройте устройство, выполняющее следующую логическую функцию:  .

.

5. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ

ЦИФРОВЫЕ УСТРОЙСТВА

Состояние выходов последовательностных устройств определяется не только состоянием входов в данный момент времени, но и предыдущим состоянием выходов. Таким образом, последовательностные устройства обладают «памятью». Рассмотрим наиболее характерные последовательностные устройства.

Триггеры

Триггеры – цифровые устройства с двумя выходами (прямым Q и инверсным  ), состояние которых, однажды установленное, может сохраняться сколь угодно долго. Изменение исходного состояния производится с помощью входных сигналов по правилу работы каждого типа триггера. Таким образом, триггер может хранить заложенный в нем 1 бит информации.

), состояние которых, однажды установленное, может сохраняться сколь угодно долго. Изменение исходного состояния производится с помощью входных сигналов по правилу работы каждого типа триггера. Таким образом, триггер может хранить заложенный в нем 1 бит информации.

|

|

= 0 или Q = 0,

= 0 или Q = 0,  =1), и комбинационная схема (KC), преобразующая поступающие сигналы в сигналы управления БЯ. Комбинационная схема содержит информационные входы (X0¸Xn), входы синхронизации

=1), и комбинационная схема (KC), преобразующая поступающие сигналы в сигналы управления БЯ. Комбинационная схема содержит информационные входы (X0¸Xn), входы синхронизации  и входы разрешения

и входы разрешения  .

.

В принципе можно синтезировать большое число триггерных структур с различным законом функционирования. Однако в цифровой электронике нашли применение 4 типа триггеров: RC-триггер, D-триггер,

JK-триггер, T-триггер. Информационные входы этих триггеров имеют следующие обозначения:  (Set – установка) – вход для раздельной установки триггера в состояние «1» (Q=1,

(Set – установка) – вход для раздельной установки триггера в состояние «1» (Q=1,  =0); R (Reset – сброс) – вход для раздельной установки триггера в состояние «0» (Q = 0,

=0); R (Reset – сброс) – вход для раздельной установки триггера в состояние «0» (Q = 0,  = 1); D (Delay – задержка) – вход для установки триггера в состояние «1» или «0»; J (Jerk – внезапное выключение) – вход для раздельной установки триггера в состояние «1»; K (Kill – внезапное отключение) – вход для раздельной установки в состояние «0»; T (Toggle – релаксатор) – счетный вход триггера; V (Valre – клапан, вентиль) – управляющий вход для разрешения приема информации либо тактовых импульсов; C (Clock – первичный источник синхронизации) – разрешает запись информации в триггер.

= 1); D (Delay – задержка) – вход для установки триггера в состояние «1» или «0»; J (Jerk – внезапное выключение) – вход для раздельной установки триггера в состояние «1»; K (Kill – внезапное отключение) – вход для раздельной установки в состояние «0»; T (Toggle – релаксатор) – счетный вход триггера; V (Valre – клапан, вентиль) – управляющий вход для разрешения приема информации либо тактовых импульсов; C (Clock – первичный источник синхронизации) – разрешает запись информации в триггер.

По способу восприятия входных сигналов триггеры могут быть асинхронными (нетактируемыми) и синхронными (тактируемыми). Асинхронные триггеры воспринимают информацию в любой момент времени, а синхронные – только при наличии разрешающего сигнала на специальном тактовом C-входе. Синхронизация ограничивает время приема триггером входных сигналов, а следовательно, уменьшает вероятность, при появления помехи на сигнальных входах, ложного срабатывания триггера. Другими словами, синхронизация повышает помехоустойчивость, которая является важным параметром любого цифрового устройства, т. к. замена в результате помехи хотя бы одного элемента двоичного кода приведет к полному искажению информации.

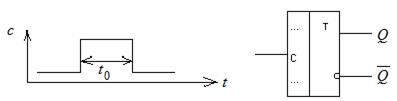

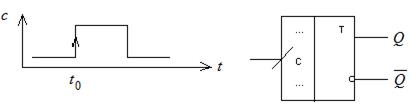

Синхронизация может быть статическая – уровнем (высоким, низким) или динамическая – перепадом на C-входе (фронтом, срезом). Условные обозначения способов синхронизации представлены на рис. 5.2, где С – синхроимпульс,  – промежутки времени, в течение которых триггер воспринимает входную информацию.

– промежутки времени, в течение которых триггер воспринимает входную информацию.

По виду выходных сигналов триггеры разделяют на статические и динамические. Статические – триггеры, у которых выходные сигналы в устойчивых состояниях остаются неизменными во времени. В динамических триггерах выходные сигналы представляют последовательность импульсов.

По способу запоминания информации могут быть триггеры с логической и физической организацией памяти. Первые выполняются на логических элементах, во вторых используются нелинейные свойства материалов или нелинейные характеристики компонентов.

Характеристики триггеров определяются прежде всего параметрами логических элементов, на которых выполнен триггер. Специфическими параметрами триггера являются:

· время задержки переключения триггера  ,

,  ,

,  , которое определяется количеством элементов от информационного (тактового) входа до выхода. Минимальная длительность входного сигнала

, которое определяется количеством элементов от информационного (тактового) входа до выхода. Минимальная длительность входного сигнала  ;

;

· разрешающее время триггера  – наименьший интервал времени между входными сигналами минимальной длительности, вызывающими бесперебойное переключение триггера;

– наименьший интервал времени между входными сигналами минимальной длительности, вызывающими бесперебойное переключение триггера;

· максимальная частота переключения триггера  .

.

Обычно рабочую частоту принимают в 1,5 раза меньше максимальной.

а

б

в

Рис. 5.2. Способы синхронизации и условные обозначения триггеров:

а – высоким уровнем синхроимпульса; б – фронтом синхроимпульса;

в – срезом синхроимпульса

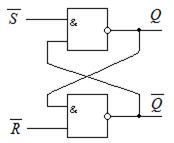

5.1.1. RS-триггер

RS-триггер может быть построен на логических элементах ИЛИ-НЕ, И-НЕ. На рис. 5.3 приведена схема RS-триггера на элементах ИЛИ-НЕ. Как видно из схемы, логические элементы замкнуты в кольцо  (выход каждого из них подключен ко входу другого). Инверторы, входящие в эти элементы, образуют бистабильную ячейку, а элементы, выполняющие логическую операцию, – комбинационную схему. При смене состояния триггера возникает момент, когда оба инвертора оказываются в усилительном режиме, в схеме возникает положительная обратная связь и процесс переключения протекает под её действием (регенеративный процесс) очень быстро. Для уяснения работы схемы необходимо вспомнить функционирование элемента ИЛИ-НЕ. Исходя из этого, может быть составлена таблица переключений RS-триггера (табл. 5.1).

(выход каждого из них подключен ко входу другого). Инверторы, входящие в эти элементы, образуют бистабильную ячейку, а элементы, выполняющие логическую операцию, – комбинационную схему. При смене состояния триггера возникает момент, когда оба инвертора оказываются в усилительном режиме, в схеме возникает положительная обратная связь и процесс переключения протекает под её действием (регенеративный процесс) очень быстро. Для уяснения работы схемы необходимо вспомнить функционирование элемента ИЛИ-НЕ. Исходя из этого, может быть составлена таблица переключений RS-триггера (табл. 5.1).

| Таблица 5.1 | ||||

| R | S | Qn | Qn+1 | Вид сигнала |

| хранение | ||||

| уст. 1 | ||||

| уст. 0 | ||||

| X | запрет | |||

| X |

В таблице Qn – сигнал на выходе  в момент времени tn, Qn+1 –сигнал на выходе Q в момент времени tn+1, после воздействия указанных сигналов на входах. Последняя комбинация R = S = 1 является запрещенной, т. к. при этом на выходах Q и

в момент времени tn, Qn+1 –сигнал на выходе Q в момент времени tn+1, после воздействия указанных сигналов на входах. Последняя комбинация R = S = 1 является запрещенной, т. к. при этом на выходах Q и  устанавливается 0 и при переходе к режиму хранения R = S = 0 в какое состояние установится триггер (Q = 0 или Q = 1), – не определено. На основании таблицы переключений может быть записано алгебраическое уравнение, описывающее работу триггера:

устанавливается 0 и при переходе к режиму хранения R = S = 0 в какое состояние установится триггер (Q = 0 или Q = 1), – не определено. На основании таблицы переключений может быть записано алгебраическое уравнение, описывающее работу триггера:

.

.

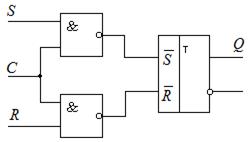

Если это уравнение перевести в базис И-НЕ –

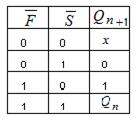

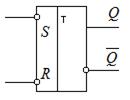

– и построить структурную схему, то получим RS-триггер с инверсными входами (рис. 5.4).

а б в

Рис. 5.4. RS-триггер с инверсными входами:

а – электрическая схема; б – таблица переходов; в – условное обозначение

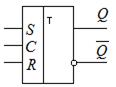

На основе этого триггера можно продемонстрировать схему триггера с синхронизацией уровня синхроимпульса (рис. 5.5).

а б

Рис. 5.5. Схема RS-триггера с синхронизацией высоким уровнем

синхроимпульса (а); условное обозначение (б)

При С = 0 на выходах входных элементов И-НЕ фиксируются высокие уровни, которые удерживают инверсный RS-триггер в исходном состоянии. Таким образом, блокируется прием входной информации. При С = 1 легко убедиться, что схема ведет себя как RS-триггер с прямыми входами.

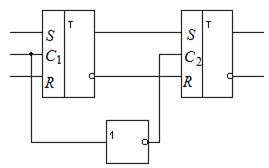

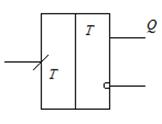

Организовать режим синхронизации перепадом синхроимпульса можно путем последовательного включения двух триггеров, тактируемых уровнем (рис. 5.6), такая структура называется двухступенчатой.

а б

Рис. 5.6. Схема RS-триггера, тактируемого срезом синхроимпульса (а);

условное обозначение (б)

При С1 = 1 входной триггер воспринимает входную информацию, а выходной блокирован (С2 = 0). В момент С1 = 0 (срез синхроимпульса) входной триггер блокируется, а выходной разблокируется (С2 = 1) и воспримет информацию, которая зафиксировалась во входном триггере в момент его блокировки.

5.1.2. D-триггер

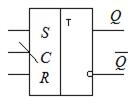

D-триггер – это синхронный триггер с одним информационным входом, предназначенным для задержки логического сигнала. Часто поэтому D-триггер называют триггером-задержкой. D-триггер повторяет значение сигнала, которое было установлено на входе триггера в предшествующий момент с задержкой максимум на один период (такт) синхроимпульса. Схема синхронизируемого уровнем D-триггера приведена на рис. 5.7. Уравнение, описывающее работу D-триггера,

,

,

при Cn = 1, Qn+1 = Dn+1 – повторяет входной сигнал, при C = 0, Qn+1=Qn – режим хранения. С использованием двухступенчатой структуры строятся D-триггеры, тактируемые срезом импульса. В таких триггерах часто делается еще один вход – вход разрешения V. В этом случае при V=1 структура работает как синхронный D-триггер, а при V=0 находится в режиме хранения (рис. 5.8).

|

|

| Рис. 5.7. Триггер, тактируемый уровнем по V входу DV-триггера | Рис. 5.8. Триггер, тактируемый уровнем по V входу DV-триггера |

5.1.3. JK-триггер

JK-триггер – это триггер с раздельными установочными входами (J®S, K®R). Схема JK-триггера приведена на рис 5.9. В отличие от

RS-триггера (см. рис. 5.5) в JK-триггере введены дополнительные связи выходов со входами через элементы И-НЕ. Это привело к тому, что при комбинации J = K = 1 триггер меняет свое состояние на противоположное, такая комбинация не является запрещенной. Работа JK-триггера отражена в таблице переключений (см. табл. 5.2) и описывается логическим уравнением  . Если взять элементы И-НЕ трехвходовые и третьи входы объединить (см. пунктир на рис. 5.9), то получится синхронизируемый уровнем JK-триггер. Как и другие типы триггеров по двухступенчатой структуре строятся JK-триггеры, синхронизируемые срезом,

. Если взять элементы И-НЕ трехвходовые и третьи входы объединить (см. пунктир на рис. 5.9), то получится синхронизируемый уровнем JK-триггер. Как и другие типы триггеров по двухступенчатой структуре строятся JK-триггеры, синхронизируемые срезом,

|

|

|

|

|

|

|

|  |

В сериях микросхем выпускаются все типы рассмотренных триггеров, синхронизируемых положительным перепадом, фронтом, срезом импульса синхронизации. Их графическое изображение представлено на рис. 5.2.

5.1.4. T-триггер

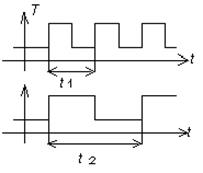

T-триггер имеет один информационный вход, переключение осуществляется перепадом входного сигнала. Таблицы состояний, графическое изображение, временные диаграммы приведены на рис. 5.10. Уравнение, описывающее работу T-триггера, –  . Как видно из временных диаграмм, T-триггер осуществляет деление частоты следования входных импульсов в два раза

. Как видно из временных диаграмм, T-триггер осуществляет деление частоты следования входных импульсов в два раза  , что определяет применение в ряде устройств.

, что определяет применение в ряде устройств.

а б в

Рис. 5.10. Асинхронный Т-триггер:

а – таблица состояний; б – условное обозначение;

в – временная диаграмма сигналов

|

|

соединен со входом D, то с приходом тактового импульса Qn+1=Qn, а в JK-триггере при J=K=1 будет изменяться состояние выхода на противоположное, и число импульсов на выходе будет в два раза меньше, т. е. такие структуры работают как T-триггеры. На рис. 5.12 показана возможность использования JK-триггера в качестве D-триггера. Таким образом, JK-триггер является универсальным.

соединен со входом D, то с приходом тактового импульса Qn+1=Qn, а в JK-триггере при J=K=1 будет изменяться состояние выхода на противоположное, и число импульсов на выходе будет в два раза меньше, т. е. такие структуры работают как T-триггеры. На рис. 5.12 показана возможность использования JK-триггера в качестве D-триггера. Таким образом, JK-триггер является универсальным.

В серийных триггерах для расширения их возможностей, кроме информационных и синхронизирующих входов, делаются установочные входы (R, S), они позволяют делать предварительную установку 0 или 1 на выходе  , причем, как правило, эти входы являются приоритетными. Кроме этого, реально действующий информационный вход в структуре триггера может быть конъюнкцией, дизъюнкцией или какой-либо функцией нескольких логических переменных, действующих на информационных входах, например: J=J1 × J2 × J3; K=K1 × K2 × K3 и т. п. Обозначение таких триггеров представлены на рис. 5.13.

, причем, как правило, эти входы являются приоритетными. Кроме этого, реально действующий информационный вход в структуре триггера может быть конъюнкцией, дизъюнкцией или какой-либо функцией нескольких логических переменных, действующих на информационных входах, например: J=J1 × J2 × J3; K=K1 × K2 × K3 и т. п. Обозначение таких триггеров представлены на рис. 5.13.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а б

Рис. 5.13 Триггеры с установочными входами:

а – D-триггер; б – универсальный JK-триггер

Триггер Шмитта

При передаче цифровых сигналов по линии связи из-за ограниченной полосы пропускания происходит затягивание фронтов импульсов, что может сделать их непригодными для нормального восприятия логическими элементами. С целью улучшения формы импульсов широко используются специальные формирователи – триггеры Шмитта. В них вводится положительная обратная связь, за счет которой такой элемент обладает гистерезисом – зоной нечувствительности.

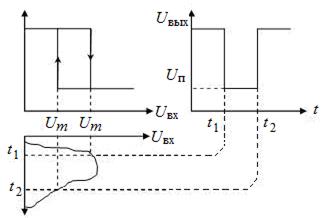

На рис. 5.14, а приведена типовая переходная характеристика триггера Шмитта, на которой показаны границы зоны нечувствительности – пороговые напряжения UП1 и UП2. На этом же рисунке приведен график, объясняющий восстановление формы сигнала.

Когда входной сигнал в момент времени  станет Uвх(t1)³UП1, триггер переключится из 1(

станет Uвх(t1)³UП1, триггер переключится из 1(  ) в 0(

) в 0(  ). Обратное переключение произойдет при Uвх(t2)³UП2.

). Обратное переключение произойдет при Uвх(t2)³UП2.

Обозначение триггера Шмита на схемах приведено на рис. 5.14, б.

а б

Рис. 5.14. Триггер Шмитта:

а – переходные характеристики триггера Шмитта; б – условное изображение

5.2. Цифровые счетчики импульсов

и делители частоты следования

Двоичные счетчики

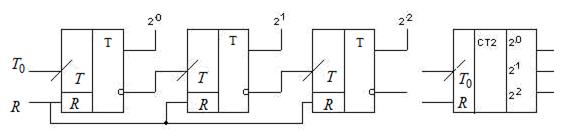

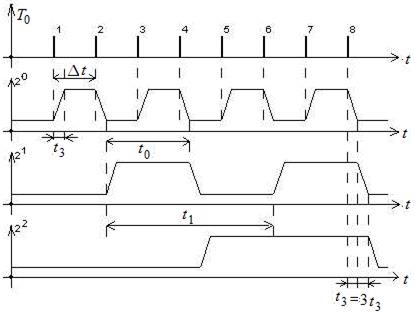

Двоичные счетчики – это последовательностные устройства, отображающие в выходном двоичном коде число поступивших на его вход импульсов. Двоичные счетчики строятся на n последовательно соединенных Т-триггерах, поэтому число всевозможных сочетаний состояний триггеров составит K=2n. Это значит, что счетчик может «сосчитать»

2n – 1 входных сигналов. Число K отражает информационную емкость двоичного счетчика и называется модулем счета. Первый импульс, пришедший после «заполнения» счетчика (когда исчерпаны все возможные состояния), автоматически сбрасывает счетчик в исходное нулевое состояние. Рассмотрим работу трехразрядного двоичного счетчика с помощью временных диаграмм (рис. 5.15).

а б

в

Рис. 5.15. Схема трехразрядного асинхронного суммирующего двоичного счетчика: а, б – условное обозначение; в – временные диаграммы

При рассмотрении диаграммы необходимо обратить внимание на то, что счетный вход каждого последующего триггера подключен к инвертирующему выходу предыдущего. Это означает, что положительный перепад на входе триггера, по которому он срабатывает, происходит при отрицательном перепаде по основному выходу предыдущего триггера. В диаграммах учтены задержки t3 (для простоты принятые одинаковыми), вызванные конечным временем переходного процесса триггера. По диаграммам легко убедиться, что значение двоичного кода на основных выходах триггеров соответствует числу пришедших импульсов (см. на диаграммном состоянии после 5-го и 7-го импульсов). С приходом 7-го импульса информационная емкость счетчика исчерпывается и 8-й импульс приводит к последовательному сбросу в нулевое состояние всех триггеров, который заканчивается через время  , равное сумме времен задержки каждого триггера. Это обстоятельство ограничивает частоту импульсов, т. е. скорость счета, т. к. необходимо выполнить условие

, равное сумме времен задержки каждого триггера. Это обстоятельство ограничивает частоту импульсов, т. е. скорость счета, т. к. необходимо выполнить условие

.

.

Такой счетчик называется асинхронным. С приходом каждого импульса число, отображаемое двоичным кодом, увеличивается на единицу, поэтому такой счетчик называется суммирующим.

Хорошо видно, что период следования импульсов с прямого выхода каждого последующего триггера в 2 раза больше, чем у предыдущего. Если снимать информацию, например, с выхода второго триггера, то частота следования импульса здесь будет в 4 раза ниже, чем у входных импульсов, т. е. счетчик может выполнять роль делителя частоты входных импульсов.

Ограничение скорости счета, вызванного у асинхронного счетчика последовательным переключением триггеров, можно устранить, если осуществлять одновременное переключение триггеров, которое реализуется в счетчиках с параллельным переносом (рис. 5.16).

Рис. 5.16. Счетчик с параллельным переносом

В этой схеме входы J и K объединены, и когда J=K=1, JK-триггер работает, как Т-триггер, а когда J=K=0, – находится в режиме хранения. С помощью элемента И осуществляется перенос информации в старший разряд. Быстродействие повышается за счет того, чтос приходом входного импульса одновременно срабатывают все триггеры.

Если вход последующего триггера (см. рис. 5.15) соединить с прямым выходом предыдущего, то такой счетчик становится вычитающим: число, записанное в виде исходного кода, будет с приходом каждого входного импульса уменьшаться на 1. Возможна реализация реверсивного счетчика, работающего по внешней команде, или в режиме суммирования, или в режиме вычитания.

Дата добавления: 2016-06-22; просмотров: 2943;