Индивидуальные задания

Задание 1. Нарисуйте схему дешифратора 6-64 на микросхемах ИД7.

Задание 2. Нарисуйте схему дешифратора 24-4 на микросхемах ИВ1.

Задание 3. Нарисуйте схему селектирования 16-ти разрядного кода.

7. МУЛЬТИПЛЕКСОРЫ, ДЕМУЛЬТИПЛЕКСОРЫ

Мультиплексоры

Мультиплексоры (английское Multiplexer) - это комбинационные устройства, предназначенные для коммутации одного из нескольких источников логических сигналов к одной выходной шине.

В цифровых устройствах часто возникает задача передачи цифровой информации от источников к одному приёмнику. Для этого на входе канала устанавливается устройство, называемое мультиплексором (МS), которое согласно коду адреса подключает к выходу один из источников информации.

Например, из четырёх источников D0, D1, D2 и DЗ, которые подключены к информационным входам мультиплексора, необходимо выбрать один. Для этого должен быть указан номер информационного входа. Обычно он задаётся двоичным кодом на управляющих входах мультиплексора.

Для МS с двумя информационными входами достаточно одного управляющего входа Х0 (Рис.7.1.).

|

| Рис.7.1 Схема мультиплексора на 2 входа (а) - логическая, (б) – обозначение |

Обычно мультиплексоры обозначаются так:

· МS2-1 - мультиплексор с двумя информационными входами на один выход;

· МS8-1 - мультиплексор с восемью информационными входами на один выход и т.п.

Функциональная схема мультиплексора, реализованная на дешифраторе, представлена Рис.7.3.

Данный мультиплексор имеет четыре входа информационных данных (D0, D1, D2 и DЗ) и управляется двухразрядным кодом Х1,Х2, который подается на вход дешифратора.

Дешифратор формирует единичный сигнал на том выходе, который соответствует управляющему коду, тем самым подавая на выход Y сигнал с выбранной входной шины. Например, если код, подаваемый на Х1Х2 равен 00, то будет выбран информационный вход D0.

|

| Рис. 7.3 Схема мультиплексора на 4 информационных входа построенная на дешифраторе |

Мультиплексоры могут быть собраны из простейших логических элементов И, ИЛИ, НЕ, дешифраторе и логических элементах или могут использоваться готовые мультиплексоры в виде интегральных микросхем.

Мультиплексоры бывают с выходом 2С и с выходом 3С. Выход 3С позволяет объединять выходы мультиплексоров с выходами других микросхем, а также получать двунаправленные и мультиплексированные линии.

Выходы мультиплексоров бывают прямыми и инверсными.

Некоторые микросхемы мультиплексоров имеют вход разрешения/запрета С (другое обозначение - S), который при запрете устанавливает прямой выход в нулевой уровень.

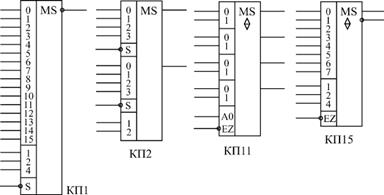

На Рис. 7.4 показаны для примера несколько микросхем мультиплексоров из состава стандартных серий.

В отечественных сериях мультиплексоры имеют код типа микросхемы КП. На схемах микросхемы мультиплексоров обозначаются буквами MS.

| Таблица 7.1 Таблица истинности 8-канального мультиплексора | |||||

| Входы | Выходы | ||||

| -EZ | Q | -Q | |||

| X | X | X | Z | Z |

Рис. 7.4. Примеры микросхем мультиплексоров

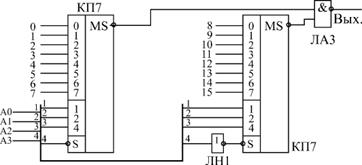

Микросхемы мультиплексоров можно объединять для увеличения количества каналов. Например, два 8-канальных мультиплексора легко объединяются в 16-канальный с помощью инвертора на входах разрешения и элемента 2И-НЕ для смешивания выходных сигналов (рис. 7.5). Старший разряд кода будет при этом выбирать один из двух мультиплексоров.

Рис. 7.5. Объединение мультиплексоров для увеличения количества каналов

Демультиплексоры

Демультиплексоры в функциональном отношении противоположны мультиплексорам. С их помощью сигналы одного информационного входа распределяются в требуемой последовательности по нескольким выходам.

Выбор нужной входной шины, как и в мультиплексоре, обеспечивается установкой соответствующего кода на адресных входах. При m адресных входах демультиплексор может иметь до 2m выходов.

|

| Рис.7.6 Схема демультиплексора на логических элементах |

Принцип работы демультиплексора поясним с помощью схемы на рис. 7.6, на которой обозначено: X-информационный вход, А-вход адреса, Y0, Y1-выходы.

Схема содержит два элемента И и один элемент НЕ. При А=0 сигнал информационного входа передаётся на выход Y0, а при А=1 - на выход Y1.

Демультиплексоры иначе называют рапределителями. На Рис. 7 7 представлена схема распределителя на базе дешифратора. В данной схеме входной сигнал D передается на один из 8 выходов Y в зависимости от управляющего кода подаваемого на входы Х1Х2.

|

| Рис.7.7 Схема демультиплексора на дешифраторе и логических элементах |

7.3. Контрольные вопросы

62. Что такое мультиплексор?

63. Поясните работу мультиплексора, схема которого представлена на Рис.7.3.

64. Поясните работу мультиплексора КП2.

65. Поясните работу мультиплексора КП11.

66. Что такое демультиплексор?

67. Поясните работу демультиплексора, схема которого представлена на Рис.7.5.

Дата добавления: 2021-12-14; просмотров: 502;