Многоразрядный компаратор

Многоразрядные компараторы обычно выполняют на базе одноразрядных с подключением дополнительных ЛЭ И и ИЛИ (для блокировки одноразрядных компараторов и объединения сигналов).

При этом используется принцип последовательного сравнения разрядов многоразрядных чисел, начиная с их старших разрядов, так как уже на этом этапе, если Х1m ≠ Х2m, задача может быть решена однозначно, и сравнение следующих за старшими разрядов не потребуется.

На практике широко применяются "неполные" компараторы в которых реализуется одна или две операции на сравнение кодов (Y=, Y> , Y=и Y> и др.). Для выполнения этих операций можно использовать отдельные фрагменты из схем на Рис.8.3, или построить специальные схемы, которые в ряде случаев могут быть упрощены.

|

|

| (а) | (б) |

| Рис.8.3. Схема компаратора на ЛЭ 2И-НЕ (а), диаграмма его работы (б) |

На схемах компараторы кодов обозначаются двумя символами равенства: "= =".

Код типа микросхемы компаратора кода в отечественных сериях — СП.

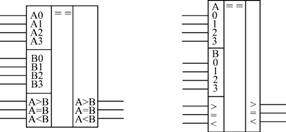

Примером такой микросхемы может служить СП1 - 4-х разрядный компаратор кодов, сравнивающий величины кодов и выдающий информацию о том, какой код больше, или о равенстве кодов (Рис. 8.4).

Помимо восьми входов для сравниваемых кодов (два 4-х разрядных кода, обозначаемых А0...А3 и В0...В3), компаратор СП1 имеет три управляющих входа для наращивания разрядности (А>B, A<B, A=B) и три выхода результирующих сигналов (А>B, A<B, A=B).

Для удобства на схемах управляющие входы и выходы иногда обозначают просто ">", "<" и "=".

Нулевые разряды кодов (А0 и В0) -младшие, третьи разряды (А3 и В3) - старшие.

Рис. 8.4. 4-х разрядный компаратор кодов СП1 (два варианта обозначения)

Если микросхемы компараторов кодов каскадируются (объединяются) для увеличения числа разрядов сравниваемых кодов, то надо выходные сигналы микросхемы, обрабатывающей младшие разряды кода, подать на одноименные входы микросхемы, обрабатывающей старшие разряды кода (Рис. 8.5).

Рис. 8.5. Каскадирование компараторов кодов

дно из основных применений компараторов кодов состоит в селектировании входных кодов.

На рис. 8.6 показано применение компараторов SN74ALS521 для селектирования 16-разрядных кодов. Инверсный сигнал с выхода первой микросхемы подается на инверсный вход разрешения второй микросхемы, выходной сигнал которой (отрицательный) говорит о совпадении входного и эталонного 16-разрядных кодов.

Рис. 8.6. Селектирование 16-разрядных кодов

8.3. Контрольные вопросы

68. Что такое компаратор?

69. Объясните работу схемы одноразрядного компаратора изображенного на Рис.2.1.

Дата добавления: 2021-12-14; просмотров: 642;