Многоразрядный последовательный сумматор

(Проектирование арифметических устройств цифровой обработки сигналов с использованием САПР Quartus II и ее библиотеки мегафункций: Метод. указания к лабораторной работе № 20 по дисциплинам "Цифровые устройства и микропроцессоры" (часть 1), "Вычислительная техника и информационные технологии" для студентов специальностей 071900, 200700, 200800, 200900, 201100 всех форм обучения / НГТУ; Сост.: А.Д.Плужников, Н.Н.Потапов, А.А.Цветков. Н.Новгород, 2005. 22 с.)

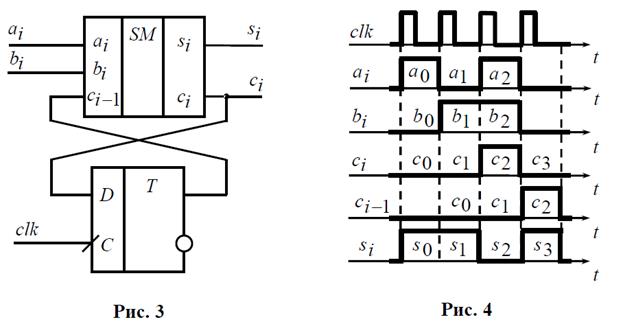

Сумматор для последовательных операндов содержит один одноразрядный сумматор, обрабатывающий поочередно разряды операндов, начиная с младших разрядов. Т. е. в каждом такте (периоде некоторой последовательности синхроимпульсов) суммируются соответствующие два разряда слагаемых. Так, вначале при сложении разрядов a0 и b0 , на двух выходах одноразрядного сумматора появятся младший разряд результата и сигнал переноса, который необходимо сохранить в течение такта. В следующем такте этот сигнал переноса должен складываться с разрядами a1 и b1, которые к данному времени поступят на входы одноразрядного сумматора. И т. д. Упрощенную схему сумматора для последовательных операндов можно представить, как показано на рис. 3. Кроме одноразрядного сумматора, она содержит D-триггер для хранения сигнала переноса, тактируемый фронтами положительных синхроимпульсов clk .

На рис. 4 показаны временные диаграммы для схемы (рис. 3), соответствующие вычислению суммы 101+110=1011

Недостатком такого сумматора является большое время суммирования ( n тактов для n -разрядных операндов). Достоинства: возможность последовательной (потоковой) обработки операндов и небольшие аппаратные затраты

Устройства выполняющие операцию вычитания

Как и устройства сложения, устройства, выполняющие операцию вычитания, делятся на: полувычитатели, полные вычитатели, многоразрядные вычитатели.

Полувычитатель

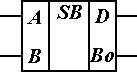

Полувычитатель—комбинационная логическая схема, имеющая два входа и два выхода. Полувычитатель позволяет вычислять разность A-B, где A и B — это одноразрядные двоичные числа (А-уменьшаемое, B-вычитаемое) при этом результатом будут два бита D и Bo (D — это бит разности , а Bo— бит заёма)

Рисунок 2.36 - Электрическая принципиальная схема полувычитателя

Рисунок 2.37 - Условно графическое обозначение полувычитателя

На основании схемы составим таблицу истинности

Таблица2.18.

| Входы | Выходы | ||

| A | B | Di | B0 |

| Уменьшаемое | Вычитаемое | Разность | Заем |

Полный вычитатель

При вычитании многоразрядных двоичных чисел нужно принимать во внимание заем "единиц" в более старших разрядах. Такую операцию осуществляет полный вычитатель. Рассмотрим схему полного вычитателя с использованием двух полувычитателей.

Рисунок 2.38 - Электрическая принципиальная схема полного вычитателя с использованием полувычитателей

Рисунок 2.39 - Условно графическое обозначение полного вычитателя.

Пользуясь рисунком 2.38 составим таблицу истинности полного вычитателя

Таблица 2.19.

| Входы | Выходы | |||

| A | B | Bi | Di | B0 |

| A-B-Bi | Разность | Заем |

Дата добавления: 2021-09-07; просмотров: 778;