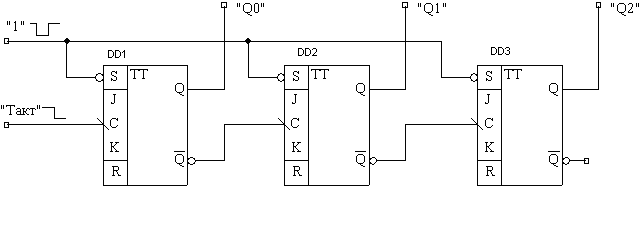

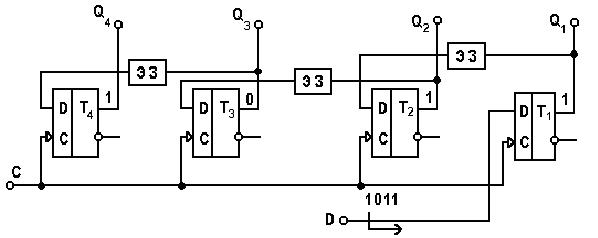

Вычитающий последовательный счётчик

Триггеры данного счетчика срабатывают по заднему фронту. Для реализации операции вычитания счетный вход старшего разряда подключается к инверсному выходу соседнего младшего разряда. Предварительно триггеры устанавливают в состояние лог.1 (111). Работу данного счетчика показывает временная диаграмма на рис. 4.

Рис. 1 Последовательный вычитающий счетчик

Рис. 2 Временная диаграмма последовательного вычитающего счетчика

Сумматор - устройство, выполняющее операции арифметического сложения над двоичными числами. Где-то здесь рассматривалисьматематические операции над двоичными числами, где говорилось о том, что сумма двух нулей есть нуль, сумма нуля и единицы есть единица, сумма двух единиц есть нуль. Одноразрядный цифровой сумматор имеет три входа: два входа слагаемых и вход переноса (от предыдущего сумматора). При этом правила сложения чуток усложняются. Одноразрядный сумматор обозначается так:

Рис. 1 - Одноразрядный цифровой сумматор

Сумматор имеет входы А и В - слагаемые, С - вход переноса, S - выход суммы, Р - выход переноса. Табличка истинности:

| Входы | Выходы | |||

| Слагаемые | Вход переноса | Сумма | Выход переноса | |

| А | B | C | S | P |

На выходе S представляется сумма сложения трех переменных - А, В, С. При переполнении сумматора, т. е. когда в результате сложения формируется единица в старшем разряде выходного числа, на выходе переноса Р формируется уровень лог. 1, который подается на вход переноса С следующего сумматора. В принципе, старшим разрядом суммы является выход переноса Р. В целом работу сумматора полностью иллюстрирует таблица. Из таких одноразрядных сумматоров составляются многоразрядные сумматоры (обычно 4-х разрядные), которые бывают последовательного и параллельного действия. Сумматоры последовательного действия обладают более низким быстродействием.

Вычитатель

Со сложением двоичных чисел все понятно. Как же осуществить на микросхемах-сумматорах операции вычитания двоичных чисел? Допустим необходимо выполнить вычитание: 11 - 5 = 6. В двоичных эквивалентах произведем операцию сложения числа 1011 (число 11) иобратный код числа 5, равный 1010 (прямой код 0101). Итак:

Если отбросить единицу в старшем (пятом) разряде, то получится код 0101, который соответствует числу 5. Но это не число 6. Значит к результату необходимо прибавить единицу. Кстати, операция увеличения какого-либо числа на единицу называется инкрементом, уменьшения на единицу - декрементом. На рисунке 2 показана схема четырехразрядного вычитателя.

Рис. 2 - 4-х разрядное устройство вычитания

Инверторы микросхемы DD1 формируют обратный код числа В. Число А поступает на входы А1-А4 сумматора DD2, обратный код числа В - на входы В1-В4 сумматора. На вход переноса Р0 подан уровень лог. 1, что обеспечивает прибавление к результату сложения единицы (т. е. инкремент результата). На выходах S1-S4 сумматора в итоге получается разность между числами А и В.

Десятичный сумматор

Чаще приходится суммировать десятичные числа. Ниже на рисунке приведена схема сумматора двоично-десятичных чисел на основе двоичных сумматоров.

Рис. 3 - Сумматор двоично-десятичных чисел

Операцию сложения выполняет сумматор DD1. При сумме большей или равной десяти на выходе микросхемы DD2, которая является схемой сравнения входов, формируется сигнал переноса Р10. На второй вход (Y1-Y4) микросхемы DD2 подается двоичный эквивалент числа 9 (1001). Сумматор DD3 осуществляет десятичную коррекцию результата суммирования. При отсутствии сигнала переноса на выходе микросхемы DD3 повторяется код числа, который был на выходе DD1, поскольку на входы В поданы лог. 0. При наличии сигнала переноса Р10=1 на входах В2-В3 устанавливаются лог. 1, что соответствует коду числа 6. Допустим есть числа А=8 и В=4. На выходе сумматора DD1 появляется код числа 12 (8+4=12). На выходе DD2 формируется сигнал переноса, сумматор DD3 выполняет операцию 12+6=18. Числу 18 соответствует код 10010. На выходах S сумматора DD3 устанавливается код 0010 (собственный перенос микросхемы DD3 не учитывается). Поскольку на выходе Р10 число 10, на выходах сумматора число 2 (0010), то в результате получается число 12.

Сумматор-накопитель

Интересными свойствами обладает сумматор-накопитель, показанный на рисунке 4.

Рис. 4 - Сумматор-накопитель

На рисунке показан простейший сумматор-накопитель. На один вход сумматора подается число К, а на второй - число с выхода регистра. В начале работы регистр обнуляется (сброс). Если на входы В сумматора DD1 подать некоторое число К, то при подаче импульса на вход С регистра (такт) в него запишется число К (в начальный момент на выходе регистра лог.0). Это же число К попадет на входы А сумматора и по следующему такту в регистр запишется уже число 2К, которое опять попадет на входы А сумматора. На выходе сумматора появится число 3К и по следующему такту запишется в регистр и т. д. То есть, в сумматоре-накопителе постепенно нарастает число. Когда в сумматоре-накопителе накопленное число превышает его объем, равный 2n-1, на выходе переноса появляется сигнал лог. 1, а на выходах S число nK-2n.

Применение таких сумматоров весьма разнообразно. Если вместо регистра установить ОЗУ (это делается в многоканальных системах), тогда такой узел становится важнейшей частью микропроцессора. Посмотрим на эти свойства сумматора-накопителя. Поскольку сигнал переноса сумматора появляется через W=2n/K тактовых импульсов, то такой сумматор является обратным преобразователем входного числа К в число W. Это число можно подсчитать на счетчике. Ну а если выразить частоту появления имульсов переноса через число К, получится вот это:

Это значит, что получается преобразователь кода числа К в частоту импульсов. Такой преобразователь можно использовать в электронных музыкальных инструментах (ЭМИ), всяких звонках и т. п.

С помощью сумматоров-накопителей можно производить умножение числа на некоторый постоянный коэффициент, можно забабахать квадратичный накопитель и еще много всякой хренотени.

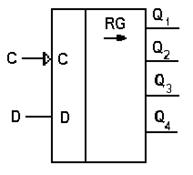

Регистрами называют логические устройства, предназначенные для запоминания и хранения цифровых кодов. Построение регистров выполняют на триггерах. Операцию передачи цифрового кода в регистр и из регистра можно осуществлять последовательно и параллельно.

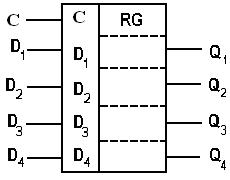

На рис.9.13 изображено условное обозначение и схема четырёхразрядного регистра параллельного действия, построенного на синхронных D – триггерах. Регистр имеет четыре входа D1÷D4информационных и один синхронизирующий вход С.

B исходное нулевое состояние логических сигналов на всех выходах Q1÷ Q4 ,

регистр устанавливается при подаче на синхронизирующий вход Ссигнала лог.1 и на все информационные входы D сигнала лог “0”. Запись двоичного числа производится при одновременной подаче на информационные входы D1÷D4 кода числа.

Рис.9.13. Условное обозначение и схема четырёхразрядного регистра параллельного действия

Триггеры, на информационные входы которых подаются сигналы лог. 1 , переводятся в состояния 1, остальные останутся в состоянии 0. Записанное число считывается с выходов Q1÷Q4.

Для запоминания числа и сдвига влево используется схемы сдвигающего регистра. На рис.9.14 приведено условное обозначение и логическая схема сдвигающего регистра. Регистры такого типа используют в качестве преобразователей последовательного кода в параллельный код.

Регистр имеет два входа: на вход С поступают динамические импульсы сдвига, являющимися положительными импульсами, изменяющимися во времени; вход D является информационным входом.

При записи числа в сдвигающий регистр цифровой двоичный код подается на информационный вход D триггера Т1, начинается со старшего разряда. При этом положительные импульсы сдвига поступают на счётные входы С триггеров.

Работу регистра рассмотрим на примере записи числа 1011. С приходом импульса сдвига на вход С и подаче на вход D единицы старшего разряда числа, триггер Т1переводится в состояние 1 (Q1). В регистре используются элементы задержки ЭЗ, которые осуществляют задержку во времени перемещения сигнала с одного триггера на другой. При подаче очередного импульса сдвига на вход С и подаче на вход D второго разряда (нуля) числа, на выходе Q1 появится 0 , а 1 из триггера Т1 через элементЭЗ переместится в триггер Т2. С приходом очередного импульса сдвига на вход С и подаче на вход D третьего разряда (единицы) числа, триггер Т1 установится в 1 и т.д. Путём последовательной подачи кодов чисел на вход D и импульсов сдвига на вход С, число записывается в регистр.

Дата добавления: 2021-04-21; просмотров: 745;