По архитектуре простейшего функционального преобразователя.

По архитектуре простейшего функционального преобразователя различают 6 типов.

|

Рисунок 3.1 - Классификация СБИС ПЛ

Первые в историческом смысле СБИС ПЛ – это ПЗУ, в которых выделяют постоянные запоминающие устройства ППЗУ (PROM), репрограммируемые запоминающие устройства РПЗУ (EPROM), электрические репрограммируемые ЭППЗУ (EEPROM). ПЗУ имеет структуру функционального преобразователя, в котором можно реализовать m независимых логических функций от n переменных причем, m – разрядность шины данных ПЗУ, n – разрядность шины адреса ПЗУ.

СБИС следующего поколения ПЛМ (программируемые логические матрицы) (PLA), а так же ПЛК (программируемые логические контроллеры) (PLS). Структура матрицы ПЛМ состоит из дешифратора D и шифратора S. Причем и дешифратор, и шифратор являются программируемыми.

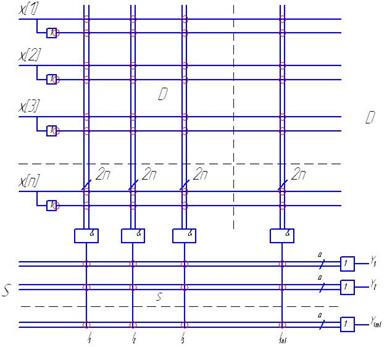

Рисунок 3.2 - Архитектура функционального преобразователя СБИС ПЛМ.

Для обеспечения возможности реализации не только комбинационных, но и последовательных схем, на выходе шифратора добавляется триггер. Такие БИС называются программируемым логическим контроллером. Так как все логические функции представляются в дизъюнктивной нормальной форме (в форме суммы произведений), то матрица ИЛИ оказывается разряженной и занятая ей часть кристалла используется не полностью.

Следующим этапом развития СБИС ПЛ является появление СБИС программируемой матричной логики. В них дешифратор является программируемым, а шифратор имеет фиксированную структуру. Такие БИС получили название PAL, а если на выходе таких схем присутствуют регистры, то они называются GAL. Архитектура СБИС ПМЛ положена в основу программируемых логических устройств ПЛУ или PLD.

Рассмотрим структуру простейшего функционального преобразователя СБИС ПЛУ.

Рисунок 3.3 - Архитектура простейшего функционального преобразователя СБИС ПЛУ

В состав функционального преобразователя входят: дешифратор D в виде программируемой матрицы И, матрица размещения результатов функции R, шифратор S с элементом ИЛИ, инвертор, выполненный на сумматоре по модулю 2 (элемент «исключающий ИЛИ»), синхронный триггер и мультиплексор, позволяющие выбрать асинхронный или синхронный режим простейшего функционального преобразователя.

В настоящее время получили развитие другие архитектуры ПФП. Например табличные архитектуры, которые используют для формирования логических функций таблицы перекодировок Look Up Table, а так же архитектура SLC (Simple logic cell), объединяющая разнообразные архитектуры СБИС ПЛ, и использующая комбинационные схемы для реализации логических функций.

Дата добавления: 2021-09-07; просмотров: 656;