Формы описания логических элементов

Всего существует 7 базовых логических элементов, реализующих 4 логические функции (НЕ, ИЛИ, И, исключающее И).

БУЛЬ (Boole) Джордж (2 ноября 1815, Линкольн, Великобритания - 8 декабря 1864, Баллинтемпль, Ирландия), английский математик и логик, один из основоположников математической логики. Разработал алгебру логики (булеву алгебру) («Исследование законов мышления», 1854), основу функционирования цифровых компьютеров.

Джордж Буль родился в бедной рабочей семье. Первые уроки математики получил у отца и, хотя посещал местную школу, в общем его можно считать самоучкой. В 12 лет он уже знал латынь, затем овладел греческим, французским, немецким и итальянским языками. В 16 лет уже преподавал в деревенской школе, а в 20 открыл собственную школу в Линкольне. В редкие часы досуга зачитывался математическими журналами Механического института, интересовался работами математиков прошлого - Ньютона, Лапласа, Лагранжа, проблемами современной алгебры.

Начиная с 1839 года, Буль стал посылать свои работы в новый Кембриджский математический журнал. Его первая работа «Исследования по теории аналитических преобразований» касалась дифференциальных уравнений, алгебраических проблем линейной трансформации и концепции инвариантности. В своем исследовании 1844 года, опубликованном в «Философских трудах Королевского общества», он коснулся проблемы взаимодействия алгебры и исчисления. В том же году молодой ученый был награжден медалью Королевского общества за вклад в математический анализ.

Вскоре после того, как Буль убедился, что его алгебра вполне применима к логике, в 1847 году он опубликовал памфлет «Математический анализ логики», в котором высказал идею, что логика более близка к математике, чем к философии. Эта работа была чрезвычайно высоко оценена английским математиком Августом Де Морганом. Благодаря этой работе Буль в 1849 году получил пост профессора математики Куинз-колледжа в графстве Корк, несмотря на то что он даже не имел университетского образования.

В 1854 году он опубликовал работу «Исследование законов мышления, базирующихся на математической логике и теории вероятностей». Работы 1847 и 1854 годов дали рождение алгебре логики, или булевой алгебре. Буль первым показал, что существует аналогия между алгебраическими и логическими действиями, так как и те, и другие предполагают лишь два варианта ответов — истина или ложь, нуль или единица. Он придумал систему обозначений и правил, пользуясь которыми можно было закодировать любые высказывания, а затем манипулировать ими как обычными числами. Булева алгебра располагала тремя основными операциями - И, ИЛИ, НЕ, которые позволяли производить сложение, вычитание, умножение, деление и сравнение символов и чисел. Таким образом, Булю удалось подробно описать двоичную систему счисления. В своей работе «Законы мышления» (1854) Буль окончательно сформулировал основы математической логики. Он также попытался сформулировать общий метод вероятностей, с помощью которого из заданной системы вероятных событий можно было бы определить вероятность последующего события, логически связанного с ними.

В 1857 году Буль был избран членом Королевского общества. Его работы «Трактат о дифференциальных уравнениях» (1859) и «Трактат о вычислении предельных разностей» (1860) оказали колоссальное влияние на развитие математики. В них нашли свое отражение наиболее важные открытия Буля.

Идеи Буля нашли применение в таких областях, о которых он не мог и мечтать - в использующих двоичный код цифровых компьютерах и в телефонной связи.

В качестве математического аппарата для описания цифровых систем используется Булева алгебра или алгебра логика.

Булевой алгеброй называется непустое множество  с двумя бинарными операциями (конъюнкции - логического И), (дизъюнкции - логического ИЛИ), унарной операцией (аналог отрицания) и двумя выделенными элементами: 0 (или Ложь) и 1 (или Истина).

с двумя бинарными операциями (конъюнкции - логического И), (дизъюнкции - логического ИЛИ), унарной операцией (аналог отрицания) и двумя выделенными элементами: 0 (или Ложь) и 1 (или Истина).

Для реализации булевых функций применяются базовые логические элементы. На них строятся все известные цифровые схемы

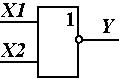

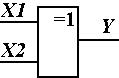

Таблица 2.4

| Логическая функция | Условное графическое обозначение | Булева функция | Таблица истинности | ||

| Входы | Выход | ||||

| X | Y | ||||

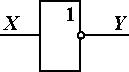

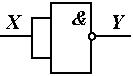

| НЕ |

|

| |||

| X1 | X2 | Y | |||

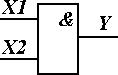

| И |

|

| |||

| И-НЕ |

|

| |||

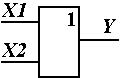

| ИЛИ |

|

| |||

| ИЛИ-НЕ |

|

| |||

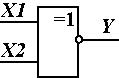

| Исключающее ИЛИ |

|

| |||

| Исключающее ИЛИ-НЕ |

|

| |||

Все логические элементы располагаются внутри микросхем. Для их работы необходимо подать питание на микросхему. Для этого на микросхеме существуют специальные выводы.

2.3.2. Универсальный характер логического элемента И-НЕ

С помощью достаточного количества логических элементов И-НЕ можно реализовать любую логическую функцию.

Таблица 2.5.

| Логическая функция | Условно графическое обозначение | Схема с использованием только логического элемента И-НЕ |

| Инвертор, НЕ |

|

|

| И |

|

|

| ИЛИ |

|

|

| ИЛИ-НЕ |

|

|

| Исключающее ИЛИ |

|

|

| Исключающее ИЛИ-НЕ |

|

|

2.3.3. Логические элементы с числом входов больше двух

Помимо двухвходовых логических элементов широко применяются логические элементы с числом входов больше 2. Рассмотрим трехвходовый элемент И (3И). На рисунке 2.6 справа.

Рисунок 2.6 - Трехвходовый элемент И (справа)и его схема на двухвходовых элементах И (слева).

Нетрудно получить булево выражение для трехвходового элемента У=Х1·Х2·Х3

Таблица 2.7.

Таблица истинности:

| X1 | X2 | X3 | Y |

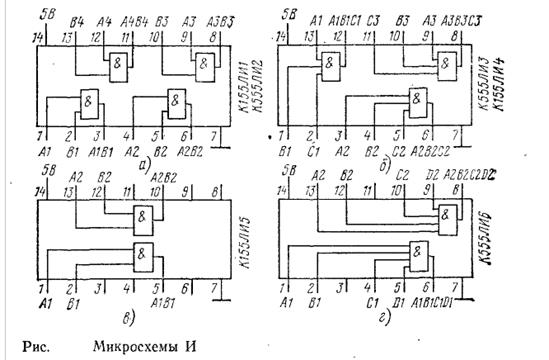

Трехвходовый элемент И реализован внутри микросхем К155ЛИ3, К155ЛИ4

2.3.4. Интегральные схемы

Все логические элементы физически располагаются внутри интегральных схем (микросхем). Рассмотрим, например, микросхемы реализующие логическую функцию И серии 155: К155ЛИ1, К155ЛИ2, К155ЛИ3, К155ЛИ4, К155ЛИ5, К155ЛИ6.

Рисунок 2.7 - Размещение логических элементов внутри корпусов микросхем.

Как видим, к 14 ножке микросхем прикладывается питающее напряжение +5В, к 7 ножке микросхем – напряжение 0В, остальные ножки задействованы для выводов элементов И. На электрических принципиальных схемах ножки питания могут не показывать, но это не значит, что питание не требуется подводить, как и любые другие электронные устройства микросхемы требуют питания.

2.3.5. Конструирование схем по таблице истинности

Рассмотрим задачу: пусть требуется открыть кодовый электрический замок кодом 111 или кодом 010. При этом будем считать, что если на выходе схемы 0, то замок закрыт, а если 1, то открыт. Составим таблицу истинности.

Таблица 2.8.

| X1 | X2 | X3 | Y (состояние замка) |

В основе схемы лежит элемент ИЛИ два входа, которого соответствуют двум кодам открывающим замок. Проверка кодов осуществляется трехвходовыми элементами И.

Рисунок 2.8 - Схема кодового замка

2.4. Классификация цифровых схем

Схемы с логическими элементами могут принадлежать к одному из 2 видов: комбинационные и последовательностные.

К комбинационным, относятся те, у которых значение выхода не зависит от значений входа в предыдущий момент времени, т.е. значение сигнала на выходе полностью определяется текущим состоянием входов. К ним относят: мультиплексоры и демультиплексоры, шифраторы и дешифраторы, сумматоры и вычитатели, преобразователи входов и т.д.

К последовательностным, относят такие, у которых значение на выходе зависит не только от текущего состояния входа и выхода, но и от состояния входов и выходов в предыдущий момент времени. К ним относят все схемы на триггерах, счетчики.

2.5. Комбинационные схемы

2.5.1. Мультиплексор

Мультиплексор – это цифровой многопозиционный переключатель, имеющий несколько сигнальных входов Xn-X0 и один выход Y. Для управления положением переключателя имеется несколько адресных входов Am-A0. Эквивалентная схема мультиплексора на 4 канала представлена на рисунке2.9. Подавая двоичный код на адресные входы, можно выбрать номер сигнального входа, который подключается к выходу. Схему мультиплексора на 4 канала c использованием логических элементов представлена на рисунке 2,4.

а.

а.

|  с.

с.

|

б.

б.

|

Рисунок 2.9 - Мультиплексор: а- эквивалентная схема; b-Условно графическое обозначение; с- Электрическая принципиальная схема на логических элементах

Таблица истинности составим на базе схемы мультиплексора на логических элементах.

Таблица 2.9.

| А1 | А0 | Вход подключаемый к выходу (положение переключателя) |

| Х1 | ||

| Х2 | ||

| Х3 | ||

| Х4 |

Булево выражение соответствующее мультиплексору

2.5.2. Демультиплексор

Демультиплексор – это цифровой многопозиционный переключатель, имеющий один сигнальный вход X и несколько сигнальных выходов Y0-Yn. Для управления положением переключателя имеется несколько адресных входов Am-A0. Эквивалентная схема демультиплексора на 4 канала представлена на рисунке 2.10. Принципиальная электрическая схема демультиплексора на 4 канала и его условно графическое обозначение представлены на рисунке 2.10. Двоичная последовательность передается с сигнального входа на сигнальный выход, соответствующий номеру на адресном входе.

а.

а.

|  с.

с.

|

б.

б.

|

Рис. 2.10 Демультиплексор

Рисунок 2.10 - Демультиплексор: а- эквивалентная схема; b-Условно графическое обозначение; с- Электрическая принципиальная схема на логических элементах

2.5.3 Дешифратор

Дешифратор (ДШ) преобразует двоичный код на входах в активный сигнал на том выходе, номер которого равен десятичному эквиваленту двоичного кода на входах. В полном дешифраторе количество выходов m = 2n, где n - число входов. В неполном ДШ m < 2n.

В качестве дешифратора можно использовать демультиплексор если на его вход X постоянно подать логическую единицу, а двоичный код подавать на адресные входы. Таблица истинности такой схемы будет выглядеть следующим образом.

Таблица2.10.

| A1 | A0 | Y3 | Y2 | Y1 | Y0 |

2.5.4 Дешифратор двоичного кода в сигнал семисегментного индикатора

Семисегментные индикаторы широко применяютсядля отображения информации

Внешний вид семисегментного индикатора поясняет рисунок. Каждый сегмент имеет свое буквенное обозначение от a до g. если используется десятичная запятая, то она соответствует сегменту h

Рисунок. 2.11 - Семисегментный индикатор

Каждый из сегментов индикатора представляет собой отдельный светоизлучающий диод, например сегмент f

Рисунок 2.12 - Сегмент f

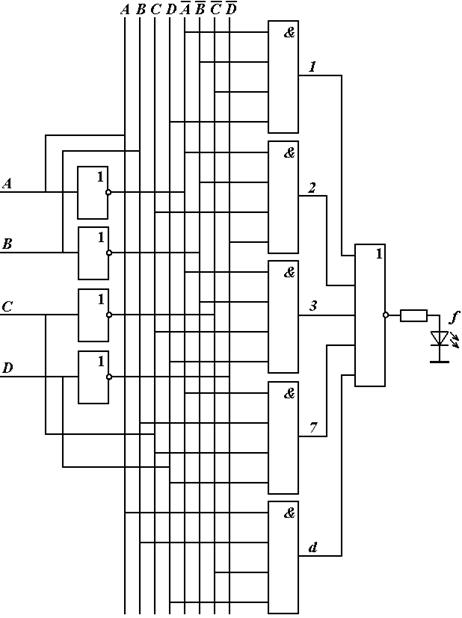

При подаче логической 1 сегмент горит, при подачи логического нуля сегмент не горит. Cконструируем часть схемы отвечающей за сегмент f. Для этого выпишем все числа отображаемые на семисегментном индикаторе.

Рисунок 2.13 - числа отображаемые на семисегментном индикаторе

Как видно из рисунка сегмент f не горит в 5 случаях соответствующих цифрам: 1,2,3,7,d.

Схема соответствующая данному сегменту может быть представлена на рисунке 2.15.

Отечественной промышленностью производятся дешифраторы двоичного кода в сигнал семисегментного индикатора КР514ИД1 и КР514ИД2. Эти дешифраторы предназначены для преобразования двоичного кода, подаваемого на их входы в код семисегментных светодиодных индикаторов. Обе микросхемы идентичны и различаются только тем, что КР514ИД1 предназначена для работы с индикаторами с общим катодом, а КР514ИД2 для индикаторов с общим анодом. Кроме того, микросхема КР514ИД1 содержит встроенные токоограничивающие резисторы на выводах a,b,c,d,e,f,g.

Условно графическое изображение микросхемы, цоколёвка и расположение сегментов на индикаторах показаны на Рисунке 2.14. Недостатком можно считать, что они не могут воспроизводить числа в шестнадцатиричной системе счисления, а ограничиваются только цифрами от 0 до 9.

Рисунок 2.14 - условно графическое обозначение дешифратора КР514ИД1

Рисунок 2.15 - Схема реализации дешифратора для сегмента f семисегментного индикатора.

2.6. Последовательные схемы

Основу таких схем составляют триггеры

Триггер – простейшее последовательностное устройство, которое может длительно находиться в одном из нескольких возможных устойчивых состояний и переходить из одного в другое под воздействием входных сигналов. Как правило таких состояний два 0 и 1 но иногда бывают триггеры с большим числом устойчивых состояний троичный триггер, декатрон;

Триггерные схемы классифицируют по следующим признакам:

· способу приёма логических сигналов;

· функциональным возможностям;

· принципу построения;

· числу устойчивых состояний (обычно устойчивых состояний два, реже - больше, см. троичный триггер, декатрон);

числу уровней - два уровня (высокий, низкий) в двухуровневых элементах, три уровня (положительный, ноль, отрицательный) в трёхуровневых элементах

По способу приема логических сигналов различают синхронные, асинхронные и смешанные триггерные схемы.

Асинхронный триггер изменяет своё состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб», «такт». Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С. Статические триггеры воспринимают информационные сигналы при подаче на вход С уровня логической единицы (прямой вход) или логического нуля (инверсный вход). Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С - вход) или от 1 к 0 (инверсный динамический С-вход). Статические триггеры в свою очередь подразделяют на одноступенчатые (однотактные) и двухступенчатые (двухтактные). В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ.

По структурному построению — однотактные (триггеры защёлки), двухтактные и триггеры с динамическим управлением. По способу реакции на помехи — прозрачные и непрозрачные. Непрозрачные, в свою очередь, делятся на проницаемые и непроницаемые. По функциональному назначению — RS, D, JK, T, RR, SS, EE, DV.

Используются в основном в вычислительной технике для организации компонентов вычислительных систем: в процессорах, регистров, счётчиков, ОЗУ.

По функциональным возможностям триггеры разделяют на следующие классы:

с раздельной установкой состояния 0 и 1 (RS-триггеры). Если триггер является синхронным — добавляется вход синхронизации C.;

универсальные (JK-триггеры);

с приёмом информации по одному входу D (D-триггеры, или триггеры задержки);

со счётным входом Т (Т-триггеры).

Каждый тип триггера имеет собственную таблицу работы (таблицу истинности). Выходное состояние триггера обычно обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) или после подачи сигнала (t+1).

Если триггер синхронный, то существует также дополнительный вход синхронизации. Для того, чтобы такой триггер учёл информацию на синхронных входах, на входе синхронизации необходимо сформировать активный фронт (обычно положительный фронт).

Рассмотрим некоторые из применяемых типов триггеров.

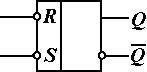

2.6.1 Асинхронный RS – триггер

Условно графическое обозначение RS триггера представлено на рисунке 2.16.

Рисунок 2.16 - Условно графическое обозначение RSтриггера.

Вход S (от английского SET) предназначен для установки триггера в единичное состояние. Вход S – инверсный, т.е. при подаче на него логического 0 триггер устанавливается в единичное состояние. Вход R (от английского RESET) предназначен для установки триггера в нулевое состояние (для сброса триггера).

Два выхода (прямой и инверсный) всегда принимают противоположное состояние. Состояние двух единиц или двух нулей на выходах называется запрещенным.

Рассмотрим схему триггера на элементах И-НЕ.

Рисунок 2.17 - Схема триггера на элементах И-НЕ

По данной схеме составим таблицу истинности:

Таблица 2.11.

| Режим работы | Входы | Выходы | |||

|

| Q |

| Влияние на выход Q | |

| Запрещенное состояние | Запрещено - не используется | ||||

| Установка 1 | Для установки Q в 1 | ||||

| Установка 0 | Для установки Q в 0 | ||||

| Хранение | БИ | БИ | Зависит от предыдущего состояния |

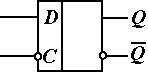

2.6.2 Синхронный D-триггер

D-триггер (D от англ. delay - задержка) - запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

Условно графическое обозначение D триггера представлено на рисунке 2.18 а его одна из возможных схем реализации с использованием логических элементов на рисунке 2.19

Рисунок 2.18 - Условно графическое обозначение Dтриггера.

Рисунок 2.19 - Вариант схемы D триггера с использованием логических элементов.

Вход D – вход данных, С – вход синхроимпульсов, R – вход асинхронного сброса, S – вход асинхронной установки 1, Q, Q – прямой и инверсный выходы.

Составим таблицу истинности D триггера

Таблица 2.12

| D | C |

|

| Q |

| Режим работы |

| Х | Х | асинхронная установка 1 | ||||

| асинхронная установка 0 | ||||||

| хранение | ||||||

| синхронная установка 1 | |||||

| хранение | ||||||

| синхронная установка |

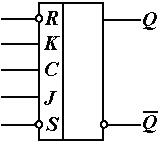

2.6.3 JK — триггер

Это универсальный триггер, обладающий характеристиками всех других триггеров.

JK-триггер работает также как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump - прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill - убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становиться равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггер, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К. Также JK триггер может иметь входы асинхронной установки S и сброса R.

Рисунок 2.20 - Условно графическое обозначение D триггера

Таблица истинности JK триггера

Таблица истинности JK триггера

|

| C | J | K | Q |

| Режим работы |

Х

Х

Х

| Х Х Х | Х Х Х | б/и | б/и | Асинхронная установка 1 асинхронная установка 0 запрещенный режим хранение синхронная установка 1 синхронная установка 0 переключение |

Режим переключение состоит в том, что состояние на выходах  и

и  изменяется на противоположное при подаче синхроимпульса.

изменяется на противоположное при подаче синхроимпульса.

2.6.4 Т – триггер.

Т-триггер по каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер может строиться как на JK, так и на D-триггерах.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена.

Рисунок 2.21 - T триггер на JK и D триггере

Таблица истинности Т триггера может быть представлена в виде

Таблица 2.14.

| С | T | Q |

Как видно из таблицы истинности временная диаграмма работы T триггера

Рисунок 2.22 - Временная диаграмма работы T триггера.

2.7 Двоичные счетчики

Счётчик - устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на T-триггерах. Основной параметр счётчика - модуль счёта - максимальное число импульсов, которое может быть сосчитано счётчиком. Как правило, модулем счета является степень двойки: 2n, где n - число разрядов счетчика. Счётчики обозначают через СТ (от англ. counter).

Классификация счетчиков:

По способу запуска:

1) синхронные

2) асинхронные

В синхронных счетчиках входной сигнал подается на синхронизирующие входы триггеров одновременно во все разряды, т.е. все триггеры переключаются одновременно. В асинхронных сигнал последовательно «проталкивается» с выхода младшего разряда на старший разряд.

Счетчики также делят на:

1) суммирующие

2) вычитающие

3) реверсивные

Суммирующие счетчики считают от 0 до максимального числа, а вычитающие наоборот. Реверсивные могут считать как в одну так и в другую сторону.

Счетчики бывают:

1) со сквозным переносом

2) с остановкой счета

Счетчики со сквозным переносом считают до максимального числа, далее сбрасываются в 0 и опять считают до максимального числа. Счетчики с остановкой счета после достижения модуля счета перестают считать импульсы

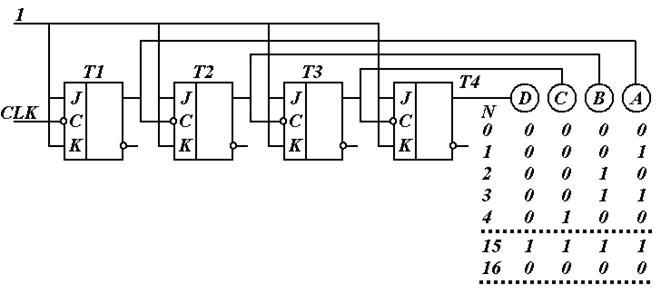

Рассмотрим четырехразрядный асинхронный счетчик со сквозным переносом на 4-х JK – триггерах.

Схема счетчика представлена на рисунке 2.23

Рисунок 2.23 - Схема счетчика и его таблица истинности

Работа счетчика происходит следующим образом. Все триггеры T1-T4 находятся в состоянии переключения, поскольку на их входы JK подана логическая 1. В начальный момент времени все триггеры сброшены и на их выводах DCBA (1 строчка таблицы истинности) присутствует логический ноль. При подаче на вход CLK (от англ. Clock) тактового импульса N=1. Переключается только первый триггер Т1. Поскольку входы C триггеров являются инверсными переключение осуществляется при переходе от 1 к 0. Остальные триггеры не переключаются. При подаче на вход тактового импульса N=2. Переключается первый триггер Т1. На его выходе формируется переход от 1 к 0, который переключает триггер T2. дальнейший процесс удобно рассмотреть на временной диаграмме работы представленной на рисунке 2.24.

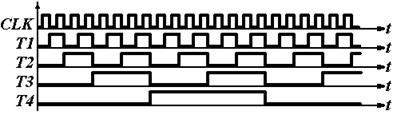

Рисунок 2.24 - Временные диаграммы работы счетчика

Как видно из временной диаграммы каждый следующий триггер переключается с вдвое меньшей частотой. Тактовый импульс в асинхронном счетчике подается только на триггер T1, остальные триггеры подключаются последовательно. Как видно из схемы переключение триггеров осуществляется неодновременное, например триггер Т2 может переключиться только после того как переключился триггер Т1, а триггер T3 может переключиться только после того как переключился триггер Т2. Каждый последовательный триггер осуществляет задержку переключении всего счетчика на собственное время переключения (как правило 10-30нс). Таким образом, при увеличении разрядности увеличивается время переключения счетчика, а следовательно уменьшается тактовая частота импульсов, которые способен подсчитать счетчик. Такого недостатка лишены синхронные счетчики.

Рассмотрим трехразрядный синхронный счетчик на JK – триггерах.

Принципиальная схема счетчика представлена на рисунке 2.25

В начальный момент времени все триггеры сброшены. На входах JK триггера Т1 присутствует логическая 1 поэтому он работает в режиме переключения. Триггеры Т2 и Т3 работают в режиме хранения. Таким образом, при подаче первого тактового импульса переключится только триггер Т1. Единица на выходе триггера Т1 подается на входы JK триггера Т2, следовательно, триггер Т2 переходит в режим переключения и по второму тактовому импульсу переключаются уже оба триггера Т1 и Т2. Дальнейшую работу легко понять из таблицы истинности приведенной на рисунке 2.25 при этом; П означает, что триггер находится в режиме переключения; Х означает, что триггер находится в режиме хранения.

Рисунок 2.25 - Схема синхронного счетчика и таблица истинности

Регистры

(Автор Белов А. В. http://www.mirmk.net/content/view/28/28/)

Регистры в цифровой и микропроцессорной технике - это устройства хранения информации. Любая информация в микропроцессорной технике кодируется и хранится в виде двоичного числа. Двоичное число состоит из некоторого количества двоичных разрядов. Регистр должен обеспечить возможность записи и хранения на протяжении всего времени работы микропроцессорной системы, всех разрядов двоичного числа. А так же возможность считывания значений всех разрядов в любое время. Регистры бывают параллельные и последовательные.

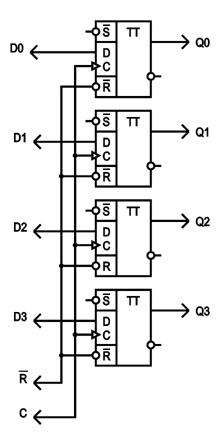

На рисунке изображена схема простейшего четырех разрядного параллельного регистра и его условное обозначение на схеме.

Рисунок 2.26 - Схема регистра на D триггерах

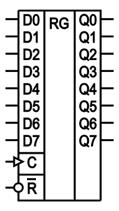

Рисунок 2.27 - Условно графическое обозначение

Как мы видим, регистр построен на основе четырех D-триггеров входы синхронизации, которых соединены вместе. На входы данных (D0 - D3) поступает двоичное число, которое необходимо записать в регистр. На вход С схемы подается тактовый сигнал. По заднему фронту сигнала двоичное число запишется в регистр. Каждый разряд запишется в свой D-триггер и тут же появится на выходах регистра (Q0 - Q3). Вход R служит для начального сброса всех триггеров регистра (то есть перевода в нулевое состояние).

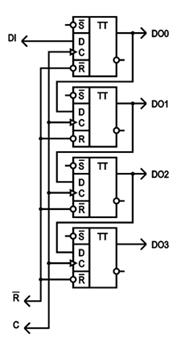

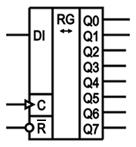

Рассмотрим схему внутреннего устройства и условное обозначение простейшего последовательного четырех разрядного регистра:

Рисунок 2.28 - Схема последовательного регистра (треугольные входы убрать)

Рисунок 2.29 - Условно графическое обозначение последовательного регистра.

Этот регистр так же построен на основе D-триггеров. Однако триггеры в этой схеме соединены по-другому. Выход одного триггера подключен к входу последующего. Схема имеет один информационный вход. На этот вход последовательно, разряд за разрядом, подается двоичное число. Для каждого очередного двоичного разряда, на вход синхронизации (С) подается тактовый импульс. По заднему фронту этого импульса очередной разряд числа записывается в младший разряд сдвигового регистра (выход Q0). Одновременно старое содержимое всего регистра сдвигается на один разряд в сторону старших разрядов. Так старое содержимое Q0записывается в следующий по очереди D-триггер (выход Q1). Содержимое Q1 переписывается в Q2. А разряд Q2 переписывается в Q3. Содержимое последнего триггера в цепочке никуда не переписывается и просто теряется. В результате входное четырехразрядное число, после четырех тактов записи последовательно записывается в регистр. Этот процесс поясняет таблица2.15

Вход R так же, как и в предыдущем случае, предназначен для начального сброса всех триггеров регистра в нулевое состояние.

Таблица 2.15.

Запись цифры A в шестнадцатеричной или числа 10 в десятичной системе счисления в четырехразрядный последовательный регистр.

| № Т.И. | DI | R | Q0 | Q1 | Q2 | Q3 |

| X | ||||||

Основное применение последовательного регистра - преобразование последовательного кода в параллельный. Например, клавиатура компьютера соединена с компьютером по последовательному каналу. Специализированный процессор, который стоит в клавиатуре, передает коды нажатых клавиш всего по одному проводу, последовательно, бит за битом. Этот провод называется - линия данных. При этом по второму проводу, который называется линией синхронизации, он передает тактовые импульсы. На каждый бит да<

Дата добавления: 2021-09-07; просмотров: 750;