ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

ТРИГГЕРЫ

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами.

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами.

В интегральной микросхемотехнике триггеры выполняют либо на основе логических интегральных элементов, либо как завершенный функциональный элемент в виде микросхемы.

Интегральные триггеры характеризуются большим разнообразием. Их отличают функциональный признак, определяющий поведение триггера при воздействии сигнала управления, а также используемый способ управления. По функциональному признаку различают триггеры типов R-S, D, T, J-K и др. По способу управления триггеры подразделяют на асинхронные и тактируемые. В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информационный вход. В тактируемых триггерах помимо информационных входов имеется вход тактовых импульсов. Их переключение производится только при наличии разрешающего, тактирующего импульса.

Триггеры применяют при построении более сложных функциональных устройств: счетчиков импульсов, регистров и т. д.

4.1.1. R-S-триггеры.В зависимости от способа управления различают асинхронные и тактируемые R-S-триггеры.

Асинхронные R-S-триггеры являются простейшими, однако они получили широкое распространение в импульсной и цифровой технике. В частности, они служат основой триггеров других типов и требуют для своего построения два двухвходовых логических элемента типа И – НЕ или ИЛИ – НЕ.

| tn | tn+1 | |

S S

|  R R

| Q n+1 |

| Q n | ||

| X |

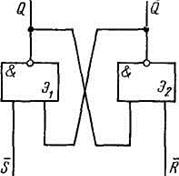

На рис. 4.1. приведена структурная схема асинхронного триггера на логических элементах И – НЕ. Схема имеет два выхода: Q – прямой, Q – инверсный.

На рис. 4.1. приведена структурная схема асинхронного триггера на логических элементах И – НЕ. Схема имеет два выхода: Q – прямой, Q – инверсный.

|

|

Рис. 4.1.

Асинхронный R-S-триггер, как и триггер любого другого типа, характеризуется двумя состояниями: логической «1» и логического «0». Состоянию логической «1» соответствует Q= 1, Q = 0; состоянию логического «0» – Q = 0, Q= 1.

Асинхронный R-S-триггер, как и триггер любого другого типа, характеризуется двумя состояниями: логической «1» и логического «0». Состоянию логической «1» соответствует Q= 1, Q = 0; состоянию логического «0» – Q = 0, Q= 1.

По информационному входу S производится установка триггера в состояние логической «1», а по информационному входу R – установка (перевод) триггера в исходное состояние логического «0». Этому соответствуют сокращенные обозначения входов и название триггера: S – set (установка), R – reset (возвращение в исходное состояние).

Принцип действия триггера определяется поведением в нем элементов И – НЕ. Он иллюстрируется таблицей переходов триггера (рис. 4.1 б), где указаны значения входных сигналов S и R внекоторый момент времени tnи состояние триггера (по значению его прямого выхода) в следующий момент времени tn+1 после прихода очередных импульсов.

При S = 0 и R = 1 подтверждается предшествующее состояние, если триггер находился в состоянии логической «1» (Q= 1, Q= 0), и переход его в состояние «1», если триггер до этого находился в состоянии «0». Пусть Q = 1,Q=0. Если S = 0, то независимо от значения сигнала на втором входе элемента Э1 И – НЕ Q= 1. На обоих входах Э2 присутствуют логические «1». Это обеспечивает Q = 0. При Q = 0, Q= 1сигнал S = 0 вызывает переключение элемента Э1 в состояние логической «1» и соответственно элемента Э2 в состояние логического «0» вследствие появления на его левом входе логической «1».

При S = 0 и R = 1 подтверждается предшествующее состояние, если триггер находился в состоянии логической «1» (Q= 1, Q= 0), и переход его в состояние «1», если триггер до этого находился в состоянии «0». Пусть Q = 1,Q=0. Если S = 0, то независимо от значения сигнала на втором входе элемента Э1 И – НЕ Q= 1. На обоих входах Э2 присутствуют логические «1». Это обеспечивает Q = 0. При Q = 0, Q= 1сигнал S = 0 вызывает переключение элемента Э1 в состояние логической «1» и соответственно элемента Э2 в состояние логического «0» вследствие появления на его левом входе логической «1».

При противоположном соотношении сигналов (S =1, R = 0) происходит либо подтверждение нулевого состояния триггера (Q = 0, Q = 1), либо его переключение из состояния «1» в состояние «0».

При противоположном соотношении сигналов (S =1, R = 0) происходит либо подтверждение нулевого состояния триггера (Q = 0, Q = 1), либо его переключение из состояния «1» в состояние «0».

Значениям сигналов на входе S = R = 1 соответствует сохранение триггером предыдущего состояния. Пусть до появления такой комбинации сигналов на входах в триггере была записана логическая «1» (Q = 1, Q = 0). При наличии S = R = 1 имеем на обоих входах элемента Э2 по логической «1». Это обусловливает Q = 0. На правом входе элемента Э1 будет логический «0», что дает Q = 1.

Значениям сигналов на входе S = R = 1 соответствует сохранение триггером предыдущего состояния. Пусть до появления такой комбинации сигналов на входах в триггере была записана логическая «1» (Q = 1, Q = 0). При наличии S = R = 1 имеем на обоих входах элемента Э2 по логической «1». Это обусловливает Q = 0. На правом входе элемента Э1 будет логический «0», что дает Q = 1.

При комбинации S = R = 0 один из входов обоих элементов И – НЕ имеет логический «0», Q = Q = 1. Такие значения выходных сигналов триггера не соответствуют ни его состоянию «1» (Q = 1, Q = 0), ни его состоянию «0» (Q = 0, Q = 1). Триггер принимает неопределенное состояние. По указанной причине комбинация сигналов на входе S = R = 0 для асинхронного R-S-триггера на элементах И – НЕ является запрещенной. Рассмотренной схеме триггера соответствуют временные диаграммы. Они построены с учетом таблицы переходов. Состояние логической «1» (Q = 1) триггер принимает при S = 1.

При комбинации S = R = 0 один из входов обоих элементов И – НЕ имеет логический «0», Q = Q = 1. Такие значения выходных сигналов триггера не соответствуют ни его состоянию «1» (Q = 1, Q = 0), ни его состоянию «0» (Q = 0, Q = 1). Триггер принимает неопределенное состояние. По указанной причине комбинация сигналов на входе S = R = 0 для асинхронного R-S-триггера на элементах И – НЕ является запрещенной. Рассмотренной схеме триггера соответствуют временные диаграммы. Они построены с учетом таблицы переходов. Состояние логической «1» (Q = 1) триггер принимает при S = 1.

На рис. 4.2, а приведена структурная схема тактируемого R-S-триггера на элементах И – НЕ. Переключения в тактируемом триггере возможны, как отмечалось, лишь при наличии разрешающего сигнала (импульса тактов), подаваемого на вход Т. Эта особенность схемы связана с применением на входах асинхронного R-S -триггера двух управляющих элементов И – НЕ (Э3, Э4). Принцип действия схемы иллюстрируют временные диаграммы, приведенные на рис.4, б.

Рис. 4.2. Структурная схема тактируемого R-S-триггера (а)

и его временные диаграммы (б)

При нулевых значениях сигналов на всех трех входах (S = R = Т = 0) на выходах элементов Э3,Э4 действует логическая «1». Состояние R-S-триггера на элементах Э1, Э2остается без изменения (интервал времени t0– t1);на рис. 1, б принято за нулевое. Состояние триггера сохраняется и при S = 1, R = Т = 0 (интервал времени t1– t2). В момент времени t2 сигналы логической «1» совпадают по входам S и T (S = Т = 1, R = 0). На выходе элемента Э3действует логический «0», а на выходе элемента Э4– логическая «1», что приводит к переключению триггера на элементах Э1, Э2в состояние «1».

Очередное переключение триггера возможно лишь в момент времени t4,когда R = Т = 1, S = 0, а также в момент времени t5, когда S = Т = 1, R = 0. Комбинация S = R=T= 1 в триггере должна быть исключена, так как на выходах элементов Э3, Э4 при этом присутствовал бы одновременно сигнал «0», что, как известно, запрещено для асинхронного R-S -триггера на логических элементах И-НЕ.

Тактируемые R-S-триггеры нашли широкое применение в устройствах цифрового действия для хранения двоичной информации в течение времени, большего ее существования в исходном источнике, например для хранения промежуточной информации, передаваемой от счетчиков импульсов и регистров.

4.1.2. D-триггеры. D-триггеры имеют один информационный вход. Состоянию логической «1» соответствует единица на входе триггера, а состоянию логического «0» – нулевой уровень входного сигнала.

На практике наибольшее применение получили тактируемые (одно-тактные и двухтактные) D-триггеры. Их обозначение обусловлено свойством сохранять состояние логической «1» после снятия входного сигнала до прихода очередного тактового импульса (delay – задержка).

D-триггеры широко используют при построении регистров.

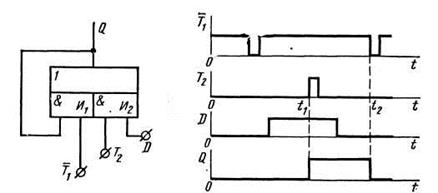

На рис. 4.3, а приведена структурная схема однотактного D-триггера, выполненная на основе асинхронного R-S-триггера.

Временные диаграммы, поясняющие его принцип действия, изображены на рис. 4.3, б.

Рис. 4.3. Структурная схема тактируемого D-триггера (а)

и его временные диаграммы (б)

Предположим, что к моменту прихода входного сигнала D-триггер находился в состоянии логического «0» (Q = 0, Q = 1). В интервале времени t1 – t2, когда действует входной сигнал D, состояние триггера не изменяется, так как при этом Т = 0 и сигналы на входах элементов Э1, Э2 S = R = 1. Действие сигнала Т = 1 в момент времени t2 обусловливает на выходе элемента Э3 S = 0, а на выходе элемента Э4 R=1. Это приводит к переключению триггера в состояние логической «1» (Q = 1, Q = 0). Состояние «1» триггера не изменится до момента времени t4, так как при Т = 0 сигналы на входах асинхронного триггера S = R = 1. Появление в момент времени t4 сигнала Т = 1 дает R = 0, S = 1 и вызывает переключение триггера в состояние логического «0».

Предположим, что к моменту прихода входного сигнала D-триггер находился в состоянии логического «0» (Q = 0, Q = 1). В интервале времени t1 – t2, когда действует входной сигнал D, состояние триггера не изменяется, так как при этом Т = 0 и сигналы на входах элементов Э1, Э2 S = R = 1. Действие сигнала Т = 1 в момент времени t2 обусловливает на выходе элемента Э3 S = 0, а на выходе элемента Э4 R=1. Это приводит к переключению триггера в состояние логической «1» (Q = 1, Q = 0). Состояние «1» триггера не изменится до момента времени t4, так как при Т = 0 сигналы на входах асинхронного триггера S = R = 1. Появление в момент времени t4 сигнала Т = 1 дает R = 0, S = 1 и вызывает переключение триггера в состояние логического «0».

Принцип действия двухтактных D-триггеров подобен однотактным. Отличие заключается в том, что запись информации в них производится с участием одной последовательности тактовых импульсов, а считывание – с участием другой последовательности тактовых импульсов. Обе последовательности тактовых импульсов имеют фазовый сдвиг в 180°.

Двухтактные D-триггеры просто реализуются на комбинированных логических элементах.

На рис. 4.4, а приведена структурная схема однофазного (имеющего один выход) двухтактного D-триггера на элементе 2И – ИЛИ. Запись единицы в триггере осуществляется при одновременном действии сигналов Т2, D на входах элемента И2, а считывание производится по входу Т1 элемента И1. Процессы в схеме иллюстрируют временные диаграммы рис. 4.4, б.

|

Рис. 4.4. Структурная схема однофазного двухтактного

D-триггера (а)и его временные диаграммы (б)

До момента времени t1триггер находится в состоянии «0». При наличии в момент времени t1сигналов на обоих входах элемента И2происходит изменение состояния триггера (Q= 1). Это состояние поддерживается в триггере до момента времени t2 логической «1» на обоих входах элемента И1.

В момент времени t2 Т1 = 0, на выходе элемента И1действует логический «0», что вызывает переход триггера в исходное нулевое состояние.

В момент времени t2 Т1 = 0, на выходе элемента И1действует логический «0», что вызывает переход триггера в исходное нулевое состояние.

4.1.3. Т-триггер. Характерным свойством Т-триггера является его переключение в противоположное состояние с приходом каждого очередного входного импульса. Ввиду широкого применения в счетчиках импульсов (рис. 4.5) его часто называют триггером со счетным запуском.

Триггеры Т-типа выполняются на базе двух асинхронных R-S-триггеров (М-S-схема), один из которых называют основным (master – основной), адругой – вспомогательным (slave – вспомогательный) (триггеры ОТ и ВТ на рис. 4.5, а).

Рис. 4.5. Структурная схема Т-триггера

По М-S -схеме реализуются несколько вариантов Т-триггера. Особенностью рассматриваемой структурной схемы является наличие в ней дополнительного инвертора (элемент Э5),управляющего ВТ, В связи с этим ее называют часто схемой с инвертором.

Последовательность переключения асинхронных R-S-триггеров, входящих в Т-триггер, такая. На этапе фронта входного импульса переключается основной триггер, а по окончании длительности tи входного импульса (на этапе среза) – вспомогательный триггер (рис. 4.5,б). Указанная особенность отражается в другом названии схемы – триггер с внутренней задержкой (Tt).

Режим счетного запуска Т-триггера определяет указанные ниже особенности, учитываемые при его построении.

В схеме должны быть созданы условия для сохранения нового состояния после переключения триггера входным импульсом. При этом должна обеспечиваться необходимая направленность переключения: если триггер находится в состоянии «1», то входной импульс переводит его в состояние «0», и наоборот. Предположим, что после переключения оба триггера установлены в состояние «1». Состояние «1» основного триггера поддерживается единичными сигналами с выходов элементов Э8,Э9. Значения «1»на выходах этих элементов создаются ввиду того, что сигнал на одном из их входов Т = 0. Состояние «1» вспомогательного триггера обусловливается тем, что при Т= 0 на обоих входах элемента Э3действует логическая «1», а на выходе элемента Э3– логический «0». Избирательность переключения Т-триггера достигается наличием связей элементов Э8, Э9 с выходами вспомогательного триггера. Если до прихода очередного входного импульса Т в триггере записана «1», то по цепям обратных связей на входе элемента Э9 будет логическая «1», а на выходе элемента Э8– логический «0». При поступлении входного импульса Т элемент Э9переходит в состояние «0», вызывая переключение в нулевое состояние основного триггера, а после окончания входного импульса в состояние «0» переключается и вспомогательный триггер. Принцип действия схемы поясняют временные диаграммы, приведенные на рис. 4.5, б.

К моменту времени t1триггеры ОТ и ВТ находятся в состоянии «1». В момент времени t1 T = 1 и триггер ОТ переходит в состояние «0», однако при этом на выходе элемента Э5действует логический «0», а на выходах элементов Э3 и Э4 – по логической «1». Таким образом, на этапе действия входного импульса состояние ВТ не изменяется. В момент времени t2 Т = 0 и на выходе элемента Э5действует логическая «1». На обоих входах элемента Э4 присутствует «1», сигнал на выходе элемента Э4 становится равным нулю, что вызывает переключение в состояние «0» и вспомогательного триггера.

С момента времени t3действие входного импульса направлено на переключение триггера в состояние «1». Вначале (в момент времени t3) в состояние «1» переключается триггер ОТ,а затем (в момент времени t4) и триггер ВТ. В последующем процессы в схеме повторяются.

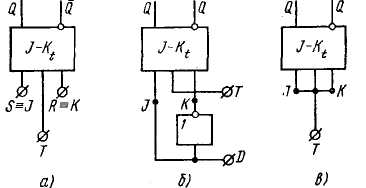

4.1.4. J-K-триггер. J-K-триггер получают на основе Т-триггера (рис. 4.6, а) путем использования в его входных цепях трехвходовых элементов И – НЕ, позволяющих иметь два дополнительных входа J и K (пунктирные линии на рис. 4.6, а). Наличие двух дополнительных входов расширяет функциональные возможности триггера, в связи с чем J-K -триггер называют универсальным. При соответствующем подключении входов J-K-триггер, в частности, может выполнять функции R-S, D- и Т-триггеров (рис. 4.6, а – в).

|

Рис. 3.5 Схемы триггеров, реализуемых на основе J-K-триггера

J-K-триггер, так же как и все типы триггеров, получаемые на его основе, является триггером с внутренней задержкой: в момент действия импульса Т информация записывается в основной триггер, а после его окончания состояние основного триггера передается во вспомогательный. Наличие в работе схемы внутренней временной задержки, определяемой длительностью тактовых импульсов, часто отражается символом«t» в обозначении J-K-триггера и триггеров, выполненных на его основе: J-Kt, R-St, Dt, Tt.

R-St- и Dt-триггеры являются тактируемыми (рис. 4.6, а, б); R-St-триггер (рис. 4.6, а) получают подачей на вход J сигнала S; а на вход K – сигнала R; D-триггер создается введением инвертора в цепь входа K (рис. 4.6, б). Триггер со счетным запуском (Tt-триггер) реализуется подключением входов J и K к входу Т.

Лекция №5

Дата добавления: 2017-05-02; просмотров: 1643;