Средства сопряжения

Обычная компьютерная система малого или среднего размера состоит из микросхемы процессора, микросхем памяти и нескольких контроллеров ввода-вывода. Все эти микросхемы соединены шиной. Мы уже рассмотрели память, центральные процессоры и шины. Теперь настало время изучить микросхемы ввода-вывода. Именно через эти микросхемы компьютер обменивается информацией с внешними устройствами.

3.1.Микросхемы ввода-вывода

В настоящее время существует множество различных микросхем ввода-вывода. Новые микросхемы появляются постоянно Из наиболее распространенных можно назвать UART, USART, контроллеры CRT (CRT - электронно-лучевая трубка), дисковые контроллеры и PIO. UART (Universal Asynchronous Receiver Transmitter - универсальный асинхронный приемопередатчик) - это микросхема, которая может считывать байт из шины данных и передавать этот байт по битам на линию последовательной передачи к терминалу или получать данные от терминала. Скорость работы микросхем UART различна: от 50 до 19 200 бит/с; ширина знака от 5 до 8 битов; 1,1,5 или 2 стоповых бита. Микросхема может обеспечивать проверку на четность или на нечетность, контроль по четности может также отсутствовать, все это находится под управлением программ.

Микросхема USART (Universal Synchronous Asynchronous Receiver Transmitter- универсальный синхронно-асинхронный приемопередатчик) может осуществлять синхронную передачу, используя ряд протоколов. Она также выполняет все функции UART. Поскольку микросхемы UART мы уже рассматривали в главе 2, сейчас в качестве примера микросхемы ввода-вывода мы возьмем параллельный интерфейс.

3.2.Микросхемы PIO

Типичным примером микросхемы PIO (Parallel Input/Output - параллельный

ввод-вывод) является Intel 8255A (рис. 3.51). Она содержит 24 линии ввода-вывода и может сопрягаться с любыми устройствами, совместимыми с TTL-схемами (например, клавиатурами, переключателями, индикаторами, принтерами) Программа центрального процессора может записать 0 или 1 на любую линию или считать входное состояние любой линии, обеспечивая высокую гибкость. Микросхема PIO часто заменяет целую плату с микросхемами МИС и СИС (особенно во встроенных системах).

Центральный процессор может конфигурировать микросхему 8255А различными способами, загружая регистры состояния микросхемы, и мы остановимся на некоторых наиболее простых режимах работы. Можно представить данную микросхему в виде трех 8-битных портов А, В и С. С каждым портом связан 8-битный регистр. Чтобы установить линии на порт, центральный процессор записывает 8-битное число в соответствующий регистр, и это 8-битное число появляется на выходных линиях и остается там до тех пор, пока регистр не будет перезаписан. Чтобы использовать порт для входа, центральный процессор просто считывает соответствующий регистр.

Другие режимы работы предусматривают квитирование связи с внешними

устройствами. Например, чтобы передать данные устройству, микросхема 8255А может представить данные на порт вывода и подождать, пока устройство не выдаст сигнал о том, что данные получены и можно посылать еще. В данную микросхему включены необходимые логические схемы для фиксирования таких импульсов и передачи их центральному процессору.

Из рис. 3.51 мы видим, что помимо 24 выводов для трех портов микросхема

8255А содержит восемь линий, непосредственно связанных с шиной данных,

линию выбора элемента памяти, линии чтения и записи, две адресные линии и линию для переустановки микросхемы. Две адресные линии выбирают один из четырех внутренних регистров, три из которых соответствуют портам А, В и С.

Четвертый регистр - регистр состояния. Он определяет, какие порты используются для входа, а какие для выхода, а также выполняет некоторые другие функции. Обычно две адресные линии соединяются с двумя младшими битами адресной шины.

3.3.Декодирование адреса

До настоящего момента мы не останавливались подробно на том, как происходит выбор микросхемы памяти или устройства ввода-вывода. Пришло время этоузнать. Рассмотрим простой 16-битный встроенный компьютер, состоящий из центрального процессора, стираемого программируемого ПЗУ объемом 2Кх8 байт для хранения программы, ОЗУ объемом 2Кх8 байт для хранения данных и микросхемы PIO. Такая небольшая система может встраиваться в дешевую игрушку или простой прибор. Вместо стираемого программируемого ПЗУ может использоваться

обычное ПЗУ.

Микросхема PIO может быть выбрана одним из двух способов: как устройство ввода-вывода или как часть памяти. Если микросхема нам нужна в качестве устройства ввода-вывода, мы должны выбрать ее, используя внешнюю линию шины, которая показывает, что мы обращаемся к устройству ввода-вывода, а не к памяти.

Если мы применяем другой подход, так называемый ввод-вывод с распределением памяти, мы должны присвоить микросхеме 4 байта памяти для трех портов и регистра управления. Наш выбор в какой-то степени произволен. Мы выбираем ввод-вывод с распределением памяти, поскольку этот метод наглядно иллюстрирует некоторые интересные проблемы сопряжения.

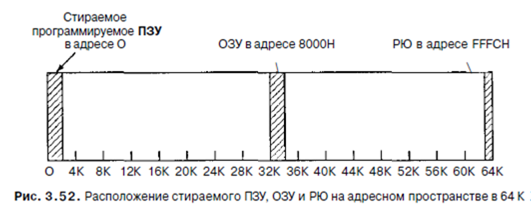

Стираемому программируемому ПЗУ требуется 2 К адресного пространства,

ОЗУ требуется также 2 К адресного пространства, а микросхеме РЮ нужно 4 байта. Поскольку в нашем примере адресное пространство составляет 64 К, мы должны выбрать, где поместить данные три устройства. Один из возможных вариантов показан на рис. 3.52. Стираемое программируемое ПЗУ занимает адреса до 2 К, ОЗУ занимает адреса от 32 К до 34 К, а РЮ - 4 старших байта адресного пространства, от 65532 до 65535. С точки зрения программиста не важно, какие именно адреса использовать, однако для сопряжения это имеет большое значение. Если бы мы обращались к РЮ через пространство ввода-вывода, нам не потребовались бы адреса памяти (зато понадобились бы четыре адреса пространства ввода-вывода).

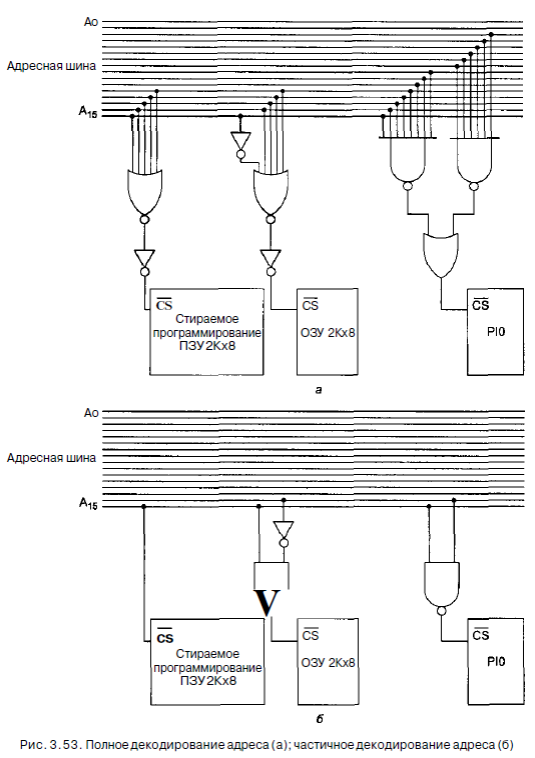

При таком распределении адресов (рис. 3.52) стираемое ПЗУ нужно выбирать с помощью 16-битного адреса памяти ОООООххххххххххх (в двоичной системе). Другими словами, любой адрес, у которого пять старших битов равны 0, попадает в область памяти до 2 К и, следовательно, в стираемое ПЗУ. Таким образом, сигнал выбора стираемого ПЗУ можно связать с 5-разрядным компаратором, у которого один из входов всегда будет соединен с 00000. Чтобы достичь того же результата, лучше было бы использовать пятивходовый вентиль ИЛИ, у которого пять входов связаны с адресными линиями от А11 до А15. Выходной сигнал будет равен 0 тогда и только тогда, когда все пять линий равны 0. В этом случае устанавливается сигнал US. К сожалению, в стандартных сериях МИС не существует пятивходовых вентилей ИЛИ. Однако мы можем использовать восьмивходовый вентиль НЕ-ИЛИ. Заземлив три входа и инвертировав выход, мы можем получить нужный нам сигнал (рис. 3.53, а). Схемы МИС стоят очень дешево, поэтому неэффективное использование одной из них вполне допустимо. По соглашению неиспользуемые входы на схемах не показываются.

Тот же принцип можно применить и для ОЗУ. Однако ОЗУ должно отвечать

на бинарные адреса типа ЮОООххххххххххх, поэтому необходим дополнительный инвертор (он показан на схеме). Декодирование адреса микросхемы PIO несколько сложнее, поскольку данная микросхема выбирается с помощью 4 адресов типа 11111111111111хх. Один из возможных вариантов схемы, которая устанавливает сигнал CS только в том случае, если на адресной шине появляется адрес данного типа, показан на рис. 3.53. Здесь используются два восьмивходовых вентиля НЕ-И, которые соединяются с вентилем ИЛИ. Чтобы сконструировать схему декодирования адреса, изображенную на рис. 3.53, а, требуется шесть микросхем МИС: четыре восьмивходовые микросхемы, вентиль ИЛИ и микросхема с тремя инверторами. Если компьютер состоит только из центрального процессора, двух микросхем памяти и PIO, мы можем сильно упростить процесс декодирования адреса. Дело в том, что у всех адресов стираемого ПЗУ и только у адресов стираемого ПЗУ старший разряд А15 всегда равен 0. Следовательно, мы можем просто связать сигнал С5 с линией А15, как показано на рис. 3.53, б. Теперь решение поместить ОЗУ в адрес 8000Н кажется не таким уж произвольным. Отметим, что в ОЗУ попадают адреса типа Юхххххххххххххх, поэтому для декодирования достаточно двух битов. Точно так же, любой адрес, начинающийся с 11, является адресом PIO. Полная логика декодирования состоит из двух вентилей НЕ-И и инвертора. Поскольку инвертор можно сделать из вентиля НЕ-И, связав два входа вместе, одного счетверенного вентиля НЕ-И более чем достаточно.

Логика декодирования адреса, показанная на рис. 3.53, б, называется частичным декодированием адреса, поскольку в данном случае полные адреса не используются. При таком декодировании считывание из адресов 0001000000000000, 0001100000000000 и 0010000000000000 будет давать один и тот же результат. В действительности любой адрес в нижней половине адресного пространства будет выбирать стираемое ПЗУ. Поскольку дополнительные адреса не используются, в этом нет ничего ужасного, но при разработке компьютера, который будет расширяться в будущем (в случае с игрушками это маловероятно), следует избегать частичного декодирования, поскольку оно сильно ограничивает адресное пространство.

Можно применять и другую технологию декодирования адреса - технологию

с использованием декодера (см. рис. 3.12). Связав три входа с тремя адресными линиями самых старших разрядов, мы получаем восемь выходов, которые соответствуют адресам в первом отрезке 8 К, втором отрезке 8 К и т. д. В компьютере, содержащем 8 микросхем ОЗУ по 8 Кх8 байт, полное декодирование осуществляет одна такая микросхема. Если компьютер содержит 8 микросхем памяти по 2 Кх8 байт, для декодирования также достаточно одного декодера, при условии что каждая микросхема памяти занимает отдельный участок адресного пространства в 8 К. (Вспомните наше замечание о том, что расположение микросхем памяти и устройств ввода-вывода внутри адресного пространства имеет значение.)

Лекция 9. Принципы микроархитектурного уровня.

1. Основные задачи микроархитектуры.

2. Тракт данных и работа памяти.

3. Состав микрокоманд.

Дата добавления: 2016-10-26; просмотров: 3436;