Тракт данных и работа памяти.

2.1.Тракт данных

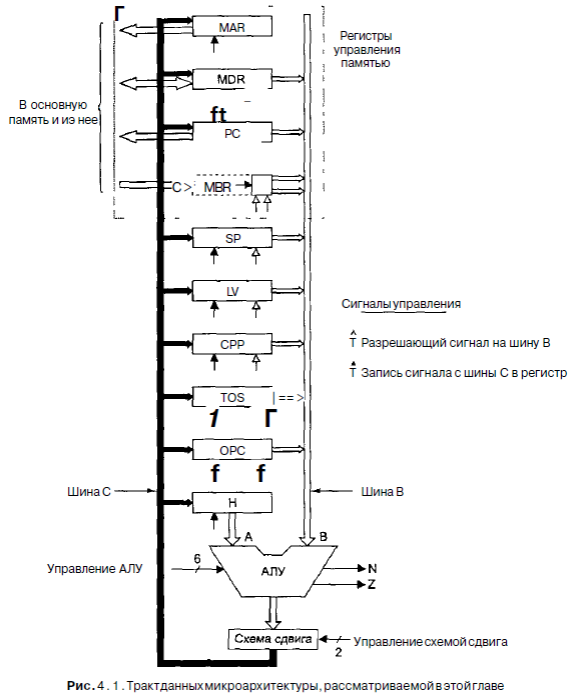

Тракт данных - это часть центрального процессора, состоящая из АЛ У (арифметико-логического устройства) и его входов и выходов. Тракт данных нашей микроархитектуры показан на рис. 4.1. Хотя этот тракт данных и был оптимизирован для интерпретации программ IJVM, он схож с трактами данных большинства компьютеров. Он содержит ряд 32-разрядных регистров, которым мы приписали символические названия (например, PC, SP, MDR). Хотя некоторые из этих названий нам знакомы, важно понимать, что эти регистры доступны только на микроархитектурном уровне (для микропрограммы). Им даны такие названия, поскольку они обычно содержат значения, соответствующие переменным с аналогичными названиями на уровне архитектуры команд Содержание большинства регистров передается на шину В. Выходной сигнал АЛУ запускает схему сдвига, а затем шину С

Значение из шины С может записываться в один или несколько регистров одновременно Шину А мы введем позже, а пока представим, что ее нет

Данное АЛУ идентично тому, которое изображено на рис. 3.18 и 3.19. Его функционирование зависит от линий управления. На рис. 4.1 перечеркнутая стрелочка с цифрой 6 сверху указывает на наличие шести линий управления АЛУ. Из них Fu и р!служат для определения операции, EN А и ENB - для разрешения входных сигналов А и В соответственно, 1NVA - для инверсии левого входа и INC – для прибавления единицы к результату. Однако не все 64 комбинации значений на линиях управления могут быть полезны.

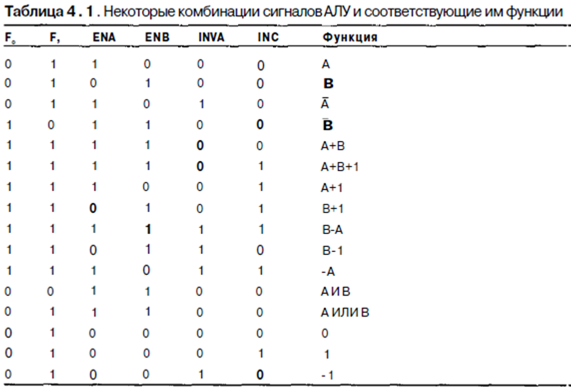

Некоторые комбинации показаны в табл. 4.1. Не все из этих функций нужны

для IJVM, но многие из них могут пригодиться для полной JVM. В большинстве случаев существует несколько возможностей для достижения одного и того же результата. В данной таблице знак «+» означает арифметический плюс, а знак «-» -арифметический минус, поэтому -А означает дополнение А.

АЛУ, изображенное на рис. 4.1, содержит два входа для данных: левый вход (А) и правый вход (В). С левым входом связан регистр временного хранения Н. С правым входом связана шина В, в которую могут поступать значения из одного из девяти источников, что показано с помощью девяти серых стрелок, примыкающих к шине. Существует и другая разработка АЛУ с двумя полноразрядными шинами, и мы рассмотрим ее чуть позже в этой главе.

В регистр Н может поступать функция АЛУ, которая проходит через правый

вход (из шины В) к выходу АЛУ Одна из таких функций - сложение входных

сигналов АЛУ, только при этом сигнал ENA отрицается, и левый вход получает значение 0. Если к значению шины В прибавить 0, это значение не изменится. Затем результат проходит через схему сдвига (также без изменений) и сохраняется в регистре Н.

Существует еще две линии управления, которые используются независимо от

остальных. Они служат для управления выходом АЛУ. Линия SLL8 (Shift Left Logical - логический сдвиг влево) сдвигает число влево на 1 байт, заполняя 8 самых младших двоичных разрядов нулями; линия SRA1 (Shift Right Arithmetic - арифметический сдвиг вправо) число вправо на 1 бит, оставляя самый старший двоичный разряд без изменений.

Можно считать и записать один и тот же регистр за один цикл. Для этого, например, нужно поместить значение SP на шину В, закрыть левый вход АЛУ, установить сигнал INC и сохранить полученный результат в регистре SP, увеличив таким образом его значение на 1 (см. восьмую строку табл. 4.1). Если один и тот же регистр может считываться и записываться за один цикл, то как при этом предотвратить появление ненужных данных? Дело в том, что процессы чтения и записи проходят в разных частях цикла. Когда в качестве правого входа АЛУ выбирается один из регистров, его значение помещается на шину В в начале цикла и хранится там на протяжении всего цикла. Затем АЛУ выполняет свою работу и производит результат, который через схему сдвига поступает на шину С. Незадолго до конца цикла, когда значения выходных сигналов АЛУ и схемы сдвига стабилизировались, содержание шины С передается в один или несколько регистров. Одним из этих регистров вполне может быть тот, от которого поступил сигнал на шину В.

Точная синхронизация тракта данных делает возможным считывание и запись одного и того же регистра за один цикл. Об этом речь пойдет ниже.

2.2.Синхронизация тракта данных

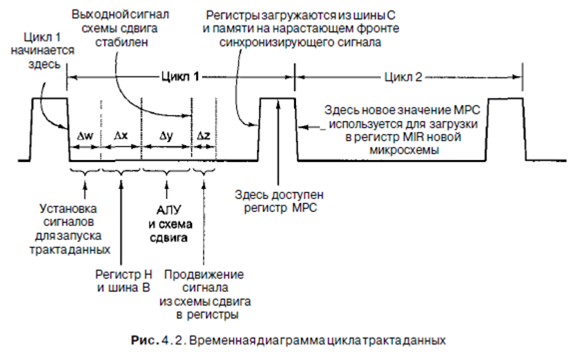

Как происходит синхронизация этих действий, показано на рис. 4.2. Здесь в начале каждого цикла генерируется короткий импульс. Он может выдаваться задающим генератором, как показано на рис. 3.20, в. На заднем фронте импульса устанавливаются биты, которые будут запускать все вентили. Этот процесс занимает определенный отрезок времени Aw. Затем выбирается регистр, и его значение передается на шину В. На это требуется время Дх. Затем АЛУ и схема сдвига начинают оперировать поступившими к ним данными. После промежутка Ду выходные сигналы АЛУ и схемы сдвига стабилизируются. В течение следующего отрезка Дг результаты проходят по шине С к регистрам, куда они загружаются на нарастающем фронте следующего импульса. Загрузка должна запускаться фронтом сигнала и осуществляться мгновенно, так что даже в случае изменений каких-либо

входных регистров изменения в шине С будут происходить только после полной загрузки регистров. На нарастающем фронте импульса регистр, запускающий шину В, приостанавливает свою работу и ждет следующего цикла. На рис. 4.2 упомянуты регистры МРС и MIR, а также память. Их предназначение мы обсудим чуть позже.

Важно осознавать, что хотя в тракте данных нет никаких запоминающих эле-

ментов, для прохождения сигнала по нему требуется определенное время. Изменение значения на шине В вызывает изменения на шине С не сразу, а только через некоторое время (это объясняется задержками на каждом шаге). Следовательно, даже если один из входных регистров изменяется, новое значение будет сохранено в регистре задолго до того, как старое (и уже неправильное) значение этого регистра, помещенное на шину В, сможет достичь АЛУ.

Для такой разработки требуется жесткая синхронизация и довольно длинный

цикл; должно быть известно минимальное время прохождения сигнала через АЛУ; регистры должны загружаться из шины С очень быстро. Если подойти к этому вопросу с особым вниманием и осторожностью, можно сделать так, чтобы тракт данных функционировал правильно.

Цикл тракта данных можно разбить на подциклы. Начало подцикла 1 запускается задним фронтом синхронизирующего сигнала. Ниже показано, что происходит во время каждого из подциклов. В скобках приводится длина подцикла.

1. Устанавливаются сигналы управления (Aw).

2. Значения регистров загружаются на шину В (Ах).

3. Происходит работа АЛУ и схемы сдвига (Ду).

4. Результаты проходят по шине С обратно к регистрам (Дг).

На нарастающем фронте следующего цикла результаты сохраняются в регистрах. Никаких внешних сигналов, указывающих на начало и конец подцикла и сообщающих АЛУ, когда нужно начинать работу и когда нужно передавать результаты на шину С, нет. В действительности АЛУ и схема сдвига работают постоянно. Однако их входные сигналы недействительны в течение периода Aw+Дх. Точно так же их выходные сигналы недействительны в течение периода Aw+ Дх+Ду. Единственными внешними сигналами, управляющими трактом данных, являются задний фронт синхронизирующего сигнала, с которого начинается цикл тракта данных, и

нарастающий фронт синхронизирующего сигнала, который загружает регистры из шины С. Границы подциклов определяются толоко временем прохождения сигнала, поэтому разработчики тракта данных должны все очень четко рассчитать.

2.3.Работа памяти

Наша машина может взаимодействовать с памятью двумя способами: через порт с пословной адресацией (32-битный) и через порт с байтовой адресацией (8-битный). Порт с пословной адресацией управляется двумя регистрами; MAR (Memory Address Register - регистр адреса ячейки памяти) и MDR (Memory Data Register - информационный регистр памяти), которые показаны на рис. 4.1. Порт с байтовой адресацией управляется регистром PC, который записывает 1 байт в 8 младших ьразрядов регистра MBR (Memory Buffer Register - буферный регистр памяти).

Этот порт может считывать данные из памяти, но не может их записывать в память. Каждый из этих регистров, а также все остальные регистры, изображенные на рис. 4.1, запускаются одним из сигналов управления. Белая стрелка под регистром указывает на сигнал управления, который разрешает передавать выходной сигнал регистра на шину В. Регистр MAR не связан с шиной В, поэтому у него нет сигнала разрешения. У регистра Н этого сигнала тоже нет, так как он является единственным возможным левым входом АЛУ и поэтому всегда разрешен.

Черная стрелка под регистром указывает на сигнал управления, который записывает (то есть загружает) регистр из шины С. Поскольку регистр MBR не может загружаться из шины С, у него нет сигнала записи (но зато есть два сигнала разрешения, о которых речь пойдет ниже). Чтобы инициировать процесс считывания из памяти или записи в память, нужно загрузить соответствующие регистры памяти, а затем передать памяти сигнал чтения или записи (он не показан на рис. 4.1).

Регистр MAR содержит адреса слов, таким образом, значения 0,1,2 и т. д. указывают на последовательные слова. Регистр PC содержит адреса байтов, таким образом, значения 0,1,2 и т. д. указывают на последовательные байты. Если значение 2 поместить в регистр PC и начать процесс чтения, то из памяти считается байт 2, который затем будет записан в 8 младших разрядов регистра MBR. Если значение 2 поместить в регистр MAR и начать процесс чтения, то из памяти считаются байты 8-11 (то есть слово 2), которые затем будут записаны в регистр MDR. Для чего потребовалось два регистра с разной адресацией? Дело в том, что регистры MAR и PC будут использоваться для обращения к двум разным частям памяти, а зачем это нужно, станет ясно чуть позже. А пока достаточно сказать, что регистры MAR и MDR используются для чтения и записи слов данных на уровне

архитектуры команд, а регистры PC и MBR - для считывания программы уровня архитектуры команд, которая состоит из потока байтов. Во всех остальных регистрах, содержащих адреса, применяется принцип пословной адресации, как и в MAR.

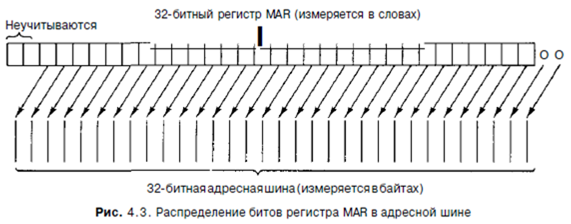

В действительности существует только одна память: с байтовой адресацией. Как же регистр MAR обращается к словам, если намять состоит из байтов? Когда значение регистра MAR помещается на адресную шину, 32 бита этого значения не попадают точно на 32 адресные линии (с 0 по 31). Вместо этого бит 0 соединяется с адресной линией 2, бит 1 - с адресной линией 3 и т. д. Два старших бита не учитываются, поскольку они нужны только для адресов свыше 232, а такие адреса недопустимы в нашей машине на 4 Гбайт. Когда значение MAR равно 1, на шину помещается адрес 4; когда значение MAR равно 2, на шину помещается адрес 8 и т. д. Распределение битов регистра MAR по адресным линиям показано на рис. 4.3.

Как уже было сказано выше, данные, считанные из памяти через 8-битный порт, сохраняются в 8-битном регистре MBR. Этот регистр может быть скопирован на шину В двумя способами: со знаком и без знака. Когда требуется значение без знака, 32-битное слово, помещаемое на шину В, содержит значение MBR в младших 8 битах и нули в остальных 24 битах. Значения без знака нужны для индексирования таблиц или для получения целого 16-битного числа из двух последовательных байтов (без знака) в потоке команд.

Другой способ превращения 8-битного регистра MBR в 32-битное слово - рассматривать его как значение со знаком между -128 и +127 и использовать это значение для порождения 32-битного слова с тем же самым численным значением.

Это преобразование делается путем дублирования знакового бита (самого левого бита) регистра MBR в верхние 24 битовые позиции шины В. Такой процесс называется расширением по знаку или знаковым расширением Если выбран данный параметр, то либо все старшие 24 бита примут значение 0, либо все они примут значение 1, в зависимости от того, каков самый левый бит регистра MBR: 0 или 1. В какое именно 32-битное значение (со знаком или без знака) превратится 8-битное значение регистра MBR, определяется тем, какой из двух сигналов управления (две белые стрелки под регистром MBR на рис. 4.1) установлен. Прямоугольник, обозначенный на рисунке пунктиром, показывает способность 8-битного регистра MBR действовать в качестве источника 32-битных слов для шины В.

Дата добавления: 2016-10-26; просмотров: 4936;