Запоминающие устройства

Запоминающие устройства (ЗУ) предназначены для записи, хранения и считывания (выборки) цифровой информации. Микросхемы памяти представляют собой функционально - и конструктивно-законченные микроэлектронные изделия, предназначенные для реализации запоминающих устройств (ЗУ).

Общепринятой является классификация микросхем памяти по следующим признакам: функциональное назначение, способ хранения информации, степень зависимости от источников питания, схемно-технологическое исполнение .

По функциональному назначению микросхемы памяти подразделяют на микросхемы оперативных ЗУ (ОЗУ) и постоянных ЗУ (ПЗУ). Оперативные ЗУ предназначены для хранения переменной информации: программ и промежуточных результатов обработки данных. Такие ЗУ работают в режимах записи, хранения и считывания информации и допускают оперативную смену своего информационного содержания. Постоянные ЗУ предназначены для хранения информации, неменяющейся в процессе работы устройства: стандартных программ, табличных данных, коэффициентов, констант и т. п. Такие ЗУ работают в режимах хранения и считывания информации, которая заносится в них предварительно, например, при их изготовлении, и во время работы не изменяется.

Основной составной частью структуры любой микросхемы памяти является матрица накопителя, представляющая собой однородный массив элементов памяти. Элемент памяти (ЭП) может хранить один бит (0 или 1) информации. Схемотехнический принцип построения элемента памяти в значительной степени определяет способ хранения информации в накопителе. По этому признаку микросхемы памяти можно разделить на статические и динамические запоминающие устройства.

В микросхемах статических ЗУ информация в режиме хранения неподвижна, т. е. находится в статическом состоянии. В этот класс микросхем памяти входят микросхемы ОЗУ, у которых элементом памяти является статический триггер, и микросхемы ПЗУ.

В микросхемах динамических ЗУ записанная в накопитель информация в режиме хранения периодически перезаписывается с целью ее восстановления (регенерации). К этому классу микросхем памяти относят микросхемы динамических ОЗУ. Элементом памяти в таких микросхемах является МДП - конденсатор, сформированный внутри полупроводникового кристалла. Информация, имеющая форму уровня напряжения (заряда) на конденсаторе, из-за наличия токов утечки в объеме и на поверхности полупроводникового кристалла не может сохраняться длительное время и поэтому нуждается в периодическом восстановлении.

Микросхемы динамических ОЗУ имеют большую информационную емкость, чем микросхемы статических ОЗУ, что обусловлено меньшим числом компонентов в одном элементе памяти и, следовательно, более плотным их размещением в полупроводниковом кристалле. Однако динамические ОЗУ сложнее в применении, поскольку нуждаются в организации принудительной регенерации, а значит, в дополнительном оборудовании и в усложнении устройств управления.

Для хранения небольших объемов информации широко применяют регистровые ЗУ. В обширной номенклатуре микросхем регистров некоторая их часть содержит многорегистровые структуры, которые можно использовать для одновременного хранения нескольких слов. Возможности таких микросхем зависят от их структурного построения и способа адресации регистров. Некоторые допускают адресное обращение к каждому из регистров (регистровые файлы). Другие работают по принципу «магазинного» ЗУ, заполняясь информацией по мере ее поступления и освобождаясь от нее в порядке ее поступления по правилу «первым вошел - первым вышел» (FIFO – First Input First Output) или в обратном порядке «последним вошел - первым вышел» (LIFO - Last Input First Output). Магазинные ЗУ нередко называют стеком (Stack - штабель). Стековые регистровые ЗУ широко применяют в калькуляторах, микропроцессорных контроллерах и других вычислительных устройствах.

В микросхемах ПЗУ функции элементов памяти выполняют перемычки между линиями строк и столбцов в накопителе. Эти перемычки представляют собой либо тонкопленочные проводники, либо диоды и транзисторы. Наличие перемычки кодируется1, ее отсутствие - 0. Возможна и обратная кодировка.

Занесение информации в микросхемы ПЗУ, т. е. их программирование, осуществляют в основном двумя способами. Один из них заключается в формировании перемычек в накопителе на заключительной стадии изготовления микросхемы с использованием трафарета (маски). Такие микросхемы получили название масочных ПЗУ (МПЗУ). Другой способ состоит в пережигании легкоплавких токопроводящих перемычек в тех точках накопителя, где должен быть записан 0 или 1 в зависимости от принятого кодирования состояний перемычек. Программирование микросхем ПЗУ осуществляет пользователь с помощью специального устройства - программатора.

Микросхемы масочных ПЗУ и программируемых пользователем ПЗУ (ППЗУ) допускают однократную запись информации, поскольку при программировании происходит необратимое разрушение соединений в накопителе. Существует разновидность ПЗУ, допускающая неоднократное программирование, т. е. перепрограммирование (репрограммирование). Этим свойством репрограммируемые ПЗУ (РПЗУ) обладают благодаря использованию в них элементов памяти на основе МДП-транзисторов специальной конструкции, способных переходить из непроводящего состояния в проводящее и обратно под воздействием внешнего программирующего напряжения. Причем оба состояния могут сохраняться длительное время (тысячи часов) без напряжения питания.

По способу стирания информации в накопителе микросхемы РПЗУ разделяют на два вида, которые называют программируемыми ПЗУ со стиранием электрическим сигналом (ЭСППЗУ) и ультрафиолетовым излучением (СППЗУ).

Наряду с полупроводниковыми микросхемами ОЗУ и ПЗУ промышленность выпускает микросхемы памяти на тонких магнитных пленках, элементами памяти в которых являются цилиндрические магнитные домены (ЦМД). Микронные размеры ЦМД позволяют разместить в тонкой пленке магнитного материала на диэлектрической подложке размерами 100*100 мм2 накопитель с информационной емкостью в десятки миллионов бит. Микросхемы памяти на ЦМД предназначены для реализации внешних запоминающих устройств, отличающихся от устройств на магнитных лентах и дисках более высокой надежностью функционирования и быстродействием благодаря полностью электронной системе записи и считывания информации.

Рассмотренные разновидности микросхем памяти систематизированы в классификационной диаграмме, приведенной на рис. 4.34.

Здесь же показаны международные буквенные обозначения микросхем памяти различных видов и типов, которые помещают на их условных графических изображениях.

По степени зависимости от источников питания различают энергозависимые и энергонезависимые ЗУ. В энергозависимых ЗУ при отключении и сбоях питания информация разрушается. Такими являются микросхемы ОЗУ. В энергонезависимых ЗУ электропитание необходимо только при записи и считывании, а в режиме хранения оно может быть отключено. К таким ЗУ относятся микросхемы ПЗУ.

Микросхемы памяти выпускают сериями. Серия представляет собой совокупность микросхем, имеющих единое конструктивно-технологическое исполнение, совместимые электрические, эксплуатационные и надежностные показатели и отличающихся информационной емкостью, быстродействием и некоторыми другими характеристиками, например наличием дополнительных входов для сигналов управления.

По физико-технологическому признаку микросхемы памяти можно разделить на два класса: биполярные и униполярные. Первые изготавливают по технологии биполярных транзисторов, вторые — по технологии полевых транзисторов, в основном МДП-транзисторов.

По схемно-технологическому признаку биполярные микросхемы обычно классифицируют на микросхемы эмиттерно-связанной логики (ЭСЛ), транзисторно-транзисторной логики (ТТЛ) и ТТЛ с диодами Шоттки (ТТЛШ), интегральной инжекционной логики (ИИЛ). Обычным является применение комбинаций схемно-технологических решений при производстве микросхем памяти, например ЭСЛ и ТТЛШ или ТТЛ и ИИЛ и т. д.

Для биполярных микросхем памяти, в частности для ЭСЛ - и ТТЛШ - микросхем, характерны высокое быстродействие, значительная нагрузочная способность, повышенное энергопотребление.

В классе униполярных микросхем памяти наиболее широко представлены микросхемы на МДП-транзисторах с каналом n - типа и микросхемы на комплементарных парах МДП-транзисторов (КМДП - микросхемы). Для nМДП – микросхем памяти характерно сравнительно высокое быстродействие, соизмеримое с быстродействием ТТЛШ - микросхем, а для КМДП - микросхем — самый низкий уровень энергопотребления и способность функционировать в условиях значительных изменений напряжения питания.

Обобщенная структурная схема запоминающего устройства, характерная для ОЗУ и ПЗУ, представлена на рис. 4.35. Она включает следующие функциональные узлы: накопитель, дешифратор кода адреса (ДШ), устройство ввода-вывода (УВВ), устройство управления (УУ).

Накопитель представляет собой совокупность элементов памяти (ЭП), объединенных в матрицу. В матрице ЭП находятся на пересечениях горизонтальных и вертикальных проводников, называемых соответственно строками и столбцами. Каждый ЭП может хранить один бит (0 или 1) информации. Для хранения n - разрядного слова требуются n элементов памяти. Совокупность элементов памяти, предназначенная для хранения одного слова, называется ячейкой памяти (ЯП).

Накопитель может иметь одноразрядную и многоразрядную (словарную) организацию. Их принципиальное различие состоит в следующем. При обращении к накопителю с одноразрядной организацией в него можно записать или из него вывести только один бит информации, т.е. одноразрядное слово. Накопитель со словарной организацией позволяет за одно обращение к нему записать или считать n разрядов, составляющих слово. На рис. 4.35. представлена структура микросхемы памяти со словарной организацией. Как видно, она имеет n информационных входов и столько же выходов, что позволяет записывать и считывать информацию n - разрядным параллельным кодом. Микросхема с одноразрядной организацией имеет один информационный вход и один выход.

Организация ЗУ предусматривает возможность обращения к любой ЯП для записи или считывания информации. Для этой цели служит дешифратор (ДШ). Он преобразует код адреса  в активный сигнал выборки ЯП. Число ЯП в накопителе равно

в активный сигнал выборки ЯП. Число ЯП в накопителе равно  , где m - число разрядов в адресном коде. Если ЗУ допускает выборку любой ЯП в произвольном порядке, то его называют ЗУ с произвольной выборкой (ЗУПВ).

, где m - число разрядов в адресном коде. Если ЗУ допускает выборку любой ЯП в произвольном порядке, то его называют ЗУ с произвольной выборкой (ЗУПВ).

Устройство ввода-вывода (УВВ) предназначено для усиления и нормализации информационных сигналов  , подаваемых на входы ЗУ D1 при записи и снимаемых с выходов D0 при считывании. Многие микросхемы имеют совмещенные входы-выходы. В таких микросхемах УВВ дополнительно выполняет и функцию разделения внутренних цепей приема и выдачи информации. К УВВ предъявляется также требование сопряжения входов и выходов с внешними линиями передачи.

, подаваемых на входы ЗУ D1 при записи и снимаемых с выходов D0 при считывании. Многие микросхемы имеют совмещенные входы-выходы. В таких микросхемах УВВ дополнительно выполняет и функцию разделения внутренних цепей приема и выдачи информации. К УВВ предъявляется также требование сопряжения входов и выходов с внешними линиями передачи.

Устройство управления формирует внутренние сигналы для воздействия на функциональные узлы ЗУ, соответствующего внешним сигналам управления: «Запись/Считывание» (WR/RD), «Выбор кристалла (микросхемы)» (CS). Сигнал WR/RD определяет режим записи при WR/RD=1 и считывания при WR/RD=0. Сигнал CS разрешает при СS=1 или запрещает доступ к накопителю по информационным входам и выходам при СS=0. У большинства микросхем памяти сигнал CS является основным для установления микросхемы в режим хранения независимо от состояний сигналов на других входах.

Принцип действия изображенной на рис.4.35 схемы применительно к ОЗУ заключается в следующем. Для записи слова Dn-1 ... D0 в заданную ЯП его необходимо подать на информационные входы DIn-1... DI0. Одновременно на адресные входы Аm-1... А0 должен быть подан код адреса выбираемой ЯП, а на входы управления - сигналы WR/RD=1 и СS=1. После выполнения этих операций входная информация через УВВ пройдет в накопитель и запишется в выбранную ячейку памяти. Для обеспечения режима хранения достаточно подать сигнал CS=0. Режим считывания реализуется аналогично режиму записи, но при значении сигнала WR/RD=0.

Типовая схема ПЗУ отличается от ОЗУ отсутствием входов для информационных сигналов.

Следует заметить, что сигналы на входах и выходах микросхем ОЗУ и ПЗУ могут быть представлены своими прямыми значениями, как, например, в вышеприведенном рассмотрении, так и инверсными. В случае инверсного представления сигнала его активное состояние изменяется на обратное, например, при  будет осуществлен режим записи, а при

будет осуществлен режим записи, а при  - режим считывания. Аналогично при сигнале СS=0 будет обеспечен доступ к микросхеме, а при СS=1 микросхема будет находиться в режиме хранения.

- режим считывания. Аналогично при сигнале СS=0 будет обеспечен доступ к микросхеме, а при СS=1 микросхема будет находиться в режиме хранения.

Структуры, и функциональные узлы микросхем статических ОЗУ.Вариант построения микросхемы статического ОЗУ с одноразрядной организацией приведен на рис. 4.36. Для примера выбрана сравнительно несложная микросхема К561РУ2 емкостью 256 бит. Структурная схема включает матрицу накопителя, дешифраторы кода адреса строк А3... А0 (А0 - младший разряд) и столбцов А7... А4, ключи выбора столбцов и УВВ. Режимом микросхемы управляют сигналы  и

и  .

.

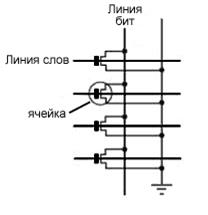

Матрица накопителя содержит 256 элементов памяти, расположенных на пересечениях 16 строк и 16 столбцов. Каждый ЭП представляет собой статический триггер на КМДП - транзисторах (рис. 4.37, а): VT1, VT2 - с n-каналами, VT3, VТ4 - с p-каналами.

Триггер имеет два парафазных совмещенных входа - выхода. С разрядными шинами РШ1 и РШ0 триггер соединен через ключевые транзисторы VТ5, VТ6. По разрядным шинам к триггеру подводится при записи и отводится от него при считывании информация в парафазной форме представления: по РШ1 – своим прямым значением, по РШ0 – инверсным. Ключевые транзисторы затворами соединены с адресной шиной (строкой). В режимах записи и считывания при возбуждении строки сигналом выборки Xi=1, снимаемым с выхода дешифратора адреса строк, ключевые транзисторы открываются и подключают триггер к разрядным шинам. При сигнале Xi=0 ключевые транзисторы закрыты, и триггер изолирован от разрядных шин.

Для сохранения состояния триггера и, следовательно, записанной в нем информации необходим источник питания, поскольку статический триггер энергозависим. В одно из двух состояний, в которых может находиться триггер, его приводят сигналы, поступающие по разрядным шинам в режиме записи: при D=1 (РШ1=1, РШ0=0) транзисторы VT1 и VT4 открыты, а VT2, VT3 закрыты, при D=0 (РШ1=0, РШ0=1) транзисторы свои состояния изменяют на обратные. В режиме считывания разрядные шины принимают потенциалы выходов триггера, передавая их через УВВ на выход микросхемы  . При считывании информация не разрушается, т, е. состояния триггеров не изменяются. Особенность КМДП - триггеров заключается в том, что в режиме хранения они потребляют незначительную мощность от источника питания, так как в любом состоянии триггера в той или другой его половине один из транзисторов закрыт. В режиме обращения к микросхеме при записи или считывании транзисторы переключаются, через них протекают токи, что обусловливает значительное повышение потребляемой мощности. Кроме триггеров в структуре микросхемы в режиме обращения к ней переключаются элементы дешифраторов, УВВ, поэтому уровень ее энергопотребления возрастает на два-три порядка.

. При считывании информация не разрушается, т, е. состояния триггеров не изменяются. Особенность КМДП - триггеров заключается в том, что в режиме хранения они потребляют незначительную мощность от источника питания, так как в любом состоянии триггера в той или другой его половине один из транзисторов закрыт. В режиме обращения к микросхеме при записи или считывании транзисторы переключаются, через них протекают токи, что обусловливает значительное повышение потребляемой мощности. Кроме триггеров в структуре микросхемы в режиме обращения к ней переключаются элементы дешифраторов, УВВ, поэтому уровень ее энергопотребления возрастает на два-три порядка.

В большинстве микросхем памяти УВВ содержит выходной ключевой усилитель-формирователь, способный принимать три состояния: два функциональных низкого и высокого уровня и одно высокоомное, обозначаемое Z-состоянием. В этом состоянии выход микросхемы практически отключен от внешней цепи. Пример такого усилителя приведен на рис. 4.37,б. Его схема состоит из инвертора на транзисторах VТ1, VТ2, двух ключевых транзисторов VТЗ, VТ4, обеспечивающих реализацию Z - состояния выхода, а также логического элемента DD2, на выходе которого формируется сигнал управления режимом ключей  . При

. При  или

или  оба ключа закрыты и выход находится в Z-состоянии. Только при условии

оба ключа закрыты и выход находится в Z-состоянии. Только при условии  и

и  ключи открыты, и схема выполняет свои функции инвертора, передавая на выходD0микросхемы информацию, считанную с выбранного элемента памяти. Наличие у микросхемы выхода с Z-состоянием позволяет объединять ее информационные вход и выход и подключать их к общей шине, по которой информация подводится к микросхеме и выводится из нее. Указанная возможность основана на том, что в любом режиме вход и выход микросхемы оказываются взаимно развязаны, как это следует из табл. 4.10, и не влияют на состояния друг друга. В указанной таблице истинности микросхемы К561РУ2 приведены условия реализации режимов работы микросхемы: хранения, записи данных, считывания данных.

ключи открыты, и схема выполняет свои функции инвертора, передавая на выходD0микросхемы информацию, считанную с выбранного элемента памяти. Наличие у микросхемы выхода с Z-состоянием позволяет объединять ее информационные вход и выход и подключать их к общей шине, по которой информация подводится к микросхеме и выводится из нее. Указанная возможность основана на том, что в любом режиме вход и выход микросхемы оказываются взаимно развязаны, как это следует из табл. 4.10, и не влияют на состояния друг друга. В указанной таблице истинности микросхемы К561РУ2 приведены условия реализации режимов работы микросхемы: хранения, записи данных, считывания данных.

| Таблица 4.10. Таблица истинности микросхемы К561РУ2 | |||||

|

| A0 ... A7 | D1 | D0 | Режим работы |

| Х | X | Х | Z | Хранение | |

| А | D | Z | Запись данных | ||

| А | Х |

| Считывание данных прямым и инверсным значением |

Примечание. Х - произвольное состояние (0 или 1).

Микросхемы на МДП-транзисторах любого типа чувствительны к воздействию статического электричества из-за высокого входного сопротивления. Даже кратковременное повышение напряжения на входе с недопустимо высоким уровнем может вызвать электрический пробой тонкого слоя подзатворного диэлектрика. Для защиты от вредного воздействия перенапряжения все входы микросхем защищены диодно-резистивными цепями, встроенными внутрь кристалла (рис. 4.37,в). Защитные цепи построены по схеме последовательного соединения двух диодов VD1, VD2 и токоограничивающего резистора R. От воздействия высокого положительного потенциала на входе защищает диод VD1, который открывается при превышении входным потенциалом его порога и фиксирует этот потенциал на допустимом для микросхемы уровне, т. е. на уровне напряжения питания. Аналогично срабатывает диод VD2 при появлении на входе отрицательного потенциала с уровнем, превышающим порог отпирания диода. При открывании диод VD2 ограничивает отрицательный потенциал безопасным для микросхемы уровнем 1 В.

При обращении к микросхеме для записи одного бита следует подвести информационный сигнал ко входу DI, подать код адреса А {А0... A7}, разрешающий сигнал  и сигнал

и сигнал  . При указанных состояниях сигналов управления и при наличии сигналов адреса в накопителе возбуждается строка Xi, выбранная дешифратором кода адреса строк, и открывает доступ по разрядным шинам ко всем элементам памяти данной строки. Одновременно возбуждается один из выходов Yi дешифратора кода адреса столбцов. Сигнал на этом выходе дешифратора открывает в блоке ключей выбора столбца транзисторы VTj0, VTj1 и коммутирует тем самым выбранный столбец на УВВ. Доступ к разрядным шинам этого столбца со стороны УВВ обеспечивает сигнал

. При указанных состояниях сигналов управления и при наличии сигналов адреса в накопителе возбуждается строка Xi, выбранная дешифратором кода адреса строк, и открывает доступ по разрядным шинам ко всем элементам памяти данной строки. Одновременно возбуждается один из выходов Yi дешифратора кода адреса столбцов. Сигнал на этом выходе дешифратора открывает в блоке ключей выбора столбца транзисторы VTj0, VTj1 и коммутирует тем самым выбранный столбец на УВВ. Доступ к разрядным шинам этого столбца со стороны УВВ обеспечивает сигнал  , который открывает ключи VT0 и VT1. Настройку УВВ на прием информационного сигнала с входа D1 осуществляет сигнал

, который открывает ключи VT0 и VT1. Настройку УВВ на прием информационного сигнала с входа D1 осуществляет сигнал  . Обращение к микросхеме для считывания происходит аналогично, но при сигнале

. Обращение к микросхеме для считывания происходит аналогично, но при сигнале  .

.

Увеличить разрядность хранимых в памяти слов можно параллельным включением нескольких одинаковых ИС.

Микросхемы статических ОЗУ с одноразрядной организацией преобладают в современной номенклатуре микросхем памяти. Вместе с тем все большее развитие получают микросхемы ОЗУ со словарной организацией.

Основным требованием, предъявляемым к ПЗУ, является сохранение информации при отключении питания. Это требование обеспечивается конструкцией ЭП. Самый простой – диодный ЭП, используемый в ПЗУ, изображен на рис. 4.38. Выборка требуемого ЭП осуществляется подачей сигнала в соответствующую шину адреса ША. Считывается информация с разрядной шины РШ. Для установки нужного ЭП в 1 в точке пересечения адресной и разрядной шин выполняется диод. Если диод отсутствует, ЭП хранит 0. Недостатком диодных ЭП является низкое быстродействие, вызванное отсутствием в ЭП активных элементов, ускоряющих зарядку емкостей разрядных шин. Поэтому ПЗУ этого типа широкого распространения не получили. Наиболее распространены ПЗУ с ЭП,  выполненными на биполярных или МОП-транзисторах. ЭП на биполярном транзисторе (рис. 4.38) может хранить 1 или 0 в зависимости от того, имеет ли эмиттер транзистора связь с разрядной шиной РШ. Если эмиттер не соединен с разрядной шиной, на разрядной шине будет 0. Когда эмиттер транзистора связан с РШ, при подаче в адресную шину 1 (выборке ЭП), на разрядной шине установится 1. Чаще используют многоэмиттерные транзисторы, что позволяет сразу формировать двоичное слово. Связь нужных эмиттеров с разрядными шинами устанавливается только один раз на одной из завершающих операций технологического процесса. Такие ПЗУ называют масочными (МПЗУ).

выполненными на биполярных или МОП-транзисторах. ЭП на биполярном транзисторе (рис. 4.38) может хранить 1 или 0 в зависимости от того, имеет ли эмиттер транзистора связь с разрядной шиной РШ. Если эмиттер не соединен с разрядной шиной, на разрядной шине будет 0. Когда эмиттер транзистора связан с РШ, при подаче в адресную шину 1 (выборке ЭП), на разрядной шине установится 1. Чаще используют многоэмиттерные транзисторы, что позволяет сразу формировать двоичное слово. Связь нужных эмиттеров с разрядными шинами устанавливается только один раз на одной из завершающих операций технологического процесса. Такие ПЗУ называют масочными (МПЗУ).

В полупроводниковых ЗУ, программируемых пользователем (ППЗУ), в исходном состоянии во всех пересечениях адресных шин с разрядными выполнены ЭП, последовательно с которыми включаются плавкие перемычки, пережигаемые в процессе программирования . В биполярных ППЗУ, выполненных на многоэмиттерных транзисторах, плавкая перемычка выполняется в эмиттерной цепи ( см. рис. 4.39.). При выборке дешифратором  адреса требуемого слова при наличии перемычки транзистор Т2, открытый коллектор которого через резистор RН подключен к U питания, включен и на выходе будет 0, если перемычка расплавлена – транзистор Т2 закрыт и на выходе – 1. Для пережигания перемычки одновременно с выборкой слова на выход подается напряжение U=8 В, достаточное для включения стабилитрона Д. При этом включается транзистор Т1, соединяя перемычку с корпусом. Напряжение питания Е многоэмиттерного транзистора при программировании доводится до 12 В, в этих условиях ток через перемычку достаточен для ее расплавления.

адреса требуемого слова при наличии перемычки транзистор Т2, открытый коллектор которого через резистор RН подключен к U питания, включен и на выходе будет 0, если перемычка расплавлена – транзистор Т2 закрыт и на выходе – 1. Для пережигания перемычки одновременно с выборкой слова на выход подается напряжение U=8 В, достаточное для включения стабилитрона Д. При этом включается транзистор Т1, соединяя перемычку с корпусом. Напряжение питания Е многоэмиттерного транзистора при программировании доводится до 12 В, в этих условиях ток через перемычку достаточен для ее расплавления.

Большое распространение в настоящее время получила постоянная память, названная флэш-памятью. Флэш-технология позволила оснастить память уникальными свойствами. Подобно ОЗУ, флэш-память можно перепрограммировать электрически внутрисистемно, во премя основной работы устройства, но подобно ПЗУ, флэш-память энергонезависима и хранит данные даже после отключения питания. Такое сочетание находит применение в самых различных устройствах как профессионального, так и бытового назначения.

Большое распространение в настоящее время получила постоянная память, названная флэш-памятью. Флэш-технология позволила оснастить память уникальными свойствами. Подобно ОЗУ, флэш-память можно перепрограммировать электрически внутрисистемно, во премя основной работы устройства, но подобно ПЗУ, флэш-память энергонезависима и хранит данные даже после отключения питания. Такое сочетание находит применение в самых различных устройствах как профессионального, так и бытового назначения.

Ячейка флэш-памяти представляет собой полевой транзистор с двумя изолированными затворами: управляющим и плавающим. Важной особенностью плавающего затвора является способность удерживать электроны, то есть заряд. Также в ячейке имеются сток и исток (рис.4.40). При программировании, между стоком и истоком под воздействием положительного поля на управляющем затворе создается канал — поток электронов. Некоторые из электронов, благодаря наличию большей энергии, преодолевают слой изолятора и попадают на плавающий затвор. На нем они могут храниться в течение нескольких лет. Некоторое минимальное количество электронов (заряда) на плавающем затворе соответствует логической единице, а превышающее это количество — нулю.

При чтении эти состояния распознаются путем измерения порогового напряжения транзистора. Для стирания информации на управляющий затвор подается высокое отрицательное напряжение, и электроны с плавающего затвора переходят (туннелируют) на исток. В технологиях различных производителей этот принцип работы может отличаться по способу подачи тока и чтению данных из ячейки. Важно, что в структуре флэш-памяти для хранения 1 бита информации задействуется только один элемент (транзистор), а в других типах памяти обычно для этого требуется несколько транзисторов и конденсатор. Это позволяет существенно уменьшить размеры выпускаемых микросхем, упростить технологический процесс, а, следовательно, снизить себестоимость.

Но и один бит далеко не предел: Промышленно уже выпускается флэш-память, каждая ячейка которой может хранить по 2 бита информации. Кроме того, существуют пробные образцы, с 4-х и даже 9-и битными ячейками! В такой памяти используются технология многоуровневых ячеек. Они имеют обычную структуру, а отличие заключается в том, что заряд их делится на несколько уровней, каждому из которых в соответствие ставится определенная комбинация бит. Теоретически прочитать/записать можно и более 4-х бит, однако, на практике возникают проблемы с устранением шумов и с постепенной утечкой электронов при продолжительном хранении. У существующих сегодня микросхем памяти для ячеек характерно время хранения информации, измеряемое годами и число циклов чтения/записи — от 100 тысяч до нескольких миллионов.

В качестве недостатков следует отметить, что в отличие от ОЗУ, флэш нельзя переписывать побайтно. Флэш-память читается и записывается блоками. Другая особенность памяти: ее нужно стереть перед тем, как записывать новые данные.

а) б)

Рис 4.41. Архитектуры флэш-памяти: а – NOR; б - NAND

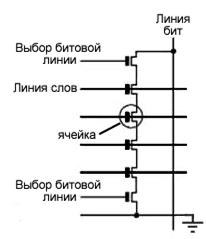

В настоящее время известны два варианта архитектуры флэш-памяти: NOR и NAND (рис.4.41). Аббревиатура NOR расшифровывается как NOT OR (ИЛИ-НЕ), а NAND – NOT AND (И-НЕ). Эти логические функции обозначают способы объединения ячеек в массив памяти.

Адресное пространство NOR-памяти позволяет работать с отдельными байтами или словами по 2 байта. Но к каждому транзистору надо подвести индивидуальный контакт. Это сильно снижает возможности увеличения плотности упаковки ячеек. В NAND ячейки группируются в небольшие блоки. Из этого следует, что при последовательном чтении и записи преимущество по скорости будет у NAND. Однако с другой стороны NAND значительно проигрывает в операциях с произвольным доступом и не позволяет напрямую работать с байтами информации. Обе архитектуры используются в своих областях применения.

Более подробные сведения о микросхемах памяти и их применении можно найти в [14]

Дата добавления: 2020-10-14; просмотров: 1068;