Логический синтез вычислительных схем

Рассмотрим логический синтез (создание) вычислительных схем на примере одноразрядного двоичного сумматора (полусумматора), имеющего два входа (а и b) и два выхода (S и P) и выполняющего операцию сложения в соответствии с табл. 6.1 (подобные таблицы в алгебре логики называют таблицами истинности).

Таблица 6.1. Логические соотношения для синтеза полусумматора

| A | B | f1(a, b) = S | f2(a, b) = P |

где

f1(a, b) = S — значение цифры суммы в данном разряде;

f2(a, b) = P — цифра переноса в следующий (старший) разряд.

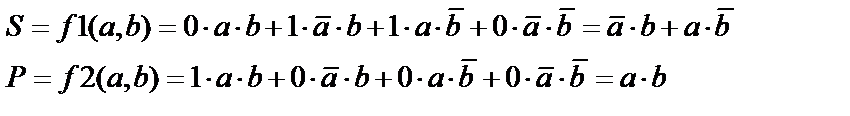

Согласно соотношению (4), можно записать:

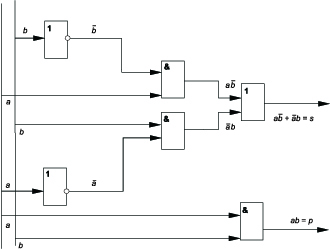

Логическая блок-схема устройства, реализующего полученную функцию, представлена на рис. 6.1.

Рис. 6.1. Логическая блок-схема полусумматора

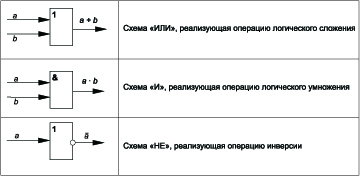

На рис. 6.2 изображены логические блоки в соответствии с международным стандартом.

Рис. 6.2. Стандартные графические обозначения блоков

ПРИМЕЧАНИЕ

В ряде случаев перед построением логической блок-схемы устройства по логической функции последнюю, пользуясь соотношениями алгебры логики, следует преобразовать к более простому виду (минимизировать). Для логических выражений «ИЛИ», «И» и «НЕ» существуют типовые технические схемы, реализующие их на реле, электронных лампах, дискретных полупроводниковых элементах и интегральных схемах. В современных компьютерах применяются системы интегральных элементов, у которых с целью большей унификации в качестве базовой логической схемы используется всего одна из схем: «НЕ — И» (NAND, штрих Шеффера), «НЕ — ИЛИ» (NOR, стрелка Пирса), А ИНОГДА и «НЕ — И — ИЛИ» (NORAND).

Дата добавления: 2021-09-25; просмотров: 619;