Электронные и логические схемы

Логические операции «AND», «OR» и «NOT» достаточно просто технически выполняются на любых системах элементов: и на электронных лампах, и на дискретных полупроводниковых элементах, и в интегральных схемах. Существуют многочисленные справочники, позволяющие выбрать подходящий вариант их технической реализации.

ПРИМЕЧАНИЕ

Здесь и далее будем считать, что «1» представляется наличием положительного импульса, а «0» — его отсутствием.

Простейшие принципиальные электрические схемы «OR» и «AND» на резисторно-диодных элементах и схема «NOT» на биполярных транзисторах показаны на рис 6.7.

Рис. 6.7. Схемы OR, AND, NOT на диодах и биполярном транзисторе

Схема «OR»: положительный импульс на выходе возникает при появлении положительного импульса на любом (a, b, c) входе, так как внутреннее сопротивление диода в прямом направлении мало (много меньше R).

Схема «AND»: положительный импульс на выходе возникает только при одновременном наличии положительных импульсов на всех трех (a, b, c) входах. При отсутствии хотя бы одного входного импульса, соответствующий ему диод будет открыт и замкнет питающее напряжение +Е через внутренние сопротивления диода и источника входного сигнала (они много меньше R) на землю.

Схема «NOT»: при подаче на вход (базу) npn-транзистора положительного импульса триод откроется и на выходе (коллекторе) напряжение с высокого снизится практически до нуля.

На рис. 6.8 показана схема «NOT» на полевых КМОП транзисторах транзисторно-транзисторной технологии. Схема «NOT»: при подаче положительного импульса на вход (a) транзистор Т1 с каналом p-типа запирается, а транзистор Т2 с каналом n-типа открывается, и на выходе (b) появляется отрицательный импульс.

Рис. 6.8. Схема NOT на полевых КМОП-транзисторах

На рис. 6.9 показана комплиментарная схема NAND на полевых транзисторах, выполненная по транзисторно-транзисторной технологии.

Рис. 6.9 Схема NAND на полевых КМОП-транзисторах

При подаче трех входных сигналов (a, b, c) , из которых хотя бы один будет низким (код «0»), на выходе схемы (f) будет высокое напряжение (код «1»). Логическая таблица истинности для этой схемы:

| a | b | c | f |

В больших интегральных схемах синтез логических и вычислительных схем выполняются на базе только одного логического «уникального» оператора: NOR, NAND или NORAND. Но каждый из уникальных операторов структурно легко реализуем на основе базовых, и, наоборот, каждый базовый операнд легко конструируется из уникальных.

| & |

| & |

| a + b |

| a b |

| b |

| b |

| a |

| b |

| & |

| a |

| & |

| & |

| a |

| a b |

| b |

| a |

| b |

| a |

| & |

| a b |

| & |

| & |

| a |

| a |

| a+b |

Рис. 6.10 Взаимные конструкции логических схем

На рис 6.10 показаны:

- логическая конструкция схемы NAND на основе схем AND и NOT,

- стандартные изображения логических схем NAND и NOR,

- логические конструкции схем NOT, AND и OR на основе схем NAND. Реализация «AND», «OR» и «NOT» на основе уникальных операторов используется при логическом синтезе вычислительных схем, ибо для базовых операторов процедуры формализованного логического синтеза разработаны наиболее подробно и конструктивно.

Триггер

Среди многих элементарных схем в компьютере наибольшее распространение получила схема триггера – статического запоминающего и логического элемента. На триггерах строятся системы статической памяти, регистры, счетчики, делители частоты и еще множество других компьютерных схем. Триггер – элемент, который может находиться в одном из двух устойчивых состояний, условно именуемых состояниями «0» и «1». Триггер имеет также два выхода: выход «0» (иногда именуемый  -выходом), выход «1» (именуемый иногда q-выходом). Если триггер находится в состоянии «0», то у него на выходе q «высокое» напряжение (порядка нескольких вольт или даже меньше), на выходе

-выходом), выход «1» (именуемый иногда q-выходом). Если триггер находится в состоянии «0», то у него на выходе q «высокое» напряжение (порядка нескольких вольт или даже меньше), на выходе  низкое (обычно нулевое) напряжение, если триггер находится в состоянии «0», то напряжения распределены наоборот.

низкое (обычно нулевое) напряжение, если триггер находится в состоянии «0», то напряжения распределены наоборот.

Триггера могут иметь раздельные входы: R (Reset) — вход установки «0», S (Set) — вход установки «1». Каждый вход устанавливает триггер в соответствующее состояние, такие триггеры часто называют R-S триггерами.

Триггеры могут иметь счетный вход T (toggle, релаксатор), очередной импульс «1» на счетном входе изменит состояние триггера. Такие триггеры часто называют T-триггерами. Триггер, установленный в какое либо состояние, сохраняет его до тех пор, пока импульс, поданный на один из входов, не изменит это состояние. Логические схемы R-S триггера (a) и T триггера (b) показаны на рис.6.11.

Рис. 6.11 Логические схемы R-S триггера (a) и T триггера (b)

Проследив напряжения на входах и выходах триггера можно видеть, что состояние триггера статически поддерживается его напряжениями. Например, сигнал «1», поступивший на вход S, на выходе  триггера установит низкое напряжение, поступающее оттуда на вход R, и будет восприниматься как сигнал установки триггера в состояние «0». Аналогичная картина наблюдается при установке триггера в состояние «0: высокое напряжение, поступающее в этом случае с выхода

триггера установит низкое напряжение, поступающее оттуда на вход R, и будет восприниматься как сигнал установки триггера в состояние «0». Аналогичная картина наблюдается при установке триггера в состояние «0: высокое напряжение, поступающее в этом случае с выхода  на вход R будет поддерживать триггер в состоянии «0». При подаче импульса «1» на счетный вход T этот импульс пройдет только через тот вентиль (схему «AND»), который пропускает его на раздельный вход, переключающий триггер. Например, если триггер находится в состоянии «1», при поступлении импульса на вход T будет открыт вентиль, пропускающий импульс на вход R, и триггер переключится в состояние «0». Принципиальная электрическая КМОП схема R-S триггера, выполненного по транзисторно-транзисторной технологии, показана на рис. 6.12.

на вход R будет поддерживать триггер в состоянии «0». При подаче импульса «1» на счетный вход T этот импульс пройдет только через тот вентиль (схему «AND»), который пропускает его на раздельный вход, переключающий триггер. Например, если триггер находится в состоянии «1», при поступлении импульса на вход T будет открыт вентиль, пропускающий импульс на вход R, и триггер переключится в состояние «0». Принципиальная электрическая КМОП схема R-S триггера, выполненного по транзисторно-транзисторной технологии, показана на рис. 6.12.

Рис. 6.12 R-S триггер на КМОП транзисторах

Триггера используются при организации запоминающих регистров и счетчиков. При этом в регистрах обычно используются триггера с раздельными входами, а в счетчиках – со счетными. Считывание информации с триггеров обычно выполняется с помощью схем AND.

Регистр

Логическая схема 3-х разрядного регистра с вентилями (схемами «AND») для ввода и считывания информации показана на рис. 6.13.

Рис. 6.13 Логическая схема регистра

В каждом i-м разряде регистр содержит R-S триггер Тi и подключенную к нему для считывания информации схему AND-вентиль. Считывание информации из регистра при подаче импульса считывания, опрашивающего схемы «AND» всех триггеров, на разрядные выходы ai поступит «1» через те вентили, триггера которых были в состоянии «1». Запись информации в регистр может выполняться в однотактном или двухтактном режимах. В однотактном режиме на соответствующий вход каждого триггера подается «1». В двухтактном режиме все входы R всех триггеров подключаются к одному проводу установки «0», по которому сначала все триггеры обнуляются, а затем на входы S тех триггеров, которые нужно установить в «1», подается соответствующий импульс.

Счетчик

На рис. 6.14 показана логическая схема 4-х разрядного двоичного счетчика. Этот счетчик 16-м импульсом сбрасывается в 0.

Рис. 6.14 Логическая схема двоичного счетчика

На счетный вход каждого следующего триггера через вентили пройдет импульс со входа счетчика только, если все предыдущие триггера стояли в состоянии «1». На рис. 6.15 показана логическая схема десятичной тетрады двоично-десятичного счетчика – он представляет собой двоичный счетчик с циклом обнуления через 10 импульсов (считает от 0 до 9).

Рис. 6.15 Логическая схема тетрады двоично-десятичного счетчика

Импульс обнуления счетчика формируется от каждого 10-го импульса, поступающего на вход счетчика (при наличии в счетчике кода 1001, то есть 9). Запись информации в счетчик не через счетный вход и считывание показаний счетчика выполняется так же, как в двоичном регистре.

Дешифратор

На рис. 6.16 показана логическая схема дешифратора 3-х разрядного двоичного кода.

Рис. 6.16 Логическая схема дешифратора

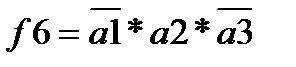

Дешифратор по двоичному коду, поступающему на вход, выбирает один выход, на котором формирует сигнал «1»; на остальных выходах формируется сигнал «0». У дешифратора n-разрядного двоичного кода может быть 2n выходов. В приведенной схеме n=3, и следовательно 23 = 8 выходов. Например, сигнал «1» на 6-ом выходе f6 будет сформирован, если на вход поступил двоичный код 010, так как  . Таблица истинности дешифратора:

. Таблица истинности дешифратора:

| a1 | a2 | a3 | f1 | f2 | f3 | f4 | f5 | f6 | F7 | f8 |

Дата добавления: 2021-09-25; просмотров: 601;