Особенности построения цифровых узлов средств отображения информации

Буферные запоминающие устройства буквенно-цифровых СОИ

Буферные запоминающие устройства выполняются как модули ОЗУ с произвольной выборкой на основе полупроводниковых накопителей — БИС ОЗУ-Нк, объединяемых в прямоугольную матрицу из тсрядов по тр БИС ОЗУ в каждом ряду. Такая организация должна обеспечить требуемое число ячеек памяти запоминающего устройства (ЗУ) NЗУ и требуемую их разрядность п. В модуль ЗУ входят также схемы согласования выходных и входных информационных и адресных сигналов и схема дешифратора адреса. Расчет модуля БЗУ производят в такой последовательности.

1) Находят требуемую разрядность п БЗУ в соответствии с выражением (1.29) и требуемое число ячеек памяти NЗУ в соответствии с выражением (3.19).

2) Определяют требуемое быстродействие в соответствии с (3.23) при учете времени задержки счетчика адресации tD.счА и схем согласования по адресным входам и информационным выходам tD.согл. Таким образом, время выборки БИС ОЗУ Нк относительно адреса должно быть

tA ≤ βГ(1 - αZ )/Nз.тсfZ - tв.ПЗУ - tD.cчА- tD.согл.(4.1)

3) Выбирают тип БИС ОЗУ-Нк, обеспечивающий требуемое быстродействие, с информационной емкостью CНк = NНк×nНк, наиболее удовлетворяющей требованиям по емкости и организации памяти БЗУ, при заданных ограничениях по стоимости, потребляемой мощности и критерию доступности.

4) Определяют число ОЗУ-Нк в ряду матрицы накопителей тР,необходимое для получения требуемой разрядности ЗУ:

тр= [пЗУ/пНк].(4.2)

5) Определяют число рядов матрицы накопителей тс,необходимое для наращивания объема ЗУ с целью получения требуемого количества N'ЗУ ячеек памяти:

mс = [NЗУ/NНК]. (4.3)

6) Находят общее количество БИС ОЗУ-Нк, входящих в модуль ЗУ:

m = mсmр. (4.4)

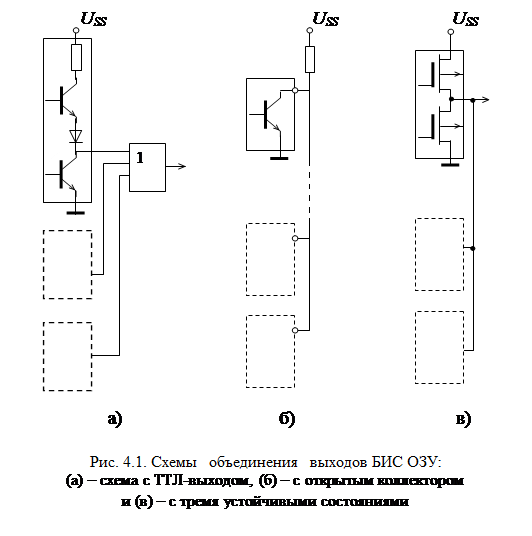

7) Организуют формирование информационных входных и выходных цепей модуля, для чего объединяются все одноименные информационные входы Di и выходы Qj БИС, входящих в один столбец матрицы накопителей. Объединение информационных входов производится непосредственно, объединение же информационных выходов зависит от типа выходных цепей БИС ОЗУ-Нк. БИС с ТТЛ-выходами, аналогичными выходами логических элементов ТТЛ, объединяются с помощью логической схемы ИЛИ (рис. 4.1, а). Выходы БИС с открытым коллектором объединяются по схеме монтажного ИЛИ (рис. 4.1, б), а выходы БИС с тремя устойчивыми состояниями объединяются непосредственно (рис. 4.1, в).

|

Для схем, имеющих выходы с открытым коллектором, значение сопротивления нагрузки должно находиться в пределах

Rн.мин £ Rн £ Rн.макс. (4.5)

Максимальное значение Rн.макс выбирается из условия, чтобы при формировании сигнала логической единицы падение напряжения (Uoh)на резисторе, определяемое протекающими по нему токами, не приводило к недопустимому уменьшению уровня напряжения логической единицы:

Rн.макс = (USS.мин - Uон.мин)/[IOH + pIIHн + (mc - 1)IО.ут], (4.6)

где Uон.мин- минимально допустимый уровень напряжения логической единицы; USS.мин- минимальное значение напряжения питания; IOH- выходные токи логической единицы БИС ОЗУ-Нк; IIHн- входные токи логической единицы микросхем нагрузки; IО.ут- выходные токи утечки БИС ОЗУ-Нк; р - число входов микросхем нагрузки, подключенных к одному информационному входу. Минимальное значение Rн.минвыбирают из условия, чтобы при формировании сигнала логического нуля падение напряжения на резисторе, определяемое протекающим по нему токами, обеспечило допустимый уровень логического нуля:

Rн.макс = (USS.макс – UOL.макс)/[IOL + pIILн + (mc - 1)IО.ут], (4.7)

где UOL.макс - максимально допустимый уровень напряжения логического нуля; USS.макс- максимальное значение напряжения питания; IOL- выходные токи логического нуля БИС ОЗУ-Нк; IILн - входные токи логического нуля микросхем нагрузки.

8) Организуют адресацию ячеек памяти по двухкоординатному принципу - выбор ряда матрицы накопителей осуществляется по входам выбора микросхем ВК, выбор же ячейки памяти в ряду - по адресным входам БИС. Для этого одноименные адресные входы Ai всех БИС ОЗУ-Нк объединяют. Из k = [log2N3У] адресных разрядов модуля ЗУ k1 = log2NНкразряд выделяют для адресации ячеек памяти в пределах одного ряда матрицы накопителей, а k2 = (k - k1)старших разрядов - для адресации рядов матрицы. Для реализации последней выбирают дешифратор k2-разрядного входного кода. Каждый выход дешифратора подключается к объединенным входам выбора микросхем ВК одного ряда матрицы накопителей.

9) Определяют токовую (IDL; IDH)иемкостную CD нагрузки для схем ввода информации в ЗУ с учетом того, что коэффициент разветвления для них определяется числом объединенных информационных входов БИС ОЗУ-Нк, тс:

IDL= тсIIDL; IDH = тсIIDH ; CD= mcCID+CмD, (4.8)

где Iidl, Iidh , CD - входные токи логического нуля и логической единицы и входная емкость по одному информационному входу БИС; CмD - монтажная емкость цепи информационного входа.

Для БИС ОЗУ с двунаправленными информационными выводами следует учитывать также входные токи микросхем нагрузки. В этом случае:

IDL= тсIIDL + pIIL, IDH = тсIIDH + pIIH, CD = mcCID + CмD CмQ + pCI , (4.9)

где IIL, Iih, CI - входные токи логического нуля и логической единицы и входная емкость микросхем нагрузки БЗУ; р - число входов микросхем нагрузки, подключенных к одному выходу БЗУ; CмQ - монтажная емкость цепи информационного выхода.

10) Определяют токовые Iql; IQм и емкостную CQ нагрузки по

информационным выходам БИС ОЗУ-Нк. Для схем, имеющих выходные цепи с тремя устойчивыми состояниями,

IQL = pIIL+(mc - 1)IQ ут , IH = pIIH + (mс - 1)IQ ут,

CQ = mг CQ.o + pCI + CмQ,(4.10)

где CQ.o - выходная емкость одного информационного выхода; CмQ - монтажная емкость цепи информационного выхода; IQ.ут - ток утечки невыбранного выхода.

Для микросхем с двунаправленными информационными выводами в качестве нагрузки следует учитывать также токи утечки IO.утсхем ввода информации в БЗУ и их выходную емкость CQО,так как они при выводе информации остаются подключенными к информационным выводам, но переводятся в высокоимпедансное состояние. В этом случае

Iql = pIIL + (mс - 1)IQ.ут+ IO.ут

IQH = pIIH + (mс - 1)IQ.ут+ IO.ут ; CQ = mсCQO + pCI + CмQ. (4.11)

11) Определяют токовые (IAL, IAН)и емкостную (СA)нагрузки по

выходам схем адресации с учетом того, что коэффициент разветвления для них определяют числом БИС ОЗУ-Нк в модуле т:

IAL = mIIA , IAH = mIIAH, CA = CIA + CмA, (4.12)

где IIAL, IIAH, CIA - входные токи логического нуля и логической единицы и входная емкость одного адресного входа БИС ОЗУ-Нк; CмA - монтажная емкость адресной цепи.

12) Находят токовые IDCL, IDCH и емкостную CDC нагрузки на

выходы дешифратора, учитывая, что коэффициент разветвления для них определяется числом БИС ОЗУ в ряду матрицы накопителей:

IDCL = mpIIBKL, IDCH = mрIIBKH, CDC = mрCIBK + CмBK, (4.13)

где IIBKL, IIBKH, CIBK- входные токи логического нуля и логической единицы и входная емкость входа выбора микросхемы ВК; CмBK- монтажная емкость цепи выбора микросхем.

Полученные в п.п. 9-12 нагрузки и емкости должны удовлетворять требованиям технических условий по нагрузке соответствующих микросхем. При несоблюдении этих условий необходимо включать схемы согласования.

13) Рассчитывают потребляемую мощность ЗУ:

PSS.ЗУ = PSS.НК + PSS.DC + PSS.согл, (4.14)

где PSS.НК, PSS.DC, PSS.согл- мощности, потребляемые всеми БИС ОЗУ-Нк, дешифратором и схемами согласования. Потребляемая мощность в режиме «Запись/Считывание» и в режиме хранения для многих микросхем ЗУ различна. Одновременно в режиме обращения к ЗУ могут находиться mрБИС ОЗУ, определяющие одну ячейку памяти БЗУ. Следовательно,

PSS.НК = mрPSS.W/R + (m - mр)PSS.M , (4.15)

где PSS.W/R , PSS.M - мощности, потребляемые БИС ОЗУ в режимах выборки и хранения.

14) Определяют временные параметры модуля БЗУ. Для правильного выполнения функций БИС ОЗУ необходима подача сигналов по различным входам с определенными сдвигами по времени, длительностям и периодам повторения.

| <== предыдущая лекция | | | следующая лекция ==> |

| Устройство синхронизации телевизионных СОИ | | | Малоразрядные цифровые и буквенно-цифровые средства отображения информации |

Дата добавления: 2017-05-02; просмотров: 1238;