Регистры и сдвиговые регистры

Отдельный триггер может использоваться для хранения одного бита информации. Однако для машин, которые должны обрабатывать слова данных, состоящие из множества битов (обычно 64), удобнее объединить группу триггеров в стандартную структуру, называемую регистром. Работа триггеров, входящих в состав регистра, синхронизируется общим тактовым входом. Поэтому данные записываются (загружаются) во все триггеры и считываются изо всех триггеров одновременно.

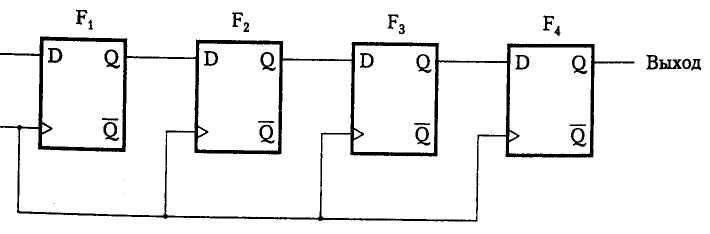

В ходе обработки цифровых данных часто требуется сдвинуть или циклически прокрутить значения группы битов данных. Реализуются эти операции аппаратно. Простейшим механизмом для их выполнения является регистр, содержимое которого легко может быть сдвинуто вправо или влево на одну позицию за раз. В качестве примера рассмотрим 4-разрядный сдвиговый регистр, показанный на рис. А.ЗЗ. Он состоит из четырех D-триггеров, соединенных таким образом, что каждый тактовый импульс вызывает перемещение содержимого триггера Fi в триггер Fi +1, в результате чего получается «сдвиг вправо». Данные следовательно «вдвигаются» в регистр и «выдвигаются» из него. Для выполнения циклического смещения данных достаточно соединить выход Out и вход In.

Для корректного функционирования сдвигового регистра необходимо, чтобы на каждый тактовый импульс его содержимое смещалось ровно на одну позицию. Это условие накладывает некоторые ограничения на запоминающие элементы, которые могут использоваться в сдвиговых регистрах. Например, вентильные защелки (рис. А.27) для этой цели не подходят. При высоком уровне тактового сигнала значение на входе D немедленно передается на выход, а оттуда — на следующую защелку. В результате количество сдвигов на один тактовый импульс никак не контролируется. Поэтому сдвиговые регистры создаются на основе двухступенчатых триггеров или триггеров, тактируемых фронтом сигнала.

Рис. 3.28. Простейший сдвиговый регистр.

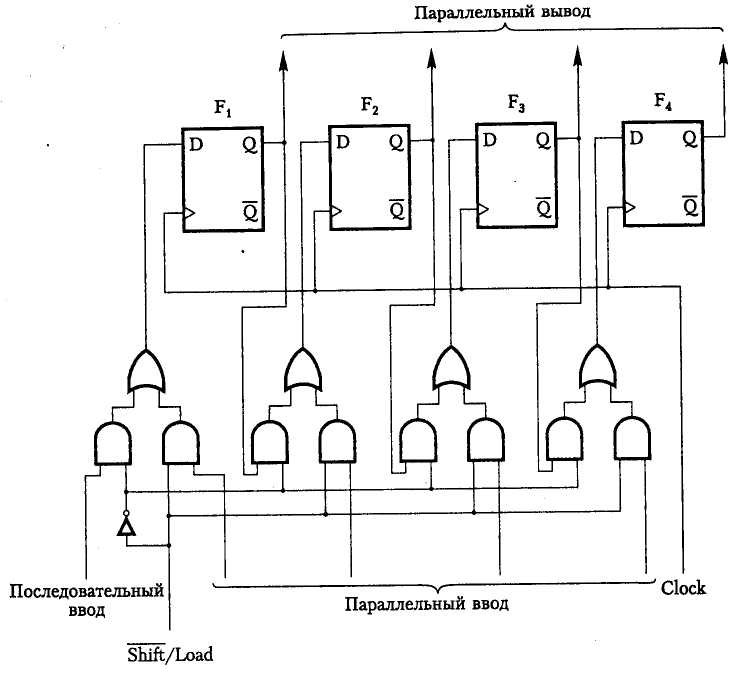

Интересной разновидностью сдвигового регистра является регистр, разряды которого могут считываться и загружаться параллельно. Для этого в него добавляются дополнительные вентильные схемы (рис. 3.29). Загрузка данного регистра выполняться как последовательно, так и параллельно. Когда на тактовый вход регистра подается очередной импульс, при условии, что Shift/Load =0, выполняется сдвиг, а в противном случае — параллельная загрузка регистра.

Рис. 3.29. Сдвиговый регистр с параллельным доступом

Счетчики

В предыдущем разделе рассказывалось о применении триггеров для создания сдвиговых регистров. Кроме того, триггеры используются в схемах счетчиков. Пожалуй, не нужно объяснять, для чего в цифровых компьютерах нужны счетчики. Но здесь речь идет не только об аппаратном механизме для выполнения обычных счетных функций — с их помощью можно также генерировать управляющие и тактирующие сигналы. Счетчик, управляемый высокочастотным тактовым сигналом, может использоваться для выдачи более редких сигналов кратной частоты. Такие счетчики называются делителями частоты.

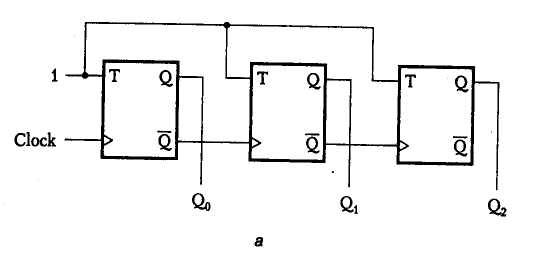

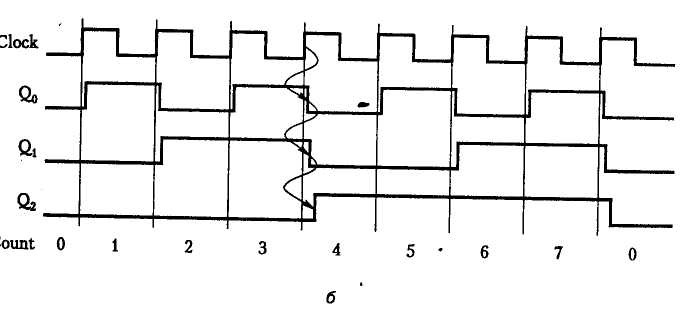

Простейший трехступенчатый (или 3-разрядный) счетчик конструируется на основе Т-триггера (рис. А.35). Напомним, что когда на вход Т подается значение 1, триггер действует как переключатель, то есть его состояние изменяется при подаче каждого тактового импульса. Два последовательных тактовых импульса приводят к изменению выхода Q0 — из состояния 1 в состояние 0 и опять в состояние 1 или же из состояния 0 в состояние 1 и опять в 0. Таким образом, частота изменения выходного сигнала Q0 будет вдвое меньшей, чем частота входного так-то сигнала. А в связи с тем, что второй триггер тактируется сигналом Q0 частота изменения его выходного сигнала Q1 будет вдвое меньшей, чем частота О0 и вчетверо меньшей, чем частота исходного тактового сигнала. В данном примере полагается тактирование всех трех триггеров положительным фронтом

Рис. 3.30. 3-разрядный счетчик прямого счета: схема (а); временная диаграмма (б)

Такой счетчик называют счетчиком со сквозным переносом или волнообразным счетчиком (ripple counter), поскольку входной тактовый сигнал волнообразно распространяется по его схеме. Например, положительный фронт импульса 4 меняет сигнал 1 на выходе Q0 на 0. Это изменение на выходе Qo, в свою очередь, вызывает изменение сигнала на выходе Q1 — из 1 в 0, что опять-таки, изменяет сигнал Q2 — из 0 в 1. Если в каждом триггере происходит некоторая задержка D, то задержка перед установкой сигнала на выходе О2 составляет уже 3D. Если от счетчика требуется очень высокая скорость работы, подобная задержка может вызывать проблему.

Однако время задержки по сравнению с тактовой частотой, как правило, очень мало, поэтому им можно пренебречь.

Добавив еще несколько логических вентилей, можно сконструировать синхронный счетчик, в котором все ступени будут управляться общим тактовым сигналом, так что состояния всех триггеров будут изменяться одновременно. Такие счетчики способны функционировать с очень высокой скоростью, поскольку общее время задержки на распространение сигнала в них существенно сокращено.

В противоположность им счетчики такой конструкции, как на рис. 3.30, называются асинхронными.

Упражнения

3.15. Последовательные устройства содержат элементы, называемые

3.16. Элементом памяти, который позволяет размещать данные, является обычно ___.

3.17. D-триггер называется также триггером______________________ .

3.18.______ Нормальным выходом триггера является выход _____ (Q,  ).

).

3.19. Перечислить три функциональных состояния D-триггера на рис. 3.10.

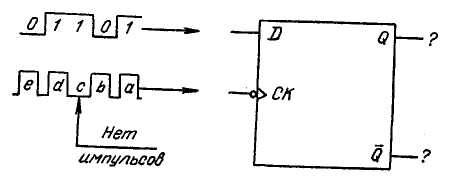

3.20. Назвать функциональные состояния D –триггера, приведенного на рис. 3.31, соответствующие каждому тактовому импульсу.

|

Рис. 3.31. К упражнениям 3.20 и 3.21

3.21. Перечислить двоичные значения на выходе Q D-триггера на рис. 3.31 после каждого тактового импульса.

3.22. Защелка — это устройство _________________ (размещения, расчета) данных.

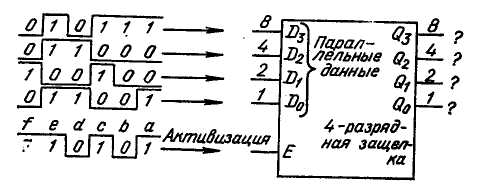

3.23. Входом активизации такой 4-разрядной защелки является логический сигнал (0,1).

3.24. Перечислить двоичные 4-разрядные числа на выходах защелки на рис. 3.32.

|

рис.3.32.

3.25. Перечислить четыре функциональных режима JK –триггера на рис. 3.25.

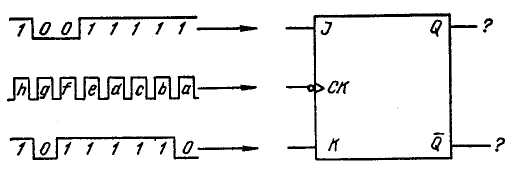

3.26. Перечислить режимы JK –триггера (рис. 3.25), соответствующие каждому тактовому импульсу.

3.27. Перечислить двоичные состояния на нормальном выходе Q JK –триггера на рис. 3.33 после каждого тактового импульса.

Рис. 3.33. К упражнениям 3.26 и 3.27

3.28. См. рис. 3.20. D-триггер является устройством, запускаемым _____ (уровнем, фронтом) импульсов.

3.29. См. рис. 3.25. Этот JK –триггер является устройством, запускаемым фронтом ___ (положительных, отрицательных) импульсов.

3.30. См. рис. 3.21. Такая 4-разрядная защёлка является элементом, включаемым импульсов.

Решения

3.15. Триггерами. 3.16. Триггер. 3.17. Данных. Иногда его называют триггером временной задержки. 3.18. Q. Выход  — инверсный. 3.19. Установка, сброс, ожидание. 3.20. См. таблицу истинности (табл. 3.6): импульс а — установка; импульс б — сброс; время с (нет импульсов) — ожидание; импульс d— установка; импульс е — сброс. 3.21. См. табл. 3.6. импульс а—1; импульс b - 0; время с (нет импульсов)—0; импульс d — 1; импульс е — 0. 3.22. Размещения. 3.23. См. табл. 3.7. Логической 1 (Н-сигналом). 3.24. См. табл. 3.7: импульс а—1001; импульс b —1001 (данные, соответствующие импульсу а, захвачены до того, как вход перешел от 1 к 0); импульс с— 1010; импульс d— 1010 (данные, соответствующие импульсу с захвачены до того, как изменилось состояние входов D3, D2, D1, Do); импульс е—1101; импульс f — 0010. 3.25. См. табл. 3.8. Режимы: триггера, установки, сброса, ожидания. 3.26. См. табл. 3.8: импульс а — установка; импульс б — триггер; импульс с — триггер; импульс d—триггер; импульс е — триггер; импульс f —сброс; импульс g—ожидание; импульс h—ожидание. 3.27. См. табл. 3.8, после импульса а — установка, 1;после импульса b — триггер, 0; после импульса с — триггер, 1; после импульса d — триггер, 0; после импульса е —триггер, 1; после импульса f— сброс, 0; после импульса g — ожидание, 0; после импульса h — триггер, 1. 3.28. Положительным фронтом импульса (при переходе от L к Н). 3.29. Отрицательных (при переходе от Н к L). 3.30. Уровнем.

— инверсный. 3.19. Установка, сброс, ожидание. 3.20. См. таблицу истинности (табл. 3.6): импульс а — установка; импульс б — сброс; время с (нет импульсов) — ожидание; импульс d— установка; импульс е — сброс. 3.21. См. табл. 3.6. импульс а—1; импульс b - 0; время с (нет импульсов)—0; импульс d — 1; импульс е — 0. 3.22. Размещения. 3.23. См. табл. 3.7. Логической 1 (Н-сигналом). 3.24. См. табл. 3.7: импульс а—1001; импульс b —1001 (данные, соответствующие импульсу а, захвачены до того, как вход перешел от 1 к 0); импульс с— 1010; импульс d— 1010 (данные, соответствующие импульсу с захвачены до того, как изменилось состояние входов D3, D2, D1, Do); импульс е—1101; импульс f — 0010. 3.25. См. табл. 3.8. Режимы: триггера, установки, сброса, ожидания. 3.26. См. табл. 3.8: импульс а — установка; импульс б — триггер; импульс с — триггер; импульс d—триггер; импульс е — триггер; импульс f —сброс; импульс g—ожидание; импульс h—ожидание. 3.27. См. табл. 3.8, после импульса а — установка, 1;после импульса b — триггер, 0; после импульса с — триггер, 1; после импульса d — триггер, 0; после импульса е —триггер, 1; после импульса f— сброс, 0; после импульса g — ожидание, 0; после импульса h — триггер, 1. 3.28. Положительным фронтом импульса (при переходе от L к Н). 3.29. Отрицательных (при переходе от Н к L). 3.30. Уровнем.

Лекция 17

Дата добавления: 2016-07-05; просмотров: 4940;