Схемное построение логических элементов

Различают схемы: диодной логики (ДЛ)

диодно - транзисторной (ДТЛ)

транзисторно - транзисторной логики ( ТТЛ )

Схемотехника диодной логики (ДЛ).

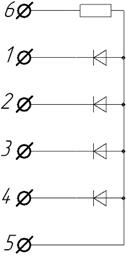

Схемы ДЛ строят на полупроводниковых диодах в комбинации с резисторами. На рис. 1.6 приведена ½ микросхемы ДЛ.

Рис. 1.6. ½ микросхемы К 194 ЛИ1

В зависимости от схемы включения и кодирования сигналов можно получить логические функции ИЛИ или И.

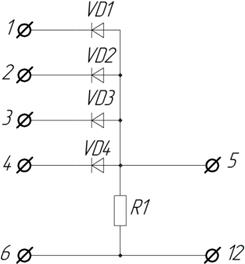

Для образования логического элемента ИЛИ необходимо кодировать сигналы следующим образом : Логическая единица – высокий отрицательный потенциал, логический нуль – нулевой потенциал. Логический элемент ИЛИ примет вид, изображенный на рис. 1.7.

Рис. 1.7 Логический элемент ИЛИ на ДЛ

Работа схемы «ИЛИ»: при воздействии сигнала «Лог.1», т.е. (-Е) хотя бы на один вход, открывается соответствующий диод VD1 – VD4 и на выходе (5) появляется отрицательное напряжение входного сигнала, уменьшенное на величину падения напряжения на открытом диоде.

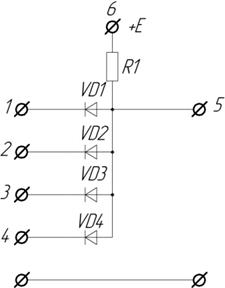

Если изменить кодировку сигналов, а именно: Логической единицей считать высокий положительный уровень напряжения, а нулём – нуль или небольшое отрицательное напряжение, то те же элементы микросхемы, будучи соединенными по схеме, представленной на рис. 1.8, будут осуществлять выполнение функции И.

Рис. 1.8 Логический элемент И на ДЛ

Работа схемы «И». Если хотя бы на одном входе схемы имеется низкий уровень напряжения, принимаемый за условный «0», то диод, связанный через катод с этим входом, открыт. Ток от источника +Е через токоограничительный резистор R1 стекает через открытый диод поэтому напряжение на его аноде, следовательно, и на выходе (клемма 5) равно 0. Если на все входы, т.е. на катоды диодов подать лог.1 – положительный потенциал, то все диоды «запираются», ток от источника +Е не может больше стекать через диоды, а на выходе (клемма 5) напряжение приближается к +Е, что соответствует логической 1.

Достоинства схем ДЛ: простота устройства, возможность расширения, помехоустойчивость.

Недостатки: 1) Значительное потребление тока;

2) Падение амплитуды сигнала при прохождении через ДЛ;

3) Ограниченные возможности (только схемы И и ИЛИ, нет НЕ)

Микросхемы ДЛ широко использовались в ЭВМ типа ЕС, в настоящее время имеют ограниченное применение.

Схемотехника диодно - транзисторной логики (ДТЛ).

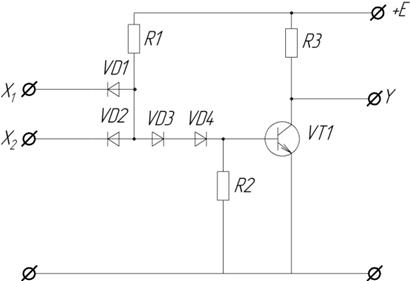

Схема базового элемента ДТЛ приведена на рис. 1.9.

Рис. 1.9 Схема базового логического элемента ДТЛ

Разбор схемы:

Входная часть

и

и  - это уже знакомая нам диодная логика, производящая обработку входных сигналов по схемам И/ИЛИ (в зависимости от кодирования сигналов)

- это уже знакомая нам диодная логика, производящая обработку входных сигналов по схемам И/ИЛИ (в зависимости от кодирования сигналов)

V  и V

и V  осуществляют связь входной части и транзистора

осуществляют связь входной части и транзистора

,

,  простой инвертор.

простой инвертор.

В зависимости от кодирования сигналов схема выполняет функции И-НЕ и ИЛИ-НЕ.

1. И-НЕ. В этом случае схема кодирования сигналов должна отвечать следующим условиям: логический «0» - низкий уровень входного напряжения (близкий к нулю), логическая «1» - высокий положительный уровень напряжения.

Работа: При подаче на один или оба входа логического «0», потенциал точки А снижается, но остается положительным. Диоды V  и V

и V  обеспечивают снижение потенциала точки В до небольшого отрицательного значения, что гарантирует надежное «запирание» транзистора

обеспечивают снижение потенциала точки В до небольшого отрицательного значения, что гарантирует надежное «запирание» транзистора  Потенциал точки С большой, что соответствует логической «1» на выходе Y.

Потенциал точки С большой, что соответствует логической «1» на выходе Y.

Если на обоих входах логическая «1», то  и

и  заперты, потенциал точки А повышается, соответственно повышается и потенциал точки В, что вызывает «отпирание» транзистора

заперты, потенциал точки А повышается, соответственно повышается и потенциал точки В, что вызывает «отпирание» транзистора  . На выходе, то есть в точке С потенциал уменьшается, что соответствует логическому «0».

. На выходе, то есть в точке С потенциал уменьшается, что соответствует логическому «0».

2. ИЛИ-НЕ. В этом случае схема кодирования сигнала должна осуществляться по следующей схеме: логический «0» - это высокий положительный потенциал, а «1» - это физический нуль.

Работа: При подаче на оба входа логического «0»,

заперты. Потенциал точек А и В высокий, поэтому транзистор

заперты. Потенциал точек А и В высокий, поэтому транзистор  открыт и находится в режиме насыщения. Напряжение на коллекторе транзистора значительно снижается, что соответствует по принятой схеме кодирования сигналов логической «1».

открыт и находится в режиме насыщения. Напряжение на коллекторе транзистора значительно снижается, что соответствует по принятой схеме кодирования сигналов логической «1».

Если хотя бы на один из входов подать логическую «1», потенциалы точек А и В упадут, транзистор  перейдет в режим отсечки и потенциал точки С поднимется до значения логического «0».

перейдет в режим отсечки и потенциал точки С поднимется до значения логического «0».

Достоинство ДТЛ: транзистор кроме операции инвертирования, выполняет и роль усилителя, следовательно, нагрузочная способность увеличивается.

Типичные представители серии ДТЛ – серии 156, К511.

ТТЛ – элементы (транзисторно-транзисторная логика)

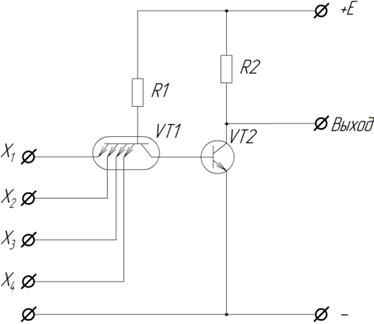

Схема базового элемента ТТЛ приведена на рис. 1.10.

Рис. 1.10 Базовый элемент И-НЕ ТТЛ с простым инвертором

После перехода к широкому выпуску интегральных полупроводниковых микросхем ДТЛ, довольно быстро выяснилось, что для улучшения электрических параметров цифровых микросхем выгоднее заменить матрицу входных диодов VD1 – VD2 (рис. 1.9) многоэмиттерным транзистором VT1 в схеме ТТЛ элемента (рис.10). Поэтому название ДТЛ трансформировалось в ТТЛ. Четыре p-n перехода транзистора VT1 образуют матрицу диодов, соответствующую диодам VD1 – VD4 (рис. 1.6).

Схема может реализовать как функцию И так и ИЛИ (при смене кодировки сигнала), однако это вызывает большие неудобства в пределах одной серии. Поэтому схему используют только в качестве логического элемента И-НЕ при следующей кодировке: логический «0» - низкий уровень напряжения, логическая «1» - высокий потенциал, а образование логической структуры ИЛИ-НЕ осуществляют параллельным соединением элементов схемы И-НЕ.

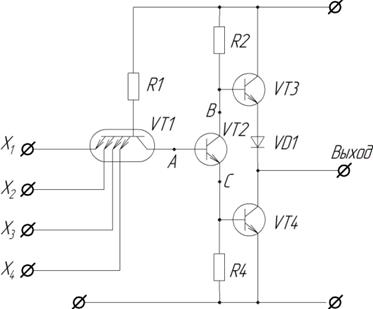

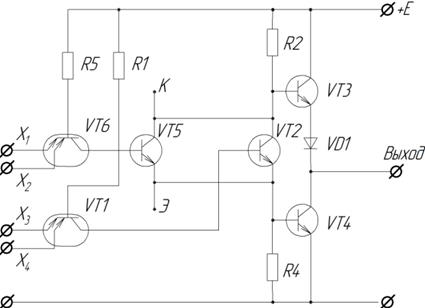

Реальные схемы И-НЕ выполняются со сложным инвертором, позволяющим увеличить нагрузочную способность элемента (рис. 1.11).

Рис. 1.11 Элемент И-НЕ ТТЛ со сложным инвертором

Работа. Схема содержит три каскада: входной (многоэмиттерный транзистор VT1 и резистор R1), фазорасщепительный (транзистор VT2, резисторы R2 и R4), выходной (транзисторы VT 3 и VT4, резистор R3 и диод VD1).

Когда один или несколько входов соединены с общей шиной, что соответствует подаче логических нулей, соответствующие эмиттерные переходы транзистора VT1 окажутся смещены в прямом направлении, поскольку потенциал базы выше потенциала эмиттера. Напряжения на базе VT1, равного ≈ 0,3-0,7 В, недостаточно для отпирания трех переходов: коллекторного VT1 и двух эмиттерных - VT2 и VT5.

Когда второй каскад (транзистор VT2) заперт, на его коллекторе – высокое напряжение. Ток, протекающий через резистор R2, обеспечивает отпирание транзистора VT3 и диода VD1. Если при этом отсутствует нагрузка между выходным выводом и общей шиной, ток через VT3 и диод VD1 мал, а выходное напряжение ≈ равно 3,6В, что соответствует логической «1».

При логической «1» на всех входах  открывается, открывая VT3, а VT4 закрыт низким потенциалом точки В. Поэтому на выходе Y будет низкий потенциал, что соответствует логическому «0». Базовой ИС серии 155 является логическая схема 155ЛА (И-НЕ 18 модификаций).

открывается, открывая VT3, а VT4 закрыт низким потенциалом точки В. Поэтому на выходе Y будет низкий потенциал, что соответствует логическому «0». Базовой ИС серии 155 является логическая схема 155ЛА (И-НЕ 18 модификаций).

Преимущества ТТЛ перед ДТЛ:

- высокое быстродействие;

- большая нагрузочная способность.

Недостатки:

- большее потребление энергии.

Рассмотренная схема И-НЕ относится к так называемым ИС с закрытым выходом.

Кроме них выпускается ИС с открытым выходом.

Схема И-НЕ с открытым выходом приведена на рис. 1.12.

Рис. 1.12 Логический элемент ТТЛ с открытым коллектором

На выходе формируется только сигнал низкого уровня, поэтому для нормальной работы выходного транзистора коллектор следует подключать к источнику питания напряжением до 30 вольт через внешнюю нагрузку: резистор, элемент индикации, обмотку реле и т.п.

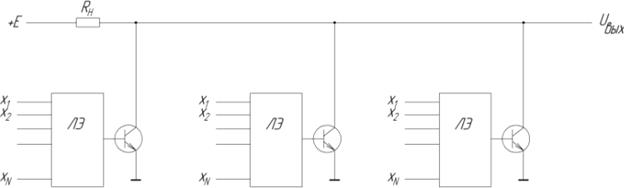

Другое применение подобных микросхем связано с выполнением логических операций. Логические элементы с открытым коллектором в отличие от сложных инверторов допускают параллельное соединение нескольких выходов к общей нагрузке (рис. 1.13).

Рис. 1.13 Схема псевдоэлемента «монтажное И»

При таком соединении, если на выходе одного или нескольких элементов будет низкий потенциал, тот же потенциал окажется на выходе всей системы. Чтобы обеспечить логическую «1» на общем выходе, необходимо иметь логические «1» на всех выходах. Другими словами, в данном случае параллельным подключением нескольких открытых коллекторов к общей нагрузке создается система , выполняющая логическую операцию И (монтажное И). Выход с открытым коллектором помечают специальным значком ( ◊ - ромбик). Типичными представителями класса элементов с открытым коллектором являются К155ЛА7, К155ЛА11, К155ИД1 и т. п.

Если питание общее +5В

При введении R=3,3 и уровень лог.1 повышается.

Используются для интерфейса: передатчики, приемники.

Схема передачи данных по витой паре с волновым сопротивлением Z = 100 Ом.

Схема И-ИЛИ-НЕ

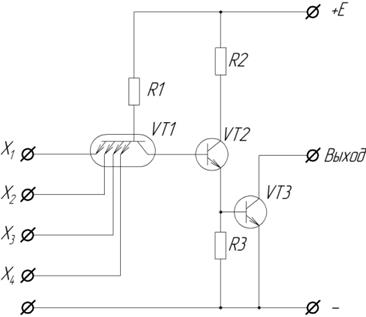

Схема универсального логического элемента И-ИЛИ-НЕ приведена на рис. 1.14.

Рис. 1.14 Схема элемента И-ИЛИ-НЕ

Содержит несколько многоэмиттерных транзисторов (на рис. 1.14 их два – VT1 и VT6). Часть схемы (VT1-VT4, VD1, R1-R4) это обычная схема И-НЕ со сложным инвертором (рис. 1.11). Для увеличения логических возможностей, то есть получения функции ИЛИ, добавлено еще два транзистора: VT5 и VT6. Многоэмиттерный транзистор VT6 осуществляет схему двухвходового логического элемента И, а VT5, включенный параллельноVT2, роль фазорасщепителя. Как видно из схемы, коллекторы и эмиттеры обоих фазорасщепительных транзисторов VT2 и VT5 соединены между собой и выведены из микросхемы в виде дополнительных выводов, предназначенных для расширения по ИЛИ. Оба транзистора VT2 и VT5 имеют одну и ту же нагрузку и «отпирание» любого из них «запирает» выходной транзистор VT4 и «отпирает» VT3.

Очевидно, чтобы получить от элемента функцию ИЛИ-НЕ необходимо замкнуть между собой входы

,

,

и на эти объединенные входы подавать два логических сигнала

и на эти объединенные входы подавать два логических сигнала

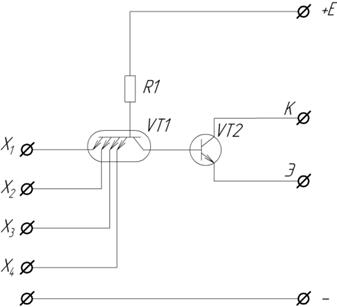

Таким образом в этом случае схема будет выполнять функцию двухвходового элемента ИЛИ-НЕ. Учитывая, что объединенные выводы коллекторов и эмиттеров фазорасщепительных транзисторов выведены из микросхемы, можно увеличить число входов по ИЛИ (расширить по ИЛИ) путем присоединения, так называемых, расширителей по ИЛИ (рис. 1.15).

Таким образом в этом случае схема будет выполнять функцию двухвходового элемента ИЛИ-НЕ. Учитывая, что объединенные выводы коллекторов и эмиттеров фазорасщепительных транзисторов выведены из микросхемы, можно увеличить число входов по ИЛИ (расширить по ИЛИ) путем присоединения, так называемых, расширителей по ИЛИ (рис. 1.15).

Рис. 1.15 Схема расширителя по ИЛИ

Это многоэмиттерный транзистор VT1 и соединенный с ним транзистор VT2.

Модификации: К155ЛД1 содержит два четырехвходовых элемента, у которых сделаны выходы от коллекторов и эмиттеров. У микросхемы К155ЛД3 аналогичные выводы К и Э имеет восьмивходовой элемент.

Дата добавления: 2017-05-02; просмотров: 3686;