Принципы функционирования цифровых устройств комбинационной логики.

Этот вопрос рассмотрим на примере логических устройств, применяемых в вычислительных системах. К ним относят цифровые устройства: сумматоры, шифраторы, дешифраторы, мультиплексоры и демультиплексоры, компараторы и др.

Сумматор — логическое устройство, предназначенное для сложения чисел, подставленных в двоичной форме. Для этого в каждом из разрядов применяют одноразрядный суммирующий элемент (рис. 13.8) на три входа: два — для слагаемых x1 и x2 данного разряда, а третий (y1) — для переноса 1 из соседнего младшего разряда. Устройство снабжают двумя выходами: по одному (S) выдается искомая сумма x1+x2, а по другому (Р) переносится 1 в соседний старший разряд.

Для сложения двоичных чисел с несколькими разрядами используют двух- и трехразрядные сумматоры с последовательным переносом 1 в старшие разряды (например, микросхемы К155ИМ2 и К155ИМЗ соответственно). Быстродействие сумматоров последовательного действия лимитируется временем переноса 1 через все элементы устройства. Для улучшения этого показателя применяют сумматоры с параллельным переносом (например, К155ИП4).

Рис. 13.8. Условное обозначение сумматора

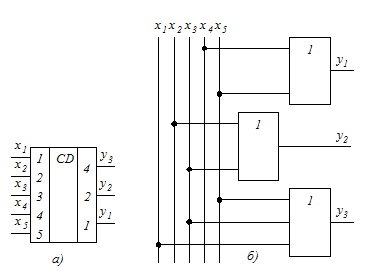

Шифратор (кодер) — логическое устройство с n входами и m выходами, преобразующее входные одиночные сигналы, соответствующие логической 1, в m-разрядный двоичный код на выходе. Для шифратора, показанного условно на рис. 13.9, а (n=5, m=3), задают следующую таблицу истинности (табл. 13.6).

Функциональная схема, реализующая на элементах ИЛИ приведенную в табл. 13.6 программу работы шифратора, представлена на рис. 13.9, б.

Рис. 13.9. Условное обозначение шифратора (а) и его функциональная схема на элементах ИЛИ (б)

Таблица 13.6 Программа работы шифратора (n=5, m=3)

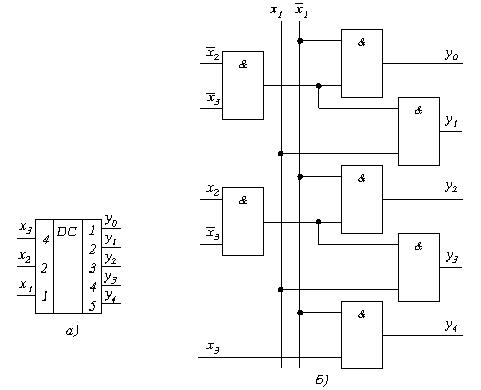

Дешифратор (декодер) — логическое устройство (рис. 13.10, а), выполняющее операцию обратного преобразования n-элементного входного двоичного кода в одиночные сигналы, соответствующие логической 1 на его выходах. Так как на n входах можно получить в двоичном коде наборов, то число выходов дешифратора не должно превышать эту величину. Дешифратор, условное обозначение которого показано на рис. 13.10, а (n=3; m=5), имеет топологию, обратную топологии рассмотренного ранее шифратора (рис. 13.9, а). Поэтому и таблица истинности такого дешифратора (табл. 13.7) имеет структуру, обратную таблице истинности (см. табл. 13.6) рассмотренного шифратора.

Рис. 13.10. Условное обозначение дешифратора (а) и его функциональная схема на элементах И (б)

Таблица 13.7 Программа работы дешифратора (n=3; m=5)

Функциональная схема дешифратора, реализующая на элементах И заданную программу (см. табл. 13.7), приведена на рис. 13.10, б.

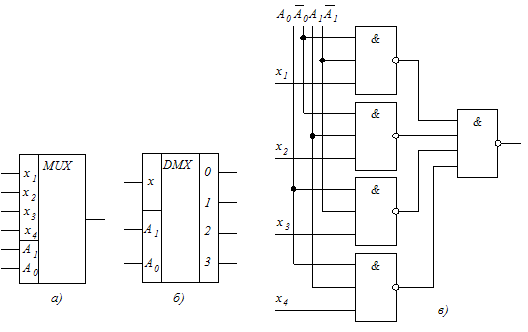

Мультиплексор — логическое устройство, предназначенное для управляемой передачи данных от нескольких входных цепей в общий выходной канал. Он снабжается двумя группами входов: адресными и информационными. Сигнал, поступающий на адресный вход мультиплексора, определяет, какой из информационных входов в данный момент подключен к его выходу. Поэтому число адресных (А) и информационных (Х) входов мультиплексора связано соотношением X=2A.

На рис. 13.11 приведены условное обозначение мультиплексора и логическая схема, реализующая алгоритм его работы.

Демультиплексор — логическое устройство, предназначенное для управляемой передачи данных от одной входной цепи в несколько выходных. Принцип его действия противоположен принципу работы мультиплексора. Поэтому он кроме адресных содержит единственный информационный вход и 2A выходов. По адресному сигналу вход демультиплексора подключается к соответствующему выходу. Как следует из сказанного, по выполняемым функциям демультиплексор аналогичен дешифратору. Отличие состоит лишь в том, что по заданному адресу на выбранном выходе дешифратора появляется строго определенный сигнал, а в демультиплексоре — тот же сигнал, что и на его входе. Условное обозначение демультиплексора приведено на рис. 13.11, б.

Рис. 13.11. Условные обозначения мультиплексора (а) и демультиплексора (б) и логическая схема мультиплексора (в), реализующая алгоритм его работы

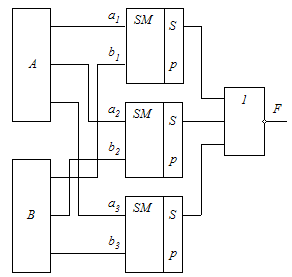

Компаратор (цифровой) — логическое устройство, обеспечивающее сравнение двух многоразрядных двоичных чисел А и В, разряды каждого из которых подаются порознь на его входы (рис. 13.12). На практике одно из чисел (например, А) является неизменным, а другое (В) изменяет свое значение от такта к такту. В момент равенства их значений на выходе компаратора формируется сигнал 1.

Рис. 13.12. Функциональная схема цифрового компаратора для сравнения двоичных чисел А и В

Дата добавления: 2017-01-26; просмотров: 2077;