Триггеры: общая структура и классификация. Назначение и принцип действия триггеров типа: RS-, D-, JK-, Т-.

Разновидности функциональных схем:

- комбинационные схемы

- последовательные устройства

Комбинационные схемы характеризуются отсутствием памяти (память – свойство системы сохранять в течении требуемого времени значение сигнала, характеризующее внутреннее состояние цифрового устройства). Сигнал на выходе комбинационного устройства в любой момент времени однозначно определяется сочетанием сигналов на входе и не зависит от его предыдущего состояния. Схемным признаком таких схем является осуществление в цепи обратной связи. Примеры: логические элементы, эл. ключи, дешифраторы, арифметические устройства.

Последовательные схемы обладают памятью и при смене цифр на входе, для предсказания сигнала на выходе, необходимо знать о состоянии, в котором устройство было до этого. В этих устройствах есть обратная связь. Простейшие из них – триггеры, счетчики, резисторы, запоминающие устройства.

Триггеры – класс устройств, общим свойством которых является способность длительно оставаться в одном из двух (или нескольких возможных) устойчивых состояний и скачком чередовать их под воздействием внешних сигналов. Одно из основных применений – запоминание информации.

Под памятью триггера подразумевают способность оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит или помнит один разряд двоичного числа.

|

| ||||

| Rn | Sn | Q |

| ||

|

| ||||

| н/о | н/о | ||||

| н/о | н/о | ||||

|

| ||||

Недостаток: неопределенное состояние.

Для исключения неопределенного состояния разработаны модификации RS-триггеров, у которых при запрещенных входных комбинациях выходной сигнал принимает следующие значения:

R-триггер - 0

S-триггер - 1

E-триггер – Qn

JK-триггер -

Триггерные системы - RS-триггер как ячейка памяти и УУ.

J, K, V, (T)C – внешние входы; Ra, Sa – внешние входы ячейки памяти; Q,  - внешние выходы; S', R' – внутренние входы.

- внешние выходы; S', R' – внутренние входы.

Функциональное назначение внешних входов

| усл. обозн. | назначение |

| информационные входы | |

| S | вход раздельной установки триггера в состоянии «1» |

| R | вход раздельной установки триггера в состоянии «0» |

| J | вход установки JK-триггера в состоянии «1» |

| K | вход установки JK-триггера в состоянии «0» |

| T | вход счетного триггера |

| D | вход установки D- или DV-триггера в состоянии «1» или «0» |

| управляющие входы | |

| V | подготовительный вход разрешения приема информации |

| C | вход синхронизации (тактирующий) |

УУ – комбинационное устройство, преобразующее входную информацию в комбинацию сигналов под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний. Изменяя схему УУ и способы ее связи с ячейкой памяти можно получить триггеры с различными функциональными свойствами. Сигнал на информационном входе определяется информацией, которая будет записываться с триггер. С помощью подготовительного сигнала можно в нужный момент прервать действие триггера или группы триггеров, сохраняя информацию на выходе (V-сигнал). Исполнительные сигналы (С-сигнал) задают момент приема входной информации и служат для синхронной работы ряда устройств, образующих функциональные узлы.

Асинхронные и синхронные триггеры

По способу ввода информации бывают асинхронные и синхронные триггеры.

Асинхронные триггеры имеют только информационный вход и срабатывают непосредственно за изменением сигналов на входе.

У синхронных триггеров смены информации на информационных входах недостаточно для срабатывания. Необходим дополнительный импульс, подаваемый на тактирующий вход.

Синхронные сигналы вырабатывают специальными генераторами тактирующих импульсов, которые задают частоту смены информации.

Основной недостаток – незащищенность перед опасными состязаниями сигналов, то есть возникновение временных сдвигов из-за различных задержек распространения сигнала, проходящего по различным цепям, низкая помехоустойчивость.

Срабатывание синхронных триггеров происходит при поступлении тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входной сигнал триггер не реагирует, то есть, по сравнению с асинхронным, обладает более высокой помехоустойчивостью.

Способы управления, в зависимости от параметра синхронного входа сигнала, используемых для записи информации, триггеры бывают:

1) со статическим управлением записью (управление по уровню входного сигнала);

2) с динамическим управлением записью (по фронту или срезу);

3) двухступенчатое управление.

Способ управления со статическим управлением записью имеет недостаток – триггер в период действия синхронного импульса ведет себя подобно асинхронному. Срабатывает в момент, когда входной сигнал достигает порогового уровня, то есть продолжает действие тактового импульса. Смена сигнала на информационный вход вызывает новое срабатывание.

При динамическом управлении по фронту или по спаду тактового импульса триггер переключается только при переходе от 0 к 1, или от 1 к 0.

Возможность задержки момента опрокидывания триггера на время длительности тактового импульса позволяют по фронту производить считывание, а по срезу – запись информации.

Двухступенчатые триггеры содержат две ячейки памяти, запись информации в которые происходит последовательно в различные моменты времени. Эту структуру называют «ведущий-ведомый» или MS-структура (Master-Slave).

Первая ступень – промежуточная запись входной информации. Вторая ступень – последовательная запись и хранение.

Формирование нового состояния происходит за два такта.

Ввод информации в ведущую ступень происходит с приходом С1. Перезапись соответственно из ведущего в ведомый – с приходом С2, в это же время происходит обновление информации на Q или  .

.

Управлять можно и одним тактовым импульсом. Запись в ведущую по фронту 0-1, перезапись в ведомую – по фронту 1-0.

Динамические двухступенчатые триггеры называют флип-флоп. Статические – лэт.

Асинхронные RS-триггеры.

|

| V |

|

| |||

| Х | |||

| Х | Х | Z |

X – не имеет значения

Z – высокоимпедансное значение выхода (выход отключен от обеих шин источника питания и выходных клемм)

Отсутствие запрещенного состояния обусловлено тем, что не введены выводы  .

.

Синхронные RS-триггеры.

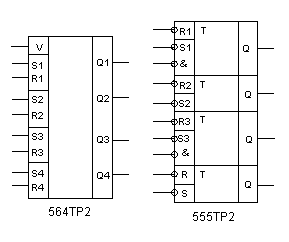

При С = 0 на выходах DD2 и DD1 логическая «1» и RS-триггер на DD3 и DD4 находится в состоянии хранения информации (и не реагирует на изменение R и S). При С = 1, информация на управляющих входах RS-триггера зависит от состояния входа R и S, проинвертированных DD2 и DD1. Входы Sa¯ и Ra¯ предназначены для асинхронной установки триггера в заданное состояние.

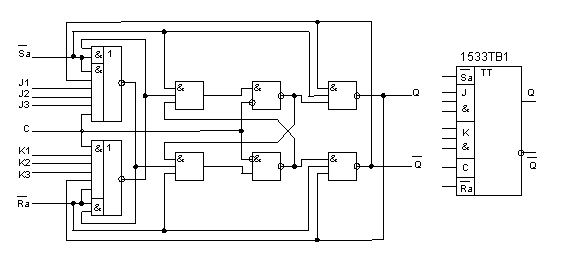

JK-триггеры

JK-триггеры не имеют неопределенных состояний. При всех входных комбинациях, кроме J = K = 1, они действуют подобно RS-триггеру. Причем J играет роль S, а К=R.

При J=K=1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение.

JK-триггеры относятся к универсальным устройствам (регистры, счетчики, делители), но кроме того, путем определенных соединений выводов, легко преобразуются в триггеры других типов.

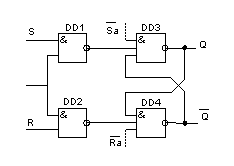

По схеме JK-триггеры отличаются от RS-триггеров наличием обратной связи с выхода на вход, поэтому состояние JK-триггера зависит не только от сигналов на входах J и K, но и от логической связи с ними сигнала с выходов Q и Q¯. Элементы временной задержки играют роль стабилизированного состояния триггера и на его функциональные свойства не влияют. Назначение – создание временного сдвига между моментом ввода входной информации JnQn¯ или KnQn и начала выхода Qn+1 и Qn+1¯.

Без этих цепей во время действия комбинации Jn = Kn = 1 началась бы генерация для предотвращения которой задержка должна быть превыше длительности тактирующих импульсов.

Действие JK-триггера: Qn+1 = Jn Qn¯VKn¯Qn.

Триггер организован по принципу ведущий-ведомый и имеет по 3 входа J и K, связанных операцией &, синхронный вход С, а также асинхронные входы  и

и  для установки триггера в состояние «0» и «1» независимо от сигналов информационных и тактовых входов.

для установки триггера в состояние «0» и «1» независимо от сигналов информационных и тактовых входов.

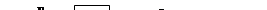

1553ТВ6 – 1553ТВ9

У ТВ6 отсутствует вход  , у ТВ10 отсутствует вход

, у ТВ10 отсутствует вход  . У ТВ11 объединены входы С и

. У ТВ11 объединены входы С и  для двух триггеров. У ТВ15 – вход

для двух триггеров. У ТВ15 – вход  , что позволяет преобразовывать эти триггеры путем объединения J и

, что позволяет преобразовывать эти триггеры путем объединения J и  .

.

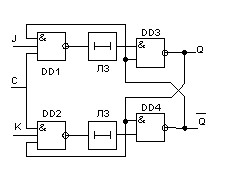

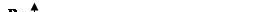

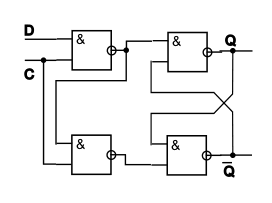

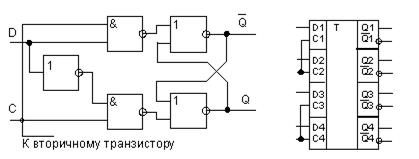

D-триггеры

D–триггеры имеют только один информационный вход. Сигнал на выходе Q в такте n+1 повторяет входной сигнал Dn в предыдущем такте n и сохраняет это состояние до следующего тактирующего импульса, то есть осуществляется задержка на один такт информации, существующей на входе D (Delay).

Qn+1 = Dn

ТМ7

D–триггеры серии ТМ7 со статическим управлением внутренними, объединенными попарно, синхронизирующими входами используются в качестве четырехразрядного регистра хранения информации с попарным тактированием разряда, а также в качестве буферной памяти и элемента задержки.

У ТМ5 отсутствует инверсный выход.

ТМ8 – с динамическим управлением.

T- и TV-триггеры.

T-триггер – счетный триггер, который имеет один информационный вход и меняет свое состояние всякий раз, когда меняет свое значение входной сигнал. В зависимости от того, фронт или срез используется для управления, считается, что триггер имеет прямой или инверсный вход. Единственный вид триггера, состояние которого определяется состоянием в предыдущем такте, а не от входной информации. Выполняет операцию сложения по модулю 2. Легко получается из D- или JK-триггера.

Дата добавления: 2017-01-26; просмотров: 4849;