Ситуации риска в логических схемах

Распространение импульсного сигнала по сети логических элементов происходит с задержкой. Задержка зависит от трассы распространения. Если сигналы а и б распространяются по цепям, имеющим различные задержки, то произойдет смещение сигналов во времени. При поступлении таких сигналов на входы логического элемента на его выходе произойдет изменение длительности сигнала или возникает риск сбоя - кратковременный ложный сигнал на выходе. Различают три основных типа риска: статический, динамический и существенный.

В комбинационных схемах встречаются ситуации статического и динамического риска. В общем случае: при изменении входных сигналов на выходе могут возникать кратковременные изменения - "иголки" из-за того, что на различных путях прохождения сигнала от входа к выходу могут возникать различные временные задержки. Одним из признаков наличия ситуации единичного риска является наличие единиц в смежных ячейках, не покрытых термом согласования при составлении выражений по карте Карно в SP – форме. Ситуация статического риска может быть устранена на стадии проектирования включением дополнительных термов, покрывающих смежные пары ячеек.

Ситуация динамического риска возникает там, где сигнал одной переменной проходит по трем или более различным путям с различными временными задержками. При этом выходной сигнал изменяется минимум три раза, а анализ карты Карно показывает, что статический риск отсутствует. Ситуацию динамического риска можно устранить путём добавления временной задержки после анализа таблицы истинности.

Моделирование комбинационной схемы с учетом временных задержек элементов дает наиболее достоверные результаты. При этом учитываются не только логические значения сигналов, но и очередность поступления этих сигналов на входы логических элементов, что имеет значение при анализе схем на наличие ситуаций риска.

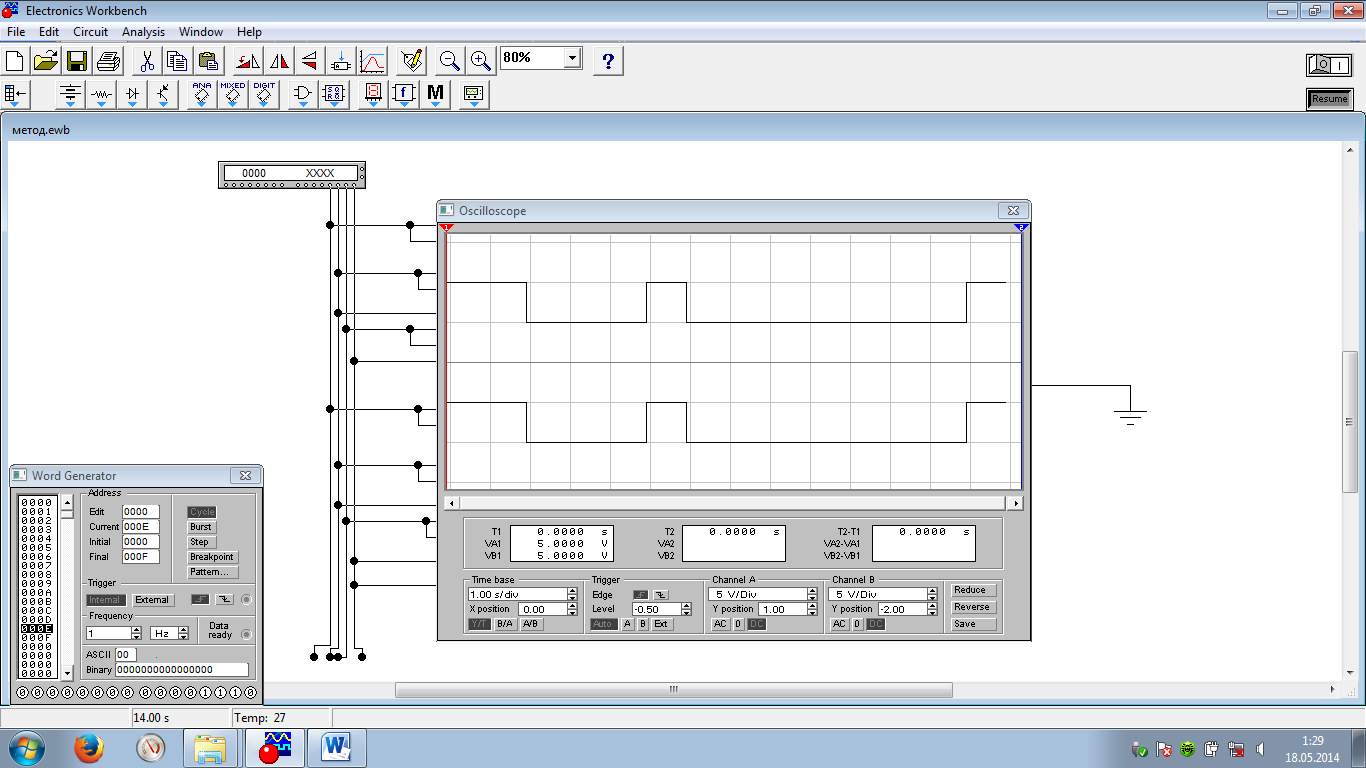

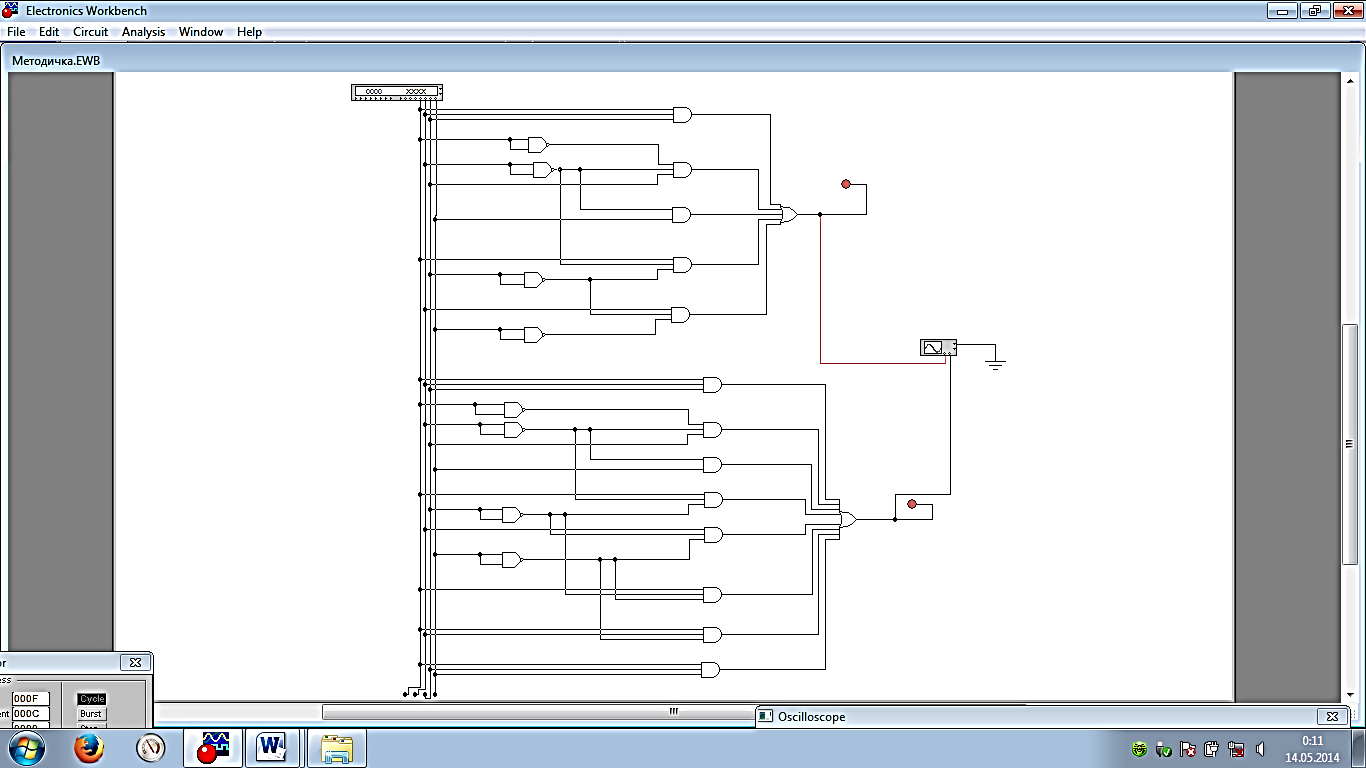

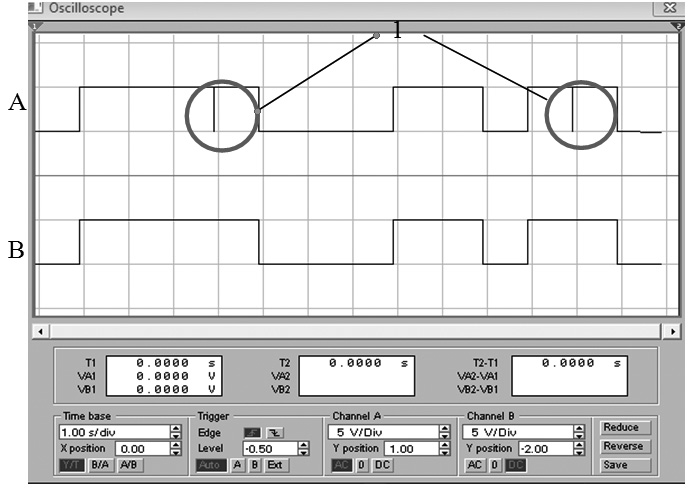

Результатом моделирования логической схемы является временная диаграмма выходного сигнала, которую можно увидеть на экране подключенного к выходу схемы осциллографа с соответствующими настройками. При этом на вход схемы подаются сигналы с соответствующих выходов логического генератора. Наблюдаемые на осциллограмме выходного сигнала минимизированной схемы «иголки» свидетельствуют о наличии ситуаций риска. Они должны отсутствовать на осциллограмме выходного сигнала схемы с дополнительным термом согласования.

Рассмотрим порядок выполнения работы на следующем примере: построить и исследовать логическую схему для функции f = S (0, 1, 5, 13).

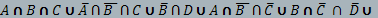

Исходное логическое выражение будет иметь вид:

Fисх=`А Ù`В ∩`С ∩`D  `А∩`В ∩`С∩D

`А∩`В ∩`С∩D  `А∩В ∩`С∩ D

`А∩В ∩`С∩ D  А ∩В ∩`С∩D

А ∩В ∩`С∩D

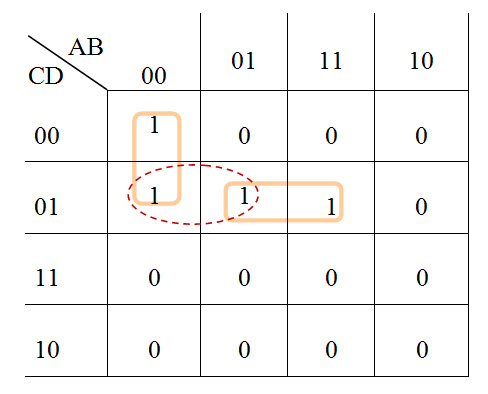

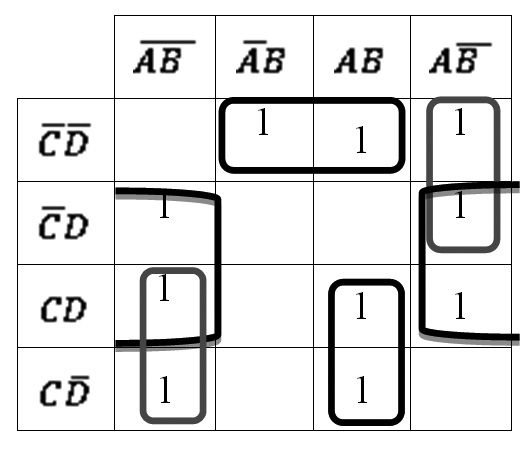

Составим карту Карно для заданной функции (рис. 2.22).

Рис.2.22. Карта Карно

Объединив на карте Карно две пары рядом стоящих единиц, составим логическое выражение для минимизированной схемы, не защищенной от ситуации риска

fmin = `А ∩`В ∩`С  В ∩`С ∩ D, (1)

В ∩`С ∩ D, (1)

и для оптимальной схемы, гарантированной от ситуаций риска

fopt = `А ∩`В ∩`С  В ∩`С ∩ D

В ∩`С ∩ D  `А ∩`С ∩ D , (2)

`А ∩`С ∩ D , (2)

(`А ∩`С ∩ D - является термом согласования для выражения (1)). Очевидно, что оба выражения меньше исходного, содержащего в данном случае 16 элементов.

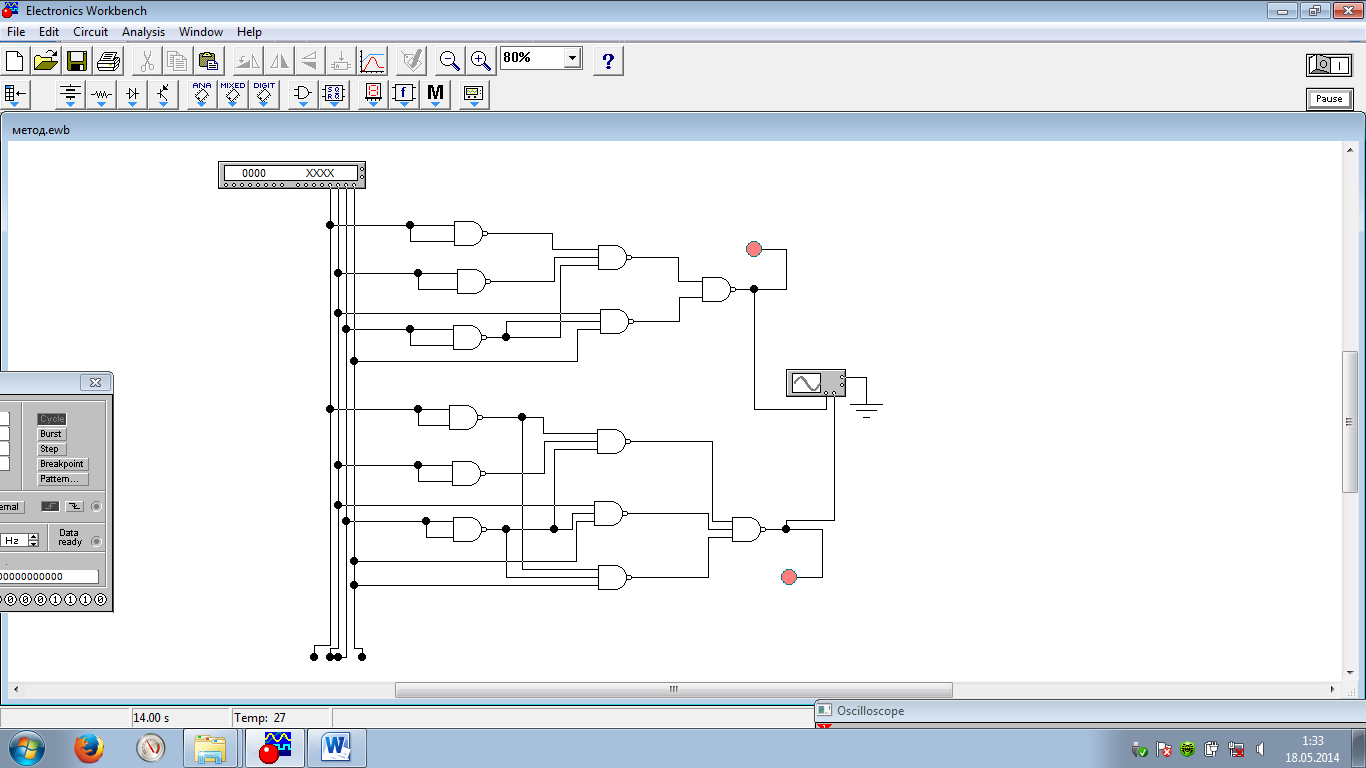

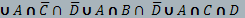

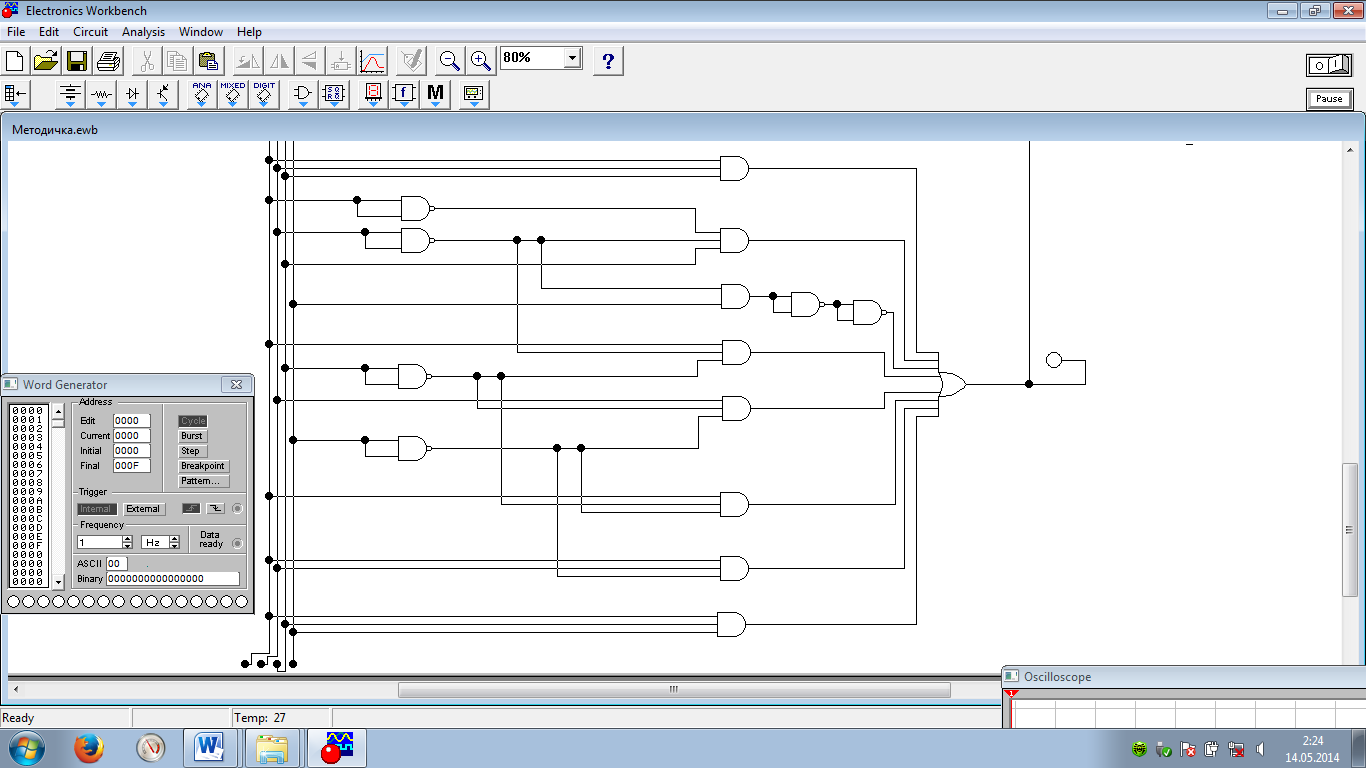

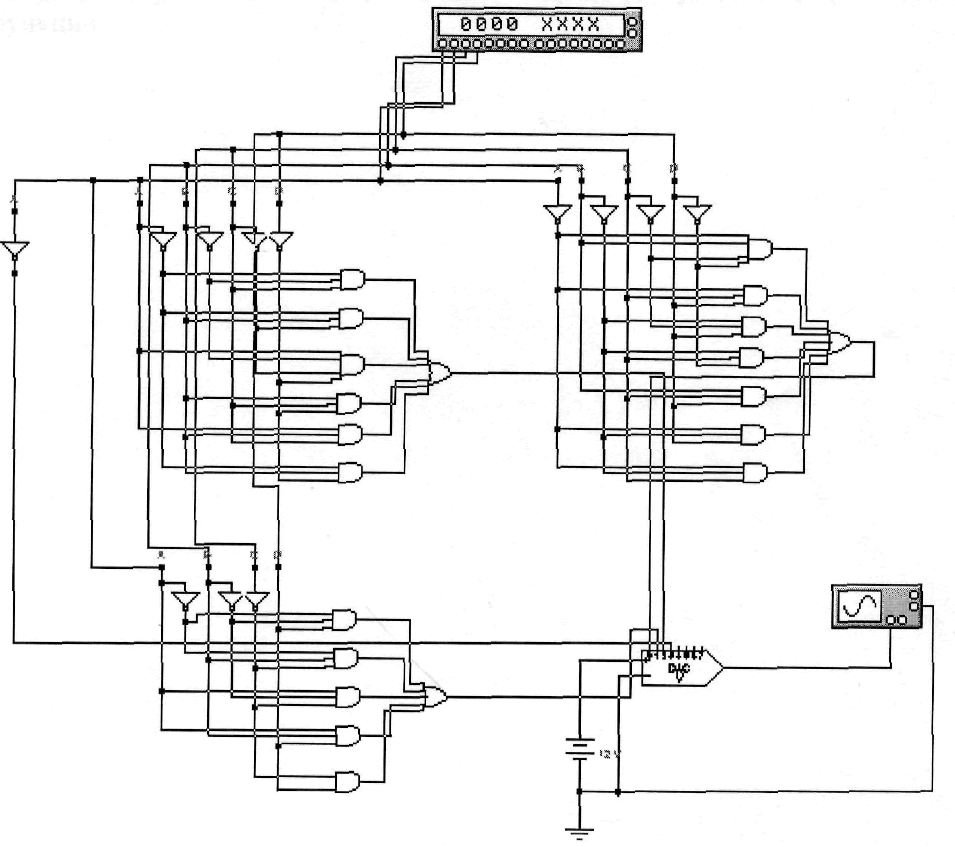

По полученным выражениям строятся машинные модели для двух схем на элементах И-НЕ: одна для минимизированного варианта схемы, не исключающего ситуации статического риска, другая - для варианта, исключающего ситуации статического риска. Входы схем подключаются к генератору слов, а выходы – к двулучевому осциллографу (рис.2.23). После соответствующей настройки генератора и запуска программы получаем временные диаграммы работы схем.

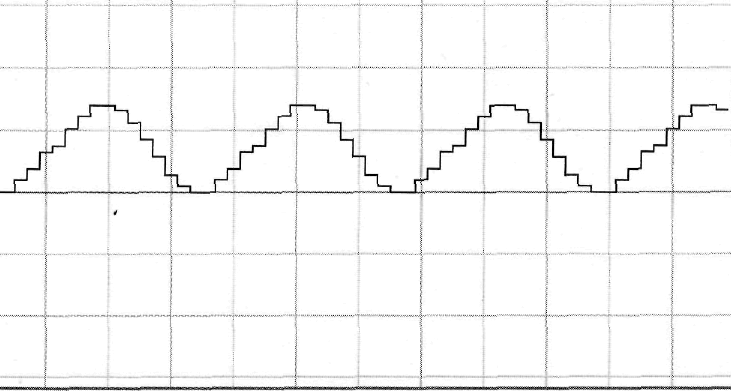

Как видно из осциллограмм, в первом случае наблюдается кратковременный выброс (иголка) выходного сигнала, которая исчезает во втором случае, где в схему добавлен соответствующий терм согласования (рис. 2.24, внизу).

| б) |

| а) |

Рис.2.23. Схемы без исключения (а) и с исключением (б) статического риска.

Рис.2.24. Осциллограмма выходных сигналов

В ряде случаев, в схемах, покрытых дополнительным термом согласования, можно наблюдать кратковременный сигнал в виде «иголки» на выходе. Это свидетельствует о том, что ситуация риска не была полностью устранена.

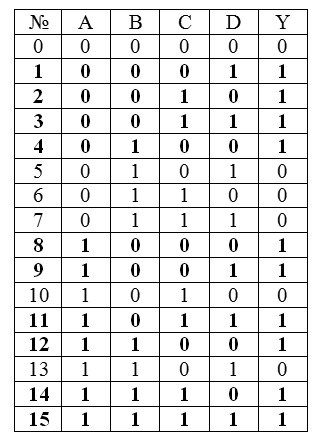

Рассмотрим модель схемы составленной для функции:

Y = ∑ (1,2,3,4,8,9,11,12,14,15)

Составим таблицу истинности для заданного условия (рис. 2.25):

Рис.2.25. Таблица истинности для функции Y = ∑ (1,2,3,4,8,9,11,12,14,15)

Логическое выражение исходной схемы имеет вид:

Y =

Для минимизации схемы составим карту Карно для заданного выражения (рис. 2.26).

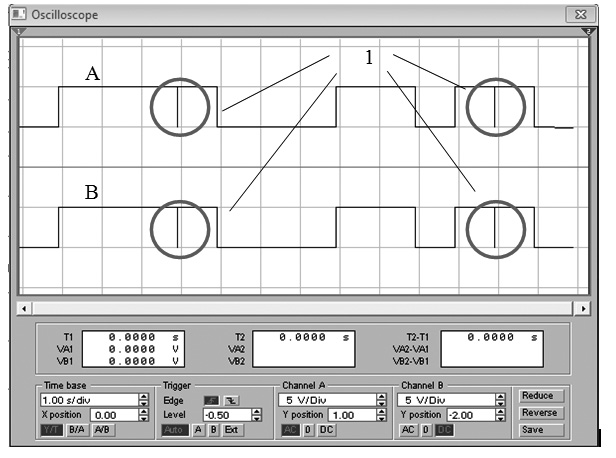

Логическое выражение минимизированной схемы, не защищённой от ситуации риска, имеет вид:

Ymin =

Рис.2.26. Карта Карно для функции Y = ∑ (1,2,3,4,8,9,11,12,14,15)

Логическое выражение схемы, защищённой от ситуации риска с дополнительными термами согласования, имеет вид:

Yopt =

.

.

По полученным выражениям строим модели схем и подсоединяем входы к генератору слов, а выходы подсоединяем к входам двулучевого осциллографа (рис.2.27).

|

|

|

| б) |

| а) |

| А |

Рис.2.27. Схемы без исключения (а) и с исключением (б) статического риска

На экране осциллографа видим выбросы («иголки») 1 при переходе схемы из состояния 3(0011) в состояние 4(0100), и из состояния 11(1011) в состояние 12(1100), т.е. в моменты времени, когда одновременно меняют своё значение три переменных B, С, D (рис.2.28).

| А В |

Как видно из рис.2.27, функция «ИЛИ» объединяет восемь входных сигналов, три из которых меняют своё значение при указанных переходах:

1) В`С`D; 2) `А`В С; 3)`ВD

Сигнал 1) меняется с 0→1. Сигналы 2) и 3) с 1→0. Очевидно, что единичный риск возникает при задержке появления сигнала 1) по отношению к моменту исчезновения сигналов 2) и 3). В короткий промежуток времени, равный времени отставания, на всех входах элемента «ИЛИ» будут нули, что приведёт к кратковременному появлению «0» на выходе, наблюдаемому на осциллограмме в виде «иголок» (рис.2.23). Дополнительная задержка сигналов 2) или 3) должна исключить изменение единичного сигнала в процессе переключения.

Добавив в цепь сигнала 3) два инвертора на основе двухвходовых элементов «И-НЕ» (рис.2.29), получили осциллограмму без «иголок» (рис.2.30). При моделировании или отладке схем, в результате анализа процесса переключения в момент образования наблюдаемых кратковременных ложных сигналов на выходе («иголок»), появляется возможность устранить как статические, так и динамические ситуации риска, неустранимые термом согласования, путём включения дополнительных элементов для обеспечения задержки в соответствующие цепи.

|

|

|

Рис. 2.29. Схема исключения динамического риска

путём добавления двух инверторов в цепь сигнала

Рис. 2.30. Осциллограммы, до (А) и после (В)

включения в схему двух инверторов

Таким образом, можно получить оптимальную структуру схемы, обеспечивающую минимум аппаратных средств при максимуме надежности. Оба критерия являются весьма важными, и обеспечение их оптимального сочетания на стадии проектирования является весьма эффективным средством достижения конкурентоспособности разрабатываемых схем. Повышение надёжности схемы на стадии проектирования путем компьютерного моделирования позволяет значительно снизить затраты на отладку схемы при её реализации.

3 МОДЕЛИРОВАНИЕ ЦАП и АЦП

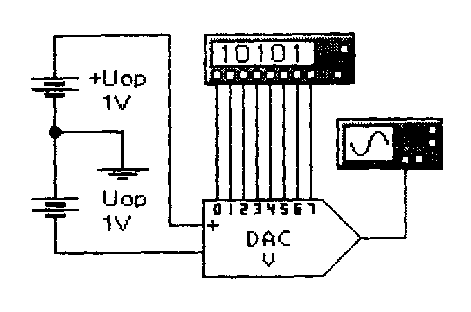

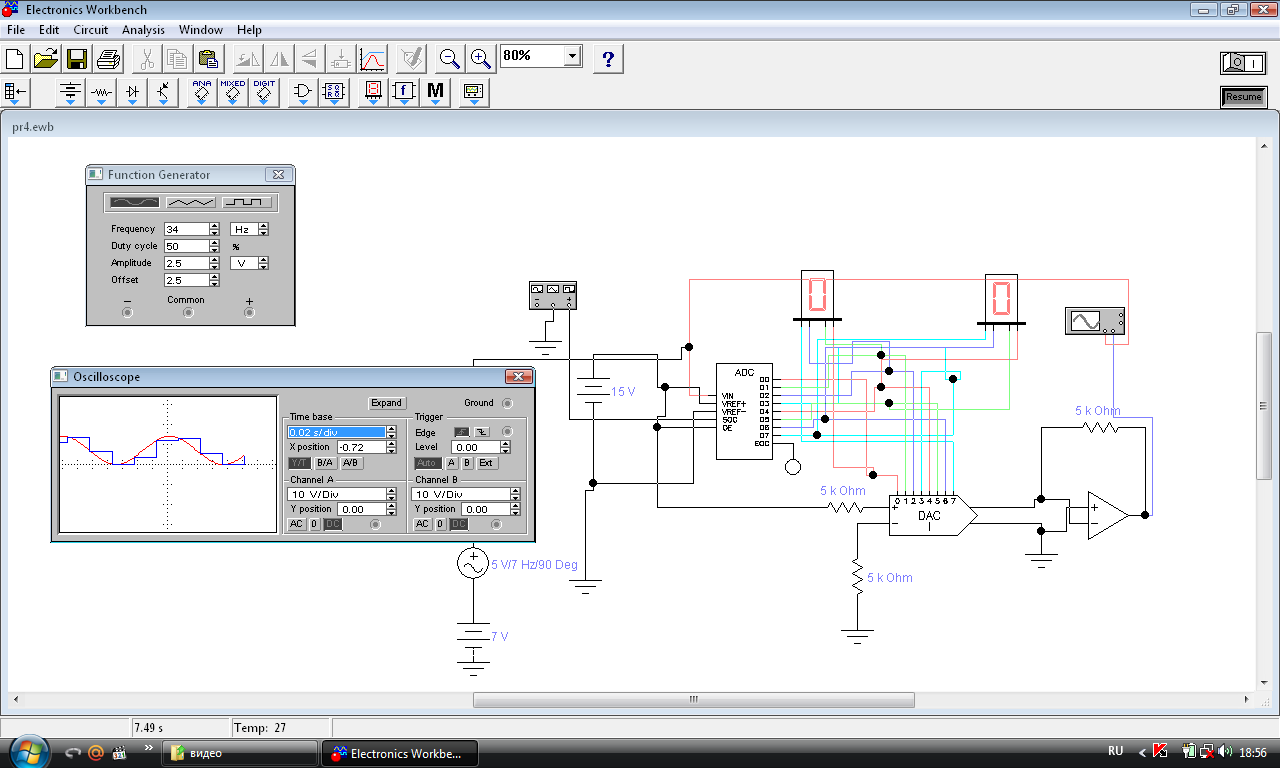

В библиотеке программы EWB 4.1 преобразователи представлены 8-разрядными ЦАП и АЦП. Схема включения библиотечного ЦАП приведена на рис.3.1. Она содержит собственно ЦАП (DAC V), два источника опорного напряжения +Uop и -Uop, генератор слов и осциллограф.

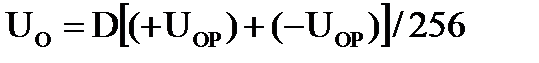

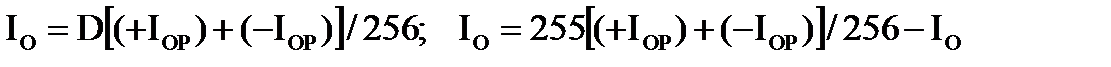

Выходное напряжение ЦАП определяется выражением:

,

,

где D - десятичный эквивалент входного двоичного кода (например, при входном 00000011D=3).

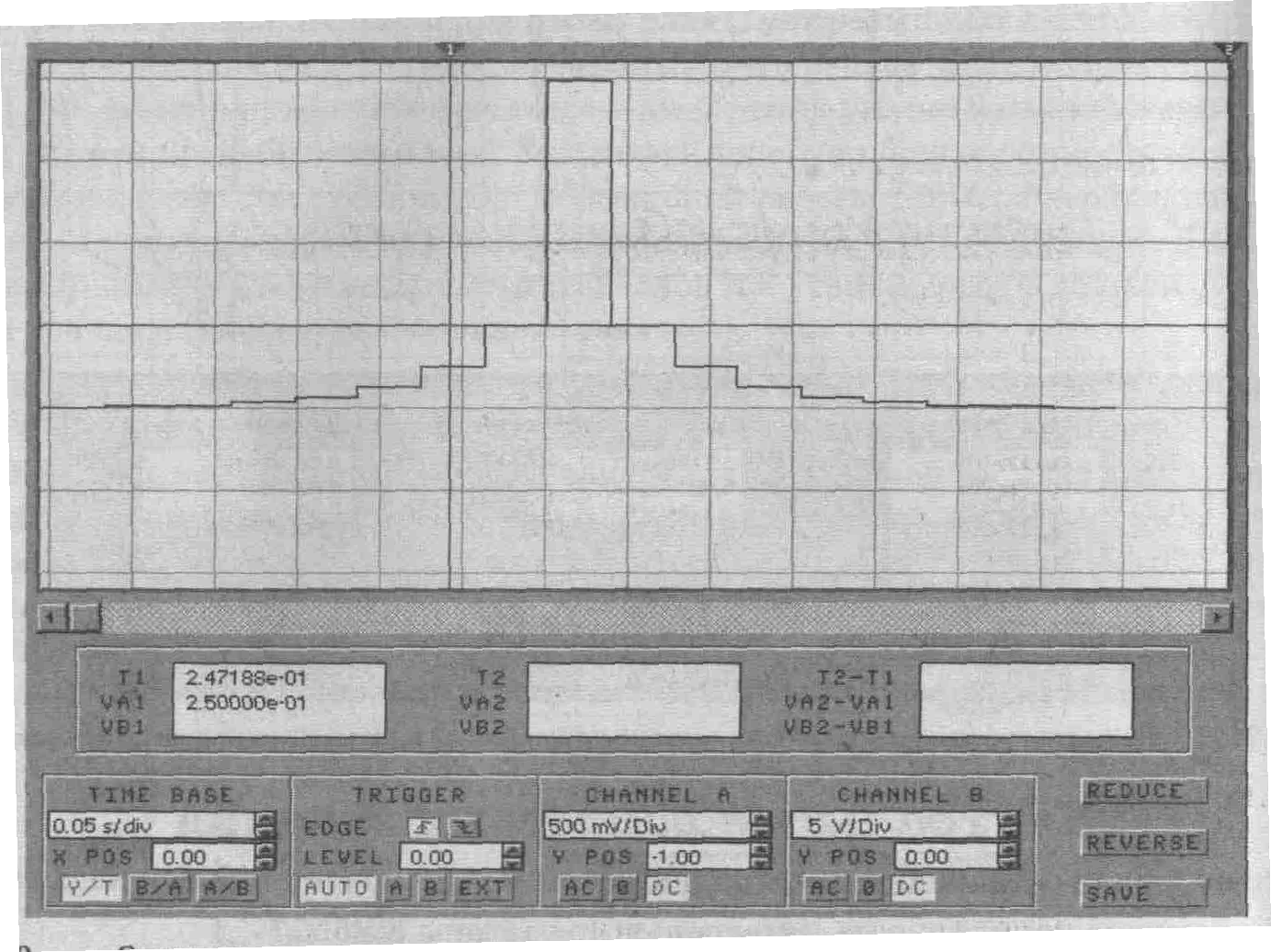

Задавая соответствующие кодовые комбинации на выходе генератора слов, можно с помощью осциллографа измерить максимальное выходное напряжение ЦАП, а также минимальное, соответствующее младшему разряду и определяющему разрешающую способность ЦАП. Нумерация разрядов показана на графическом значке ЦАП, осциллограмма - на рис.3.2.

Рис. 3.1. Схема включения библиотечного ЦАП

Для ЦАП с опорными источниками тока +Iор, -Iop ток прямого и инверсного выхода определяется соответственно:

.

.

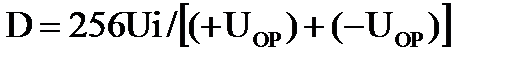

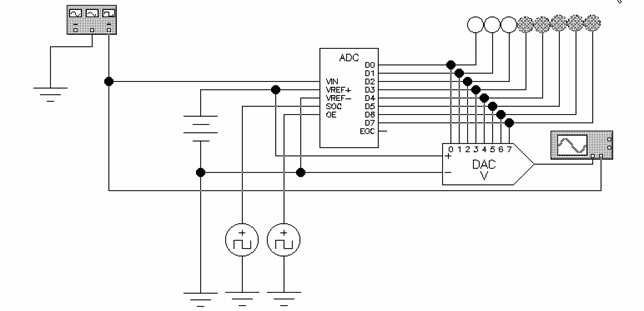

Схема включения библиотечного АЦП показана на рис.3.1. В ее состав входят собственно АЦП (ADC), источники опорного напряжения, генератор слова для синхронизации и управления выходом АЦП, функциональный генератор в качестве источника входного сигнала Ui, логический анализатор, преобразователь двоичный код-код ASCII и осциллограф.

Назначение выводов АЦП: VIN - подключение источника преобразуемого сигнала; VREF+, VREF- - подключение источников опорного напряжения; SOС - вход синхронизации; ОЕ - разрешение на выдачу выходной двоичной комбинации на выходыDO...D7; ЕОС - сигнал готовности данных (например, при выдаче данных на ЭВМ).

Рис. 3.2. Осциллограмма выходного напряжения ЦАП

Для заданного значения входного напряжения Ui, зафиксированного, например, с помощью устройства выборки и хранения, десятичный эквивалент двоичного кода на выходе АЦП определяется выражением:

.

.

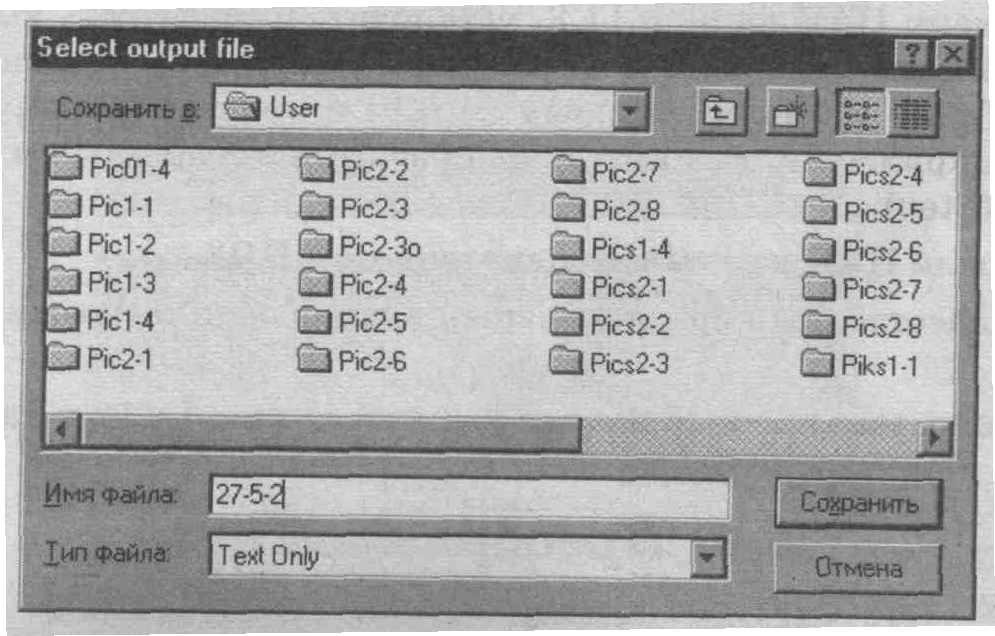

Устройство ASCII позволяет записать данные в текстовый файл. После двойного щелчка по его изображению вызывается диалоговое окно, показанное на рис.3.4, где указывается имя файла. По умолчанию в меню предлагается имя схемного файла, имеющее расширение, txt.

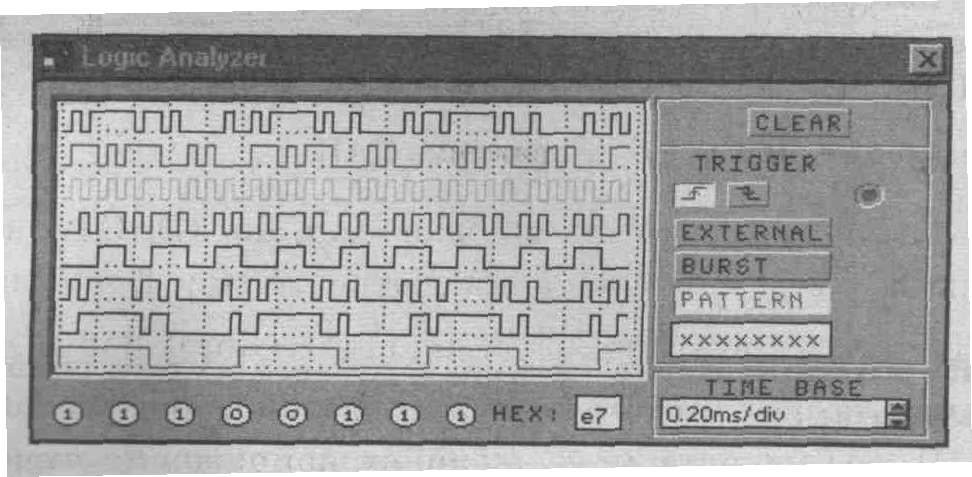

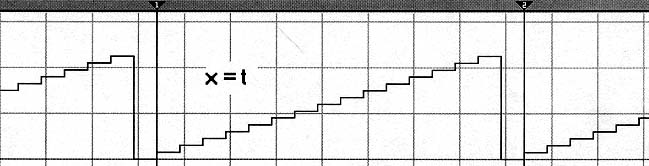

Полученные данные с АЦП можно анализировать с помощью логического анализатора и осциллографа. Данные на экране логического анализатора при преобразовании синусоидального сигнала с напряжением 1 В и частотой 1 кГц показана на рис.3.5.

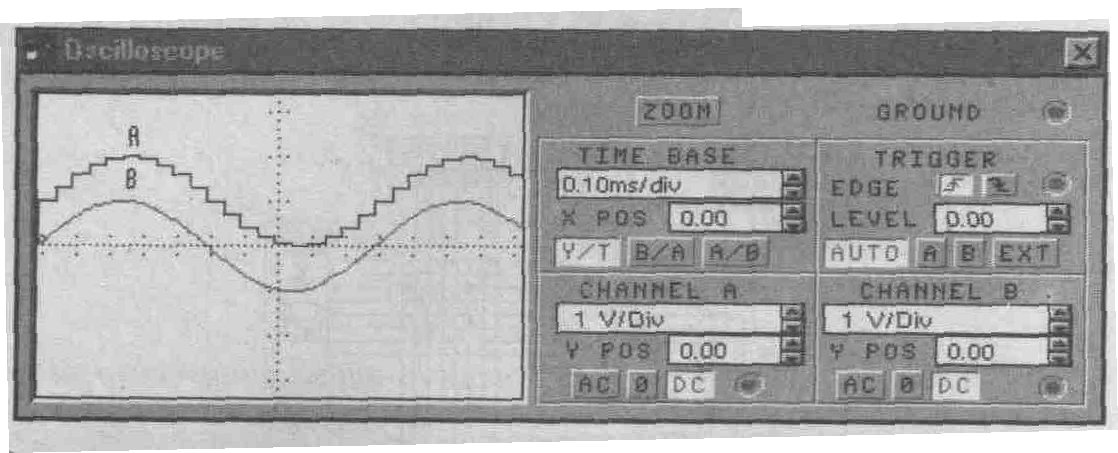

Начальный участок данных на рис.3.5 после их преобразования в аналоговый сигнал с помощью ЦАП показан в виде осциллограммы на рис. 3.6.

Рис. 3.3. Схема включения библиотечного АЦП

Рис. 3.4. Окно для записи данных в текстовый файл

Рис. 3.5. Осциллограммы выходного сигнала АЦП на экране

логического анализатора

Рис. 3.6. Осциллограммы выходного сигнала ЦАП (А) и входного АЦП (В)

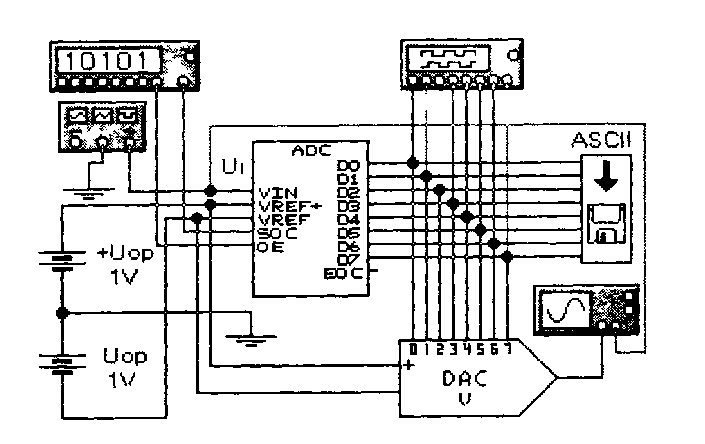

Используя библиотечные АЦП (ADC) и ЦАП (DAC-I) получить преобразование синусоидального аналогового сигнала в цифровой и обратно, убедившись в том, что система восстановила исходный сигнал. Подсчитать погрешность преобразования сигнала. Для модели преобразователя понадобятся:

8-разрядный АЦП

8-разрядный ЦАП с внешним опорным источником тока и парафазным выходом.

Семисегментный индикатор с дешифратором.

Операционный усилитель.

Схема включения библиотечных АЦП и ЦАП показана на рисунке 3.7. В ее состав входят источник опорного напряжения, функциональный генератор для синхронизации и управления выходом АЦП, осциллограф и индикаторы. Назначение выводов АЦП: SOC – вход синхронизации, OE – Разрешение на выдачу выходной двоичной комбинации на выходы D0…D7, VIN – подключение источника преобразуемого сигнала.

Рис. 3.7. Схема включения библиотечных АЦП и ЦАП

Подавая на вход VIN АЦП сигнал с функционального генератора, можно менять вид преобразуемого сигнала. Варианты подаваемых на вход АЦП сигналов представлены в таблице 3.1

Таблица 3.1

| № | Значение опорного/входного напряжения, В | Частота входного синусоидального сигнала, Гц |

| 15/7 | ||

| 15/6 | ||

| 15/5 | ||

| 15/8 | ||

| 15/9 | ||

| 15/10 | ||

| 15/4 | ||

| 15/3 | ||

| 15/2 | ||

| 15/7 | ||

| 15/8 | ||

| 15/9 | ||

| 15/6 |

Пример схемы моделирования представлен на рисунке 3.8.

Рис. 3.8. Схема моделирования сигналов различного вида

После моделирования схемы в соответствии с вариантом, можно распечатать результат с развернутыми показаниями приборов по п.1 и п.2, и сделать вывод по оптимальным значениям частот.

4 МОДЕЛИРОВАНИЕ ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ

АНАЛОГОВОГО СИГНАЛА

В библиотеке программы EWB 5.0 преобразователи представлены 16-разрядными ЦАП и АЦП. Это позволяет проводить синтез, моделирование цифрового преобразователя аналогового сигнала и построение графика функции в соответствии с заданием.

Если выходы генератора слов, запрограммированного на выдачу последовательности двоичных кодов чисел от 0 до 15, соединить с соответствующими входами ЦАП, то на экране осциллографа, подключенного к выходу ЦАП, видим сигнал в соответствии с рис.4.1.

Рис.4.1. Осциллограмма сигнала у=х

Для преобразования линейной функции у=х в заданную функцию необходимо синтезировать устройство в виде соответствующей логической схемы. Рассмотрим для примера синтез преобразователя линейной функции в синусоидальную у=sin(x).

Формализуем задание в виде таблицы истинности.

Таблица 4.1

Таблица истинности

| X | ХЗ | Х2 | XI | Х0 | Y | YЗ | Y2 | Y1 | Y0 | |

| I5 |

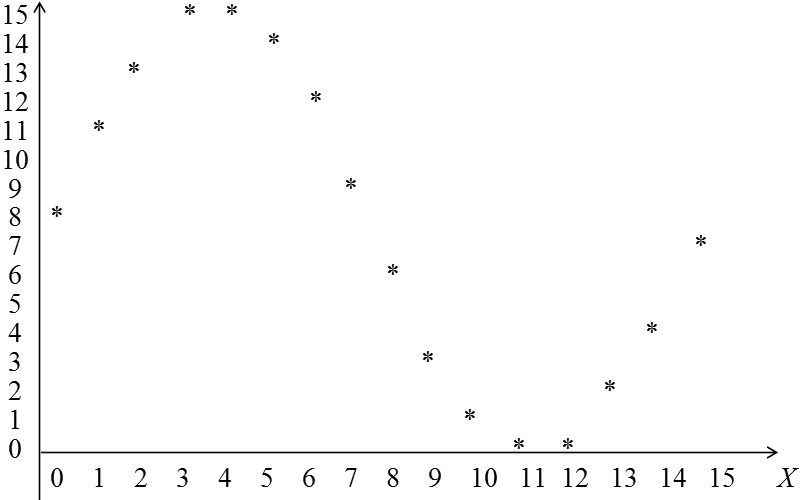

В левой части таблицы приведены двоичные эквиваленты последовательности десятичных чисел от 0 до 15, что соответствует линейной зависимости у=х, В правой части таблицы приведены вычисленные десятичные значения соответствующих точек заданной функции и их двоичные эквиваленты. На рис.4.2 приведен график заданной функции, построенный по расчетным значениям в соответствии с таблицей.

Рис.4.2. Расчетный график функции у=7.5+7.5sin(0.42x)

По данным таблицы истинности исходной функции строятся матрицы Карно для выходных функций Y0,Y1,Y2,Y3.

Матрица Карно для Y0

| X3X2 Х1Х0 | ||||

Y0=`X3* X2*`X1*`X0+`X2*`X1* X0 +`X3*`X2* X0 + X2*X1*X0 +`X2* X1*`X0+`X3*`X2*X1;

Матрица Карно для Y1

| X3X2 Х1Х0 | ||||

Y1=`X3*`X2*X0 +`X3*X2*`X1 + X3*X2*X0 + X3*`X2*`X1 +`X1*X0;

Матрица Карно для Y2

| X3X2 Х1Х0 | ||||

Y2=X3*`X2*`X1*`X0 +`X3*X2*`X1 +`X3*`X2* X1 +`X3*X1*`X0 + X3* X2*X1+X2*X1* `X0;

Матрица Карно для Y3

| X3X2 Х1Х0 | ||||

Y3=`X3;

Для синтеза схем можно воспользоваться логическим генератором. Вариант синтезированной схемы для реализации полученных функций на логических элементах представлен на рис.4.3. Использование ЦАП, на соответствующие входы которого подаются сигналы Y0,Y1,Y2,Y3 , позволяет увидеть сигнал на экране осциллографа (рис.4.4).

Рис.4.3. Модель логической схемы преобразователя

Рис.4.4. Осциллограмма выходного сигнала преобразователя

5 Преобразователь на интегральном таймере

Интегральные таймеры являются наиболее яркими представителями устройств смешанного типа, из них наиболее популярным является таймер NE555 (отечественный аналог КР1006ВИ1). Учитывая его широкое распространение в различной аппаратуре промышленного и бытового назначения, рассмотрим кратко характеристики и особенности применения NE555 [2].

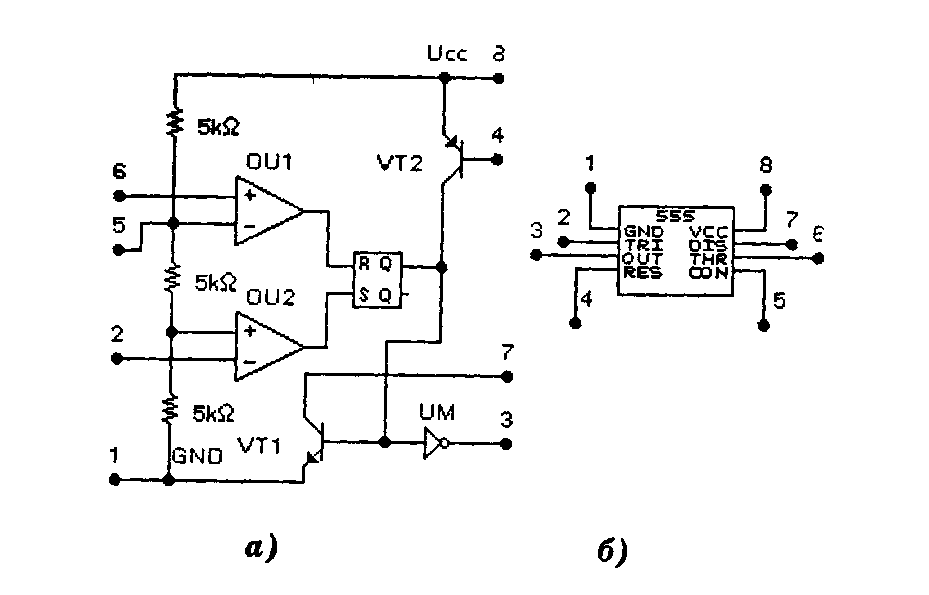

Функциональная схема таймера и его графическое обозначение в программе EWB показаны на рис.5.1. Таймер содержит два компаратора на OU1 и OU2, RS-триггер, инвертирующий усилитель мощности UM, транзисторы VT1, VT2 для цепи разряда и принудительного сброса соответственно. Внутренний резистивный делитель задает пороговые напряжения, равные 2Ucc/3 для OU1 и Ucc/3 для OU2.

Напряжение питания таймера Ucc равно 5...16,5 В, ток нагрузки (вывод 7) - 200 мА, что позволяет управлять непосредственно лампочками или электромагнитными реле. Выходное сопротивление около 10 Ом как для низкого, так и для вые кого уровней выходного напряжения. Запуск таймера осуществляется подачей на вывод 2 напряжения менее Ucc/3 (эту цепь обычно называют триггерным входом. При высоком напряжении на выводе 2 состоянием выхода таймера можно управлять с помощью компаратора OU1 по выводу 6, называемому обычно пороговым входом. Входной ток, втекающий в OU1 (вывод 6) и вытекающий из OU2 (вывод 2), не превышает 0,5 мкА. Для сброса таймера, т.е. установки на его выходе низкого напряжения независимо от напряжения на выводах 2 и 6 используется вывод 4. Если напряжение на этом выводе меньше 0,4 В, напряжение на выходе равно 0,1 - 0,2 В, а при напряжении больше 1 В цепь сброса выключена и не влияет на работу таймера. Кроме низкоомного выхода (вывод 3) таймер имеет и вспомогательный высокоомный выход (вывод 7, коллектор транзистора VT1). Этот вывод обычно используется для организации обратной связи с выхода на входы (выводы 2 и 6) таймера. Допустимое изменение напряжения на выводах 2, 4, 6 и 7 находится в пределах 0... 16,5 В. В таймере имеется доступ через вывод 5 к входам внутренних компараторов, на которые поданы пороговые напряжения. Этот вывод от резистивного делителя позволяет изменять пороговые напряжения компараторов при постоянном напряжении питания и тем самым дополнительно управлять работой таймера. Чтобы избежать влияния внешних помех и пульсации напряжения питания на точность работы таймера, рекомендуется шунтировать вывод 5 конденсатором емкостью 0,01 мкФ.

Рис. 5.1. Функциональная схема таймера NE555 (а)

и его графическое изображение в программе EWB (б)

В режиме прямой трансляции сигнала со входа на выход таймер работает в диапазоне частот до 10 МГц. Однако приводимое в справочных данных значение погрешности формирования временного интервала, равное 0,5%, измеряется обычно при формировании импульсов длительностью более 10 мкс. Время нарастания выходного напряжения таймера не превышает 100 нс.

Временные параметры таймера слабо зависят от изменений Ucc и температуры и полностью определяются схемотехникой внутренних компараторов и качества биполярной технологии их изготовления. В таймерах, изготовленных по КМОП - технологии, отличающейся худшим согласованием параметров парных транзисторов, зависимость характеристик от Ucc и температуры значительно выше, чем у таймеров, изготовленных по биполярной технологии.

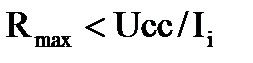

Чтобы параметры времязадающей RC-цепи не влияли на точность формирования временных интервалов, необходимо ограничить диапазон изменения сопротивления R и емкости С. Максимальное сопротивление R определяется входным током Ii компараторов. Для формирования устойчивых временных интервалов достаточно выбрать максимальное сопротивление R из условия  ; при Ucc= 10 В и Ii= 5 мкА, Rmax= 20 МОм. При включении таймера по схеме мультивибратора, когда выводы 2 и 6 объединены, таймер сохраняет работоспособность при R>Rmax, при этом рекомендуется использовать времязадающие резисторы с сопротивлением R> 10 МОм.

; при Ucc= 10 В и Ii= 5 мкА, Rmax= 20 МОм. При включении таймера по схеме мультивибратора, когда выводы 2 и 6 объединены, таймер сохраняет работоспособность при R>Rmax, при этом рекомендуется использовать времязадающие резисторы с сопротивлением R> 10 МОм.

Минимальное сопротивление R определяется максимально допустимым током, протекающим через транзистор VT1 таймера при его насыщении. Хотя допустимый выходной ток устанавливают обычно на уровне 100 мА, не рекомендуется использовать малые сопротивления R в сочетании с большими емкостями С. Объясняется это тем, что при разряде конденсатора большой емкости транзистор VT1 переходит в режим насыщения через конечное время, в течение которого он находится в активном режиме при напряжении коллектор-эмиттер UКЭ=Ucc/2, и при Rmin он может выйти из строя из-за большой рассеиваемой на нем мощности. Поэтому при формировании малых временных интервалов рекомендуется ограничиться значением Rmin=l кОм и выбрать исходя из этого емкость С. Если же таймер применяется в схеме, где С<100 пФ, то сопротивление R может быть уменьшено до 150 Ом.

Минимальная емкость времязадающего конденсатора С должна быть значительно больше изменений емкости выводов 2, 6 и 7, зависящей от напряжения на них. Поскольку эти изменения при перезарядке С не превышают нескольких пикофарад, при формировании точных временных интервалов целесообразно выбирать С<100 пФ. Можно применять конденсаторы С сколь угодно большой емкости, если их ток утечки пренебрежимо мал. Фактически же, чем больше емкость конденсатора, тем больше его ток утечки. Для нормальной работы таймера необходимо, чтобы ток утечки конденсатора С не превышал зарядный ток через резистор R. Для формирования точных (<1%) временных интервалов ток утечки через С должен быть б< чем на два порядка меньше зарядного тока.

Выходной инвертирующий усилитель таймера UM работает в режиме АВ, вследствие чего на переходной характеристике возникает "полка" длительностью 10... 20 нс при напряжении 1,5 В. Если таймер нагружен на быстродействующие ТТЛ - схемы (например, серий 130 или 533), то наличие такой "полки" недопустимо, так как она может вызвать ложное срабатывание логического элемента. Для устранения этого недостатка необходимо выход таймера зашунтировать конденсатором емкостью около 100 пФ.

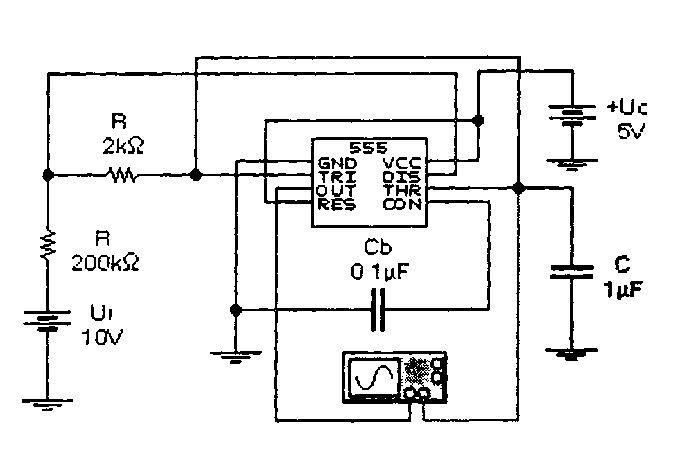

Преобразователи на интегральных таймерах отличаются весьма широким частотным диапазоном (в пределах 2...4 декад). Так, при включении таймера по схеме самовозбуждающегося мультивибратора можно получить линейный преобразователь напряжения в частоту, изменяющуюся от 10 Гц до 10 кГц, причем этот диапазон может быть легко сдвинут в любую сторону заменой одного из элементов схемы. К сожалению, модель таймера NE555 в программе EWB далека от совершенства и не позволяет это реализовать. Предварительное исследование преобразователя, схема которого приведена на рис.4.2, показало, что преобразуемое напряжение должно быть больше напряжения питания Ucc. Кроме того, схема не работает при отсутствии дополнительного сопротивления в цепи разряда интегрирующего конденсатора (транзистор VT1), поэтому сопротивление его заряда составлено из сопротивлений двух резисторов - R и R¢.

Рис. 5.2. Преобразователь напряжение-частота на таймере NE555

В схеме на рис.5.2 использована пассивная интегрирующая RC-цепь, поскольку преследовалась только цель проверки ее работоспособности. Для повышения линейности преобразователя на входе практического аналога схемы на рис. 5.2 используется преобразователь напряжение-ток (стабилизатор тока).

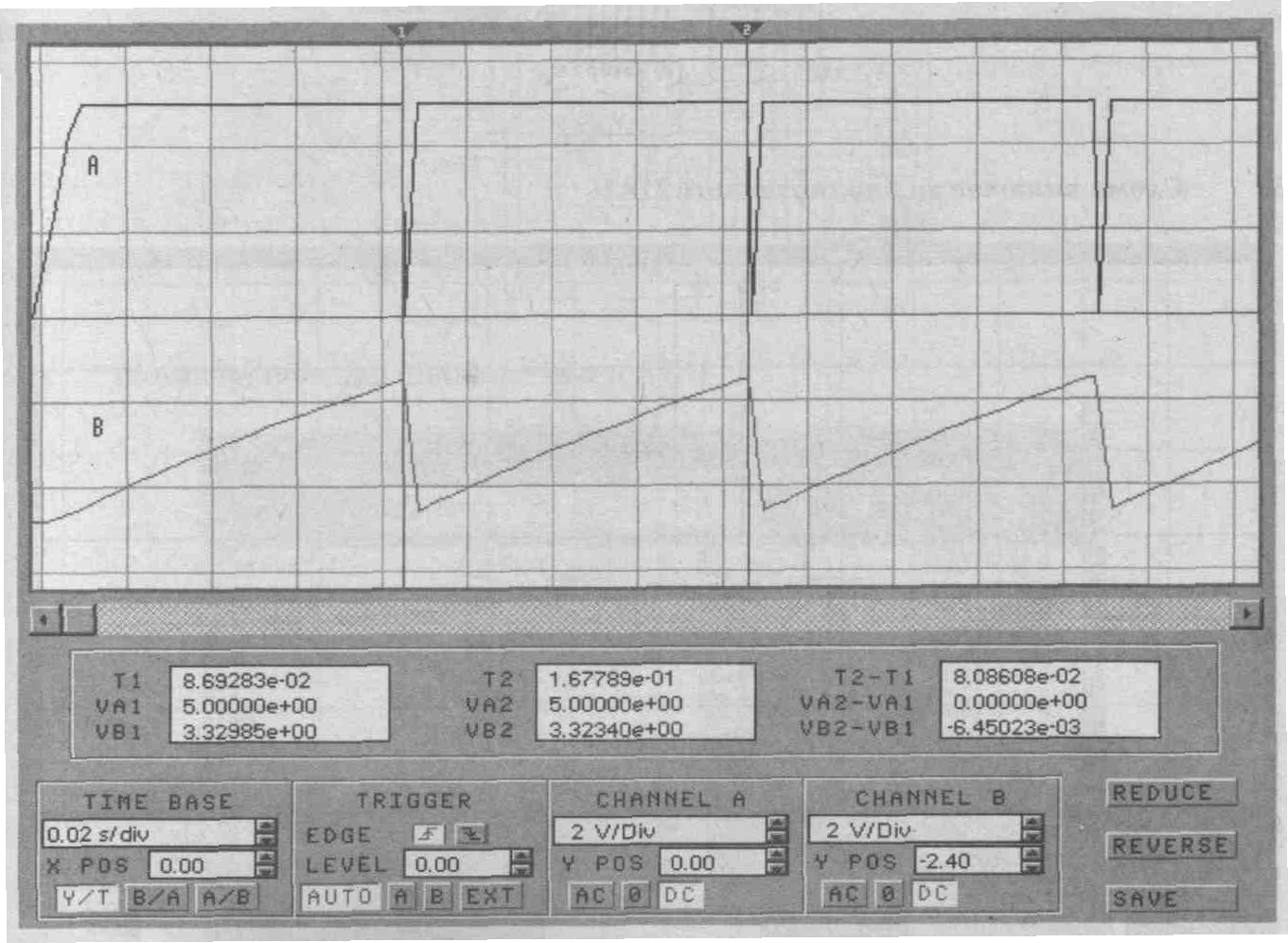

Осциллограммы сигналов на выходе OUT микросхемы и конденсаторе С показаны на рис. 5.3.

Рис. 5.3 Осциллограммы сигналов на выходе таймера (А)

и интегрирующем конденсаторе (В)

Контрольные вопросы и задания

1. Что из себя представляют интегральные таймеры и почему они так называются?

2. Чем вызвана популярность интегрального таймера NE555?

3. Проверьте работоспособность схемы преобразователя на рис.2 при Ui = 4...40 В с оценкой линейности преобразования в этом диапазоне.

Дата добавления: 2021-01-26; просмотров: 633;