Мал. 7.2 Основні системні регістри мікропроцесорів і80x86.

Керуючий регістр CR0 містить цілий ряд флагівв, що визначають режими роботи мікропроцесора. Самий молодший біт (РЕ, protect enable) цього регістра визначає режим роботи процесора. При РЕ=0 процесор функціонує в реальному режимі роботи, а при одиничному значенні мікропроцесор переключається в захищений режим. Самий старший біт регістра CR0 (біт PG, paging) визначає, включений (PG=1) чи немає (PG=0) режим сторінкового перетворення адрес.

Регістр CR2 призначений для розміщення в ньому адреси підпрограми обробки сторінкового виключення, тобто у випадку використання сторінкового механізму відображення пам'яті звертання до відсутньої сторінки буде викликати перехід на відповідну підпрограму диспетчера пам'яті, і для визначення цієї підпрограми буде задіяний регістр CR2. Регістр CR3 містить номер фізичної сторінки, у якій розташовується таблиця каталогів таблиць сторінок поточної задачі. Очевидно, що, приписавши до цього номера нулі, ми потрапимо на початок цієї сторінки.

3. Підтримка сегментного способу організації віртуальної пам'яті.

Як ми вже знаємо, для організації ефективної і надійної роботи обчислювальної системи в мультипрограмному режимі необхідно мати відповідні апаратні механізми, що підтримують незалежність адресних просторів кожної задачі й у той же час, що дозволяють організувати обмін даними і поділ коду. Для цього бажано виконання наступних двох вимог:

· щоб у кожного обчислювального процесу міг бути свй власний (особистий, локальний) адресний простір, що ніяк не може перетинатися з адресними просторами інших задач;

· щоб існував загальний (розподілений) адресний простір.

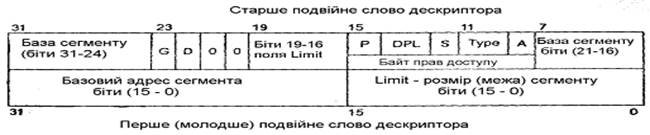

Тому в мікропроцесорах і80x86 реалізований сегментний спосіб організації розподілу пам'яті. Крім цього, в цих мікропроцесорах може бути задіяна і сторінкова трансляція. Оскільки для кожного сегмента потрібний дескриптор, пристрій керування пам'яттю підтримує відповідну інформаційну структуру. Формат дескриптора сегмента приведений на мал. 3.3. Поля дескриптора (базова адреса, поле межі) розміщені в дескрипторі не безупинно, а в розбивку, по-перше, через те, що розробники постаралися мінімізувати кількість перехресних з'єднань в напівпровідниковій структурі мікропроцесора, а по-друге – унаслідок необхідності забезпечити повну сумісність мікропроцесорів (попередній мікропроцесор і80286 працював з 16-бітовим кодом і теж підтримував сегментний механізм реалізації віртуальної пам'яті). Необхідно помітити, що формат дескриптора сегмента, зображений на мал. 3.3, справедливий тільки для випадку перебування відповідного сегмента в оперативній пам'яті. Якщо ж біт присутності в полі прав доступу рівний нулю(сегмент відсутній в памяті), то всі біти за виключенням поля прав доступу, вважаються невизначеними і можуть використовуватися системними програмістами (для вказівки адреси сегмента в зовнішній пам'яті) довільним чином.

Дата добавления: 2016-07-27; просмотров: 2002;