Мал. 7.4. Селектор сегменту.

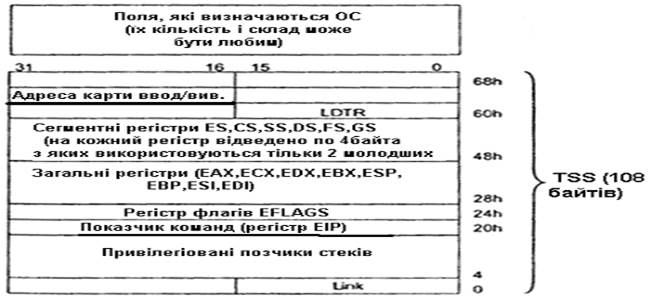

Для маніпулювання задачами ОС має інформаційну структуру, що ми уже визначили як дескриптор задачі. Мікропроцесор підтримує роботу з найбільш важливою частиною дескриптора задачі, що найменше залежить від операційної системи. Ця інваріантна частина дескриптора, з яким і працює мікропроцесор, названа сегментом стану задачі (task state segment, TSS). Перелік полів TSS зображений на мал. 3.5. Видно, що в основному цей сегмент містить контекст задачі. Процесор одержує доступ до цієї структури за допомогою регістра задачі (task register, TR).

Регістр TR містить індекс (селектор) елемента в GDT. Цей елемент являє собою дескриптор сегмента TSS. Дескриптор заноситься в тіньову частину регістра (див. мал. 3.2). До розгляду TSS ми ще повернемося, а зараз помітимо, що в одному з полів TSS міститься покажчик (селектор) на локальну таблицю дескрипторів даної задачі. При переході процесора з однієї задачі на іншу вміст поля LDTR заноситься мікропроцесором в однойменний регістр. Ініціалізувати регістр TR можна і явно.

Отже, регістр LDTR містить селектор, що вказує на один з дескрипторів глобальної таблиці GDT. Цей дескриптор заноситься мікропроцесором у тіньову частину регістра LDTR і описує таблицю LDT для поточної задачі. Тепер, коли в нас визначені як глобальна, так і локальна таблиця дескрипторів, можна розглянути процес визначення лінійної адреси. Для прикладу розглянемо процес одержання адреси команди. Адреси операндів визначаються за аналогією, але задіяні будуть інші регістри.

Мікропроцесор аналізує біт TI селектора коду й у залежності від його значення, витягає з таблиці GDT чи LDT дескриптор сегмента коду з номером (індексом), що рівний полю index (біти 3-15 селектора, див. мал. З.4). Цей дескриптор заноситься в тіньову (сховану) частину регістра CS. Далі мікропроцесор порівнює значення регістра EIP (extended instruction pointer — покажчик інструкції команди) з полем розміру сегмента, що міститься у взятому дескрипторі, і якщо зсув відносно початку сегмента не перевищує розміру межі, то значення EIP додається до значення поля початку сегмента і ми одержуємо шукану лінійну адресу команди. Лінійна адреса - це одна з форм віртуальної адреси. Вихідна двійкова віртуальна адреса, що обчислюється відповідно до використовуваної адресації, перетвориться в лінійну. В свою чергу, лінійна адреса буде дорівнювати або фізичному (якщо сторінкове перетворення відключене), або за допомогою сторінкової трансляції перетвориться у фізичну адресу. Якщо ж зсув з регістра EIP перевищує розмір сегмента коду, то ця аварійна ситуація викликає переривання і керування повинне передаватися супервізору ОС.

Дата добавления: 2016-07-27; просмотров: 1734;