Синхронные D и T-триггеры. Устройство, принцип действия

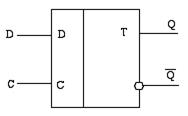

Синхронный D-триггер предназначен для одноступенчатого запоминания информации. На рис.10.14 показаны условное обозначение и таблица истинности

D - триггера. Триггер имеет два входа: информационный D и синхронизирующий C, а также два выхода: прямой Q и инверсный  .

.

Согласно таблице истинности, при подаче на синхронизирующий вход C сигнала лог.0, а на вход D любого из логических сигналов лог. 0 или лог.1, на выходе Q будет сохранён логический сигнал, подаваемый на вход D.

Рис.10.14. Условное обозначение и таблица истинности

D – триггера

При подаче на вход C сигнала лог.1, на выходе Q будет сохранён логический сигнал, подаваемый на вход D.

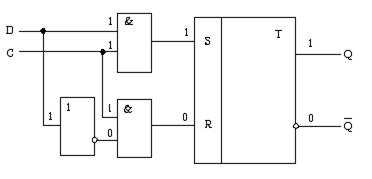

На рис.10.15 изображена логическая схема, реализующая принцип действия синхронного D - триггера. Схема состоит из асинхронного триггера, двух логических элементов И и одного инвертора. На схеме показан один из вариантов работы таблицы истинности.

Рис.10.15. Логическая схема, реализующая принцип действия синхронного D -триггера

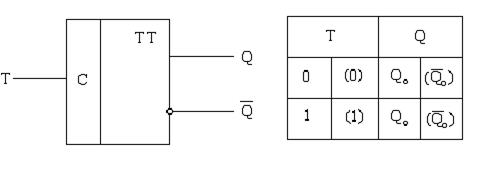

Синхронный Т - триггер (рис.10.16) предназначен для двухступенчатого запоминания информации.

Триггер имеет один синхронизирующий вход Т и два выхода: прямой Q и инверсный  .

.

Принцип действия триггера соответствует таблице истинности, из которой видно, что на вход Т - триггера поступают чередующиеся сигналы лог.0 и лог.1, при этом с прямого выхода Q снимаются: за один такт – текущие прямые логические сигналы  , за второй такт – текущие инверсные логические сигналы

, за второй такт – текущие инверсные логические сигналы  .

.

Рис.10.16. Условное обозначение и таблица истинности

Т - триггера

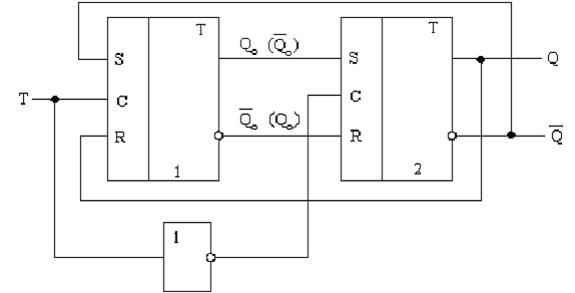

Принципиальная логическая схема синхронного Т - триггера (рис.10.17) состоит из двух синхронных RS – триггеров с синхронизирующими входами и одного инвертора. Инвертор позволяет управлять только одним триггером. Входы ведущего триггера 1 связаны с выходами ведомого триггера 2 обратными связями.

При поступлении на вход Т - триггера логического нуля, работает только ведомый триггер 2, который на выходе триггера Q установит текущее значение триггера 1 (сигнал Q0), подав при этом на вход S ведущего триггера 1 сигнал  0. Если на входе Т - триггера появится логическая единица, то триггер 1 установит на прямом выходе сигнал

0. Если на входе Т - триггера появится логическая единица, то триггер 1 установит на прямом выходе сигнал  0, сохранив при этом на входе триггера 2 значение Q0. При очередном поступлении на вход Т триггера логического нуля, ведомый триггер 2 установит на выходе триггера Q текущее значение

0, сохранив при этом на входе триггера 2 значение Q0. При очередном поступлении на вход Т триггера логического нуля, ведомый триггер 2 установит на выходе триггера Q текущее значение  0, подав при этом на вход S ведущего триггера 1 сигнал Q0. Если на входе Т - триггера появится логическая единица, то триггер 1 установит на прямом выходе сигнал Q0, сохранив при этом на выходе триггера 2 значение

0, подав при этом на вход S ведущего триггера 1 сигнал Q0. Если на входе Т - триггера появится логическая единица, то триггер 1 установит на прямом выходе сигнал Q0, сохранив при этом на выходе триггера 2 значение  0. В результате работы синхронного Т - триггера происходит двухступенчатое запоминание информации.

0. В результате работы синхронного Т - триггера происходит двухступенчатое запоминание информации.

Рис.10.17. Принципиальная логическая схема синхронного Т -триггера

Дата добавления: 2020-10-14; просмотров: 700;