Архитектура арифметического процессора

Реализация алгоритмов, в которых необходима высокая точность вычислений, наталкивается на трудности, связанные с недостаточной разрядностью представимых данных. Кроме того, в системе команд ЦП отсутствуют операции с данными, представленными с плавающей запятой, что затрудняет обработку чисел, изменяющихся в широком диапазоне. Для увеличения разрядности данных и выполнения арифметических операций с плавающей запятой можно составить соответствующие подпрограммы, однако их выполнение будет занимать значительное время. Более эффективным является использование специальных аппаратных средств. К таким средствам относится арифметический процессор (АП) Intel 8087, который называют специализированным сопроцессором для выполнения арифметических операций над числами с плавающей запятой. АП позволяет работать с тремя типами данных; целыми числами, представленными в двоичной системе счисления; целыми числами, представленными в двоично-десятичной системе счисления; вещественными числами.

Двоичные целые числа.Могут быть представлены в одном из трех форматов: слово (16-разрядное число со знаком), короткое целое (32-разрядное число со знаком) и длинное целое (64-разрядное число со знаком). В памяти целые двоичные числа записываются начиная с младшего байта.

|

| |

| |

| |

|

| |

| |

| |

|

|

|

Двоично-десятичное представление чисел.Соответствует формату, показанному на рис. 2.1, а, где d17 – d0 - обозначают 4-разрядные коды цифр числа. Таким образом, максимальное число значащих разрядов равно 18. Для записи двоично-десятичных чисел в памяти отводится 10 байт. Старший байт (на рисунке разряды 72 - 79) содержит только знак числа в старшем бите, а остальные его разряды не используются.

Вещественные числа.Могут быть представлены в одном из трех форматов. Короткий вещественный формат (КВФ) занимает 32 двоичных разряда и состоит из 23-разрядной мантиссы, 8-разрядного порядка и знака мантиссы. Длинный вещественный формат (ДВФ) занимает 64 двоичных разряда и состоит из 52-разрядной мантиссы, 11-разрядного порядка и знака мантиссы. Внутренний вещественный формат (ВВФ) занимает 80 двоичных разрядов и состоит из 64-разрядной мантиссы, 15-разрядного порядка и знака мантиссы. Все форматы вещественных чисел соответствуют стандарту IEEE 754.

Диапазон значений вещественных чисел с плавающей запятой, в котором могут выполняться вычисления арифметическим процессором, приведен в табл. 4.1. Для представления бесконечно больших чисел введены специальные коды - единица во всех разрядах порядка и нуль во всех разрядах мантиссы. Комбинации представлений мантиссы и порядка, лежащие за пределами бесконечности, обозначены NAN (от английского Not А Number - не число). Они не воспринимаются процессором как числа, так как выходят за границы допустимой точности вычислений. Таким образом, максимальный рабочий диапазон значений чисел соответствует формату ВВФ и независимо от типа исходных данных АП выполняет все операции в этом формате. Преобразование исходных данных любого типа (целые, двоично-десятичные, вещественные в КВФ и ДВФ) в формат ВВФ осуществляется сопроцессором автоматически. Причем такое преобразование всегда происходит без потери точности, так как формат ВВФ обеспечивает максимальный рабочий диапазон значений чисел. Результат вычислений может быть получен в любой желаемой форме представления (целые, двоично-десятичные, вещественные КВФ и ДВФ), т. е. получение результата связано с обратным преобразованием из внутреннего вещественного формата в требуемый. Естественно, обратное преобразование в ряде случаев может вызвать потерю точности за счет необходимости округлений. В любом случае потери точности процессор сигнализирует об этом.

Способ записи мантиссы и порядка вещественных чисел имеет следующие особенности. Числа представляются в нормализованном виде, т. е. первая значащая цифра после запятой не нуль. Например, нормализованный вид десятичного числа 0,0057 есть 0,57*10-2.

Нормализованная мантисса двоичного числа всегда будет иметь «1» после запятой. Поскольку первая цифра после запятой всегда «1», нет смысла ее хранить, и в АП она условно переносится в разряд целых. Например, если записана мантисса 010 ... О, то подразумевается, что записано число 1,010...0. Форматы вещественных чисел (рис. 2.1) содержат только знак мантиссы.

Таблица 2.1

| Диапазоны представлений | Диапазоны значений | ||||

| Знак | Порядок | Мантисса | КВФ | ДВФ | ВВФ |

| 1 1 ... 1 1 | 1 1 ... 1 1 | NAN | NAN | NAN | |

| . . . | . . . | . . . | . . . | . . . | |

| 1 1 ... 1 1 | 00...01 | NAN | NAN | NAN | |

| 1 1 ... 1 1 | 00...00 | -оо | - оо | - оо | |

| 11...10 | 11...11 | - 3,37*1038 | - 1,67*10308 | - 1,2*104932 | |

| . . . | . . . | . . . | . . . | . . . | |

| 00...00 | 00...01 | - 8,43*10-37 | - 4,19*10-307 | - 3,4*10-4931 | |

| 00...00 | 00...00 | - 0 | - 0 | - 0 | |

| 00...00 | 00...00 | +0 | +0 | +0 | |

| 00...00 | 00...01 | + 8,43*10-37 | + 4,19*10-307 | + 3,4*10-4931 | |

| . . . | . . . | . . . | . . . | . . . | |

| 1 1 ... 1 0 | 1 1 ... 1 1 | + 3,37*1038 | + 1,67*10308 | + 1,2*104932 | |

| 1 1 ... 1 1 | 00...00 | + оо | +оо | +оо | |

| 1 1 ... 1 1 | 00...01 | NAN | NAN | NAN | |

| . . . | . . . | . . . | . . . | . . . | |

| 11...11 | 11...11 | NAN | NAN | NAN |

Порядки всегда суммируются с константой смещения, выбранной так, что максимальное отрицательное значение порядка, будучи просуммировано с этой константой, дает в результате нуль. Константы смещения имеют различные значения для каждого формата вещественных чисел: КВФ - 127, ДВФ - 1023 и ВВФ - 16383.

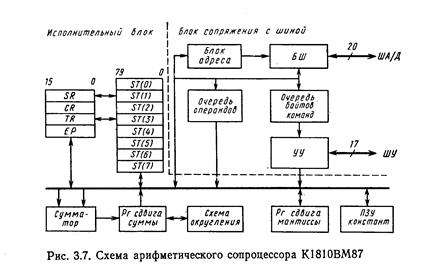

Схема АП (рис. 2.2) включает два основных блока - сопряжения с шиной (БСШ) и исполнительный ИБ. Эти блоки, как и в ЦП, осуществляют конвейерный принцип обработки данных, при котором извлечение команд и операндов выполняется параллельно с вычислениями. Команды и операнды по мультиплексированной шине адреса/данных (ША/Д) ВМ, предварительно извлекаются из памяти и размещаются в соответствующих очередях. АП может работать только в паре с центральным процессором, который в этом случае должен быть установлен в максимальный режим. Когда процессоры включены совместно, команды передаваемые по ША/Д, поступают на оба процессора одновременно. В то время как ЦП выполняет команды, АП просто «прослеживает» их прохождение, не выполняя никаких действий.

ю

ю

Рис. 2.2. Архитектура арифметического процессора Intel 8087

Это пассивное «прослеживание» продолжается до тех пор, пока в потоке команд не встречается команда ESC, которая предназначена для АП. С момента поступления команды ESC арифметический процессор начинает анализировать состояние очереди команд ЦП по сигналам QS1, QS0 (табл. 2.2). Поскольку команды в ЦП хранятся в очереди байтов команд, точный момент начала выполнения команды ESC определяется по концу выполнения предыдущей команды в очереди.

Таблица 2.2

| Состояние очереди команд | Действия с очередью команд в ЦП | |

| QS0 | QS1 | |

| Очередь не изменилась | ||

| Первый байт команды взят из очереди | ||

| Очередь реинициализирована | ||

| Очередной байт команды взят из очереди |

Как только сопроцессор определит, что последний байт предыдущей (перед ЕSС) команды взят из очереди, он приступает к выполнению своей команды. Команда ESC, как было отмечено в 1.9, обычно предваряется командой WAIT, которая переводит ЦП в состояние ожидания. Время нахождения центрального процессора в состоянии ожидания определяется активным сигналом на входе TEST. Арифметический процессор, приступая к выполнению команды, выставляет на выходе BUSY (занят) единичный сигнал, который подается на вход TEST центрального процессора и задерживает его в состоянии ожидания на время выполнения команды.

Напомним, что, находясь в состоянии ожидания, ЦП анализирует запросы прерывания и при необходимости может их обслуживать. Для обеспечения возможности совместного использования ША/Д процессоры снабжены соответствующими аппаратными средствами. Центральный процессор обладает преимущественным правом использования шины. Когда у АП возникает необходимость использования шины, например при пересылке результата операции в память, он посылает запрос на предоставление шины центральному процессору по линии RQ/GT. ЦП по этой же линии выдает сигнал разрешения на использование шины арифметическому процессору. После того как АП выполнит действия, связанные с использованием шины, он вновь посылает сигнал по линии RQ/GT, свидетельствующий об окончании использования. Этот механизм позволяет синхронизировать работу процессоров, предоставляя ресурсы ВМ в распоряжение АП.

Закончив выполнение команды, АП сбрасывает сигнал BUSY, делая активным сигнал на входе TEST, и выводит ЦП из состояния ожидания. Из приведенного описания ясно, что побудительным стимулом для включения в работу сопроцессора является наличие кода команды ESC в потоке команд совместно включенных процессоров. Код операции, которую выполняет АП, содержится в полях Х и Y команды ESC (см. рис. 1.9). В ряде случаев при выполнении команд в АП возникают исключительные ситуации, связанные с переполнением, потерей точности при округлениях и т. п. Для обработки таких ситуаций может потребоваться вмешательство ЦП, которому предписаны соответствующие программы обработки исключительных ситуаций. Механизм передачи управления на эти программы основан на использовании системы прерываний. Для этой цели АП имеет выход INT запроса прерываний, на котором генерируется сигнал запроса, когда возникает та или иная исключительная ситуация.

Рассмотренные аппаратные и программные средства процессоров позволяют достаточно просто организовать их взаимодействие и значительно расширить возможности ЦП.

Дата добавления: 2018-11-26; просмотров: 1414;