Архитектура центрального процессора

Существует много различных подходов к реализации структурной схемы (архитектуры) центрального процессора (ЦП). В нашей стране наибольшее распространение получила архитектура, предложенная американской фирмой Intel. Именно поэтому мы сосредоточим основное внимание на изучении процессоров, построенных по идеологии Intel и вычислительных машин, реализованных на базе этих процессоров фирмой IBM. Начнем с первого 16-разрядного процессора Intel 8086, разработанного еще в 1978 году и послужившего основой для разработки многих поколений ЦП, вплоть до Pentium 4.

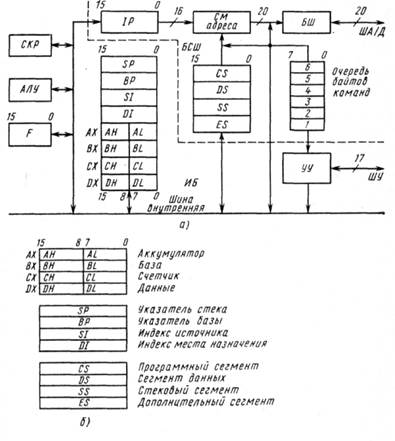

При разработке Intel 8086 применены интересные архитектурные решения, к которым, в частности, относится разделение функций сопряжения с шиной и выполнения команд. В соответствии с этим структуру процессора (рис. 1.1, а) можно условно разделить на две части: блок сопряжения с шиной (БСШ) и исполнительный блок (ИБ). Блок сопряжения с шиной БСШ обеспечивает функции, связанные с выборкой операндов и кодов команд из памяти, запоминанием операндов, установлением очередности команд, а также формированием адресов операндов и команд. Исполнительный блок ИБ получает команды из очереди команд и указывает адрес операнда для БСШ. Операнды из памяти поступают через БСШ на обработку в ИБ, который выполняет предписанные операции и возвращает результаты в память через БСШ. Важно подчеркнуть, что эти блоки работают параллельно, причем БСШ обеспечивает извлечение кодов команд заблаговременно, в то время как ИБ выполняет текущую команду. Это повышает пропускную способность мультиплексированной шины адреса/данных ША/Д и увеличивает быстродействие ЦП.

Рассмотрим назначение и работу отдельных узлов микропроцессора Intel 8086. В нем имеется четырнадцать 16-разрядных регистров, которые по своему назначению можно разделить на три группы (рис. 1.1, б). Регистры АХ, ВХ, СХ, DX образуют группу регистров общего назначения (РОН). Эти регистры могут без ограничений участвовать в выполнении арифметических и логических операций. Некоторые другие операции, например операции над цепочками байтов и слов, предписывают регистрам данной группы специальное использование: АХ - аккумулятор, ВХ - база, СХ - счетчик, DX - данные. В отличие от регистров других групп РОН обладают свойством раздельной адресации старших и младших байтов. Поэтому РОН можно рассматривать как совокупность двух наборов 8-разрядных регистров: набора Н, содержащего АН, ВН, СН, DH, и набора L, содержащего AL, BL, CL, DL. Регистры всех других групп являются неделимыми и оперируют 16-разрядными словами, даже в случае использования только старшего или младшего байта.

Регистры SP, BP, SI и DI образуют группу указательных и индексных регистров, назначение которых заключается в том, что они содержат значения смещений, используемых для адресации в пределах текущего сегмента памяти. При этом регистры-указатели SP и ВР хранят смещения адреса в пределах текущего сегмента памяти, выделенного под стек, а индексные регистры SI и DI содержат смещения адреса в пределах текущего сегмента памяти, выделенного под данные. С этим связаны и обозначения регистров: SP - указатель стека, ВР - указатель базы, SI - индекс источника и DI - индекс места назначения. Регистры этой группы могут использоваться и как регистры общего назначения.

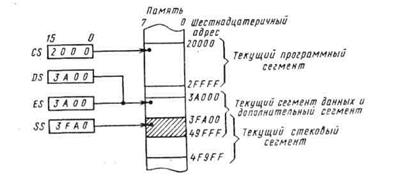

Регистры CS, DS, SS и ES, образующие группу сегментных регистров, играют важную роль во всех действиях ЦП, связанных с адресацией памяти. Обозначения регистров расшифровываются следующим образом: CS - кодовый или программный сегмент, DS - сегмент данных, SS - стековый сегмент и ES - дополнительный сегмент. Содержимое любого из этих регистров определяет текущий начальный адрес сегмента памяти, выделенного пользователем под информацию, соответствующую названию регистра.

Содержимое регистра CS определяет начальный адрес сегмента памяти, в котором располагается объектный код программы. Выборка очередной команды осуществляется относительно содержимого CS с использованием значения указателя команд IP. Содержимое регистра DS определяет начальный адрес текущего сегмента данных, так что обращение к данным в памяти ЦП осуществляет относительно содержимого DS. Для обращения к другим трем сегментам: дополнительному, стековому или программному - используется специальный указатель, который называется префиксом замены сегмента и располагается в соответствующих командах.

Содержимое регистра SS определяет текущий сегмент, выделенный для организации стека. Все обращения к памяти, при которых для вычисления адреса прямо или косвенно используются регистры ВР или SP, осуществляются относительно содержимого регистра SS. К таким обращениям относятся, например, все операции со стеком, включая и те, которые связаны с операциями вызова подпрограмм, прерываниями и операциями возврата. Обращения к данным, использующие регистр ВР (но не SP), могут производиться также и относительно одного из трех других сегментных регистров путем использования префикса замены сегмента.

Рис. 1.1. Архитектура центрального процессора Intel 8086 и его регистры.

Содержимое регистра ES определяет начальный адрес сегмента, рассматриваемого как дополнительный сегмент данных. В частности, обращения к данным в операциях с цепочками байтов или слов осуществляются относительно ES, а в качестве смещения берется содержимое DI.

Рис. 1.2. Регистр флагов

Кроме перечисленных регистров имеются два 16-разрядных регистра: IP - указатель команд и F - регистр флагов. В регистре IP формируется относительный (относительно CS)адрес команды, подлежащей исполнению. В регистре F (рис. 1.2) используются следующие девять разрядов: CF - перенос, PF - четность, AF - вспомогательный перенос, ZF - нулевой результат, SF - знак, TF - пошаговый режим, IF - разрешение прерывания, DF - направление, OF - переполнение. Неиспользованные разряды на рисунке заштрихованы.

Флаги AF, CF, PF, SF и ZF характеризуют признаки результата последней арифметической, логической или иной операции, влияющей на эти флаги. Установка флага производится в следующих случаях:

AF - при выполнении операции производится перенос «1» из младшей тетрады байта в старшую или осуществляется заем «1» из старшей тетрады;

CF - при переносе «1» из старшего бита байта (слова) или при заеме единицы в старший бит;

PF - если в представлении результата операции содержится четное число единиц;

SF - при получении «1» в старшем бите результата;

ZF - если в результате выполнения операции получено нулевое значение.

К этой группе флагов относится также флаг OF, который устанавливается при наличии переполнения в результате выполнения арифметических операций над числами со знаком.

Флаги DF, IF и TF используются для управления работой процессора. Флаг DF управляет направлением обработки данных в операциях с цепочками байтов или слов. При DF=1 цепочка обрабатывается снизу вверх, т. е. происходит автоматическое уменьшение (автодекремент) адреса текущего элемента цепочки. При DF=0 цепочка обрабатывается сверху вниз, т. е. происходит автоматическое увеличение (автоинкремент) адреса.

Флаг IF предназначается для разрешения или запрещения (маскирования) внешних прерываний. При IF = 0 внешние прерывания запрещены, т. е. процессор не реагирует на их запросы.

Флаг TF применяется для задания процессору пошагового режима, при котором процессор после выполнения каждой команды останавливается и ждет внешнего запуска. Пошаговый режим задается установкой флага TF= 1 и обычно необходим при отладке программ.

Основные операции по обработке данных выполняются в арифметико-логическом устройстве (АЛУ), с которым связана схема коррекции результатов (СКР), используемая при работе с данными, представленными в двоично-десятичных кодах. Связь внутренних узлов ЦП с шиной ША/Д осуществляется через буфер шины БШ, состоящий из двунаправленных усилителей с тремя устойчивыми выходными состояниями.

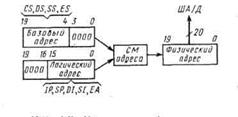

Усовершенствование архитектуры Intel 8086 связано также с введением в структуру микропроцессора специального сумматора (СМ) для вычисления адресов памяти.

Как отмечалось выше, разрядность адресов микропроцессора равна 20. Однако для упрощения операций хранения и пересылки адресной информации процессор манипулирует 16-разрядными логическими адресами, к которым относятся начальные (базовые) адреса сегментов памяти и значения смещений в этих сегментах. Логические адреса используются для вычисления 20-разрядных физических (абсолютных) адресов с помощью следующей процедуры. Содержимое каждого сегментного регистра рассматривается как 16 старших разрядов А19-А4 начального адреса соответствующего сегмента. Младшие разряды A3-А0 этого адреса всегда полагаются равными нулю и поэтому не запоминаются в регистрах, а приписываются справа к старшим разрядам во время операции вычисления физических адресов. Эта операция выполняется сумматором адреса, расположенным в блоке БСШ, и состоит в сложении 20-разрядного начального адреса сегмента с 16-разрядным смещением, которое дополняется четырьмя старшими разрядами А19-А16, равными нулю, как показано на рис. 1.3. Сумматор адресов осуществляет, например, следующие вычисления: CS + IP - при выборке очередной команды, SS + SP - при обращении к стеку, DS + SI и ES + DI - при обработке строк, DS + EA- при обращении к запоминающему устройству с произвольной выборкой (ЕА - исполнительный адрес, формирование которого описано ниже).

|

Рис. 1.3. Вычисление физического 20-разрядного адреса

Поскольку младшие четыре разряда начального адреса любого сегмента должны быть равны нулю, значения начальных адресов сегментов выбираются кратными 16. Наибольшая емкость памяти, отводимой под один сегмент, определяется максимальным значением 16-разрядного смещения и составляет 64К байт.

Рис 1.4. Пример размещения сегментов в памяти

В несложных системах с емкостью памяти не более 64К байт можно отказаться от сегментации памяти и установить все сегментные регистры в нулевое состояние. При этом 16-разрядный адрес смещения будет фактически абсолютным адресом. При использовании системы с большой емкостью памяти (до 1М байт включительно) начальные адреса сегментов задаются исходя из особенностей структуры программного обеспечения и данных, хранимых в памяти. На рис. 1.4 приведен пример размещения сегментов памяти.

Дата добавления: 2018-11-26; просмотров: 1178;