ИНТЕГРАЛЬНЫЕ СХЕМЫ НА ОСНОВЕ АРСЕНИДА ГАЛИЯ

8.1 Общие сведения

Каждая из рассмотренных цифровых схем (биполярные ТТТЛ и n-канальные КМОП структуры) имеет свои преимущества и недостатки, определяющие область их применения. Биполярные транзисторы пригодны для коммутации сравнительно больших токов, благодаря чему даже при высоком быстродействии паразитные емкости соединений между корпусами мало влияют на скорость их работы. Соединением многих биполярных микросхем, каждая из которых имеет умеренную сложность, можно создавать быстродействие узлов аппаратуры. Для построения ЭВМ и узлов дискретной автоматики сейчас наиболее широко применяются схемы ТТЛ и ТТЛШ. Сверхскоростные устройства строятся на микросхемах ЭСЛ. Постоянно повышающиеся требования, с точки зрения снижения потребляемой мощности, уменьшения габаритных размеров и стоимости устройства, повлекли за собой поиски новых путей, позволяющих улучшить рабочие характеристики МОП-транзисторов и увеличить степень интеграции базовых ЛЭ, выполняемых на биполярных транзисторах.

Одним из новых направлений в последние годы явилось развитие интегральной инжекционной логики (И2Л), которая развилась на базе самой первой простейшей логики с непосредственными связями (ТЛ НС). С помощью схем И2Л удалось увеличить плотность компоновки и снизить рассеиваемую мощность на ЛЭ. Плотность компоновки схем И2Л даже превышает плотность МОП-схем (удается разместить более 1000 элементов на 1 мм2). Небольшая рассеиваемая мощность объясняется отсутствием резисторов. Инжекция носителей в область базы транзистора осуществляется с помощью активных генераторов тока, выполненных на p-n-p-транзисторах. Большое быстродействие при малых мощностях объясняется незначительными паразитными емкостями, отсутствием накопления заряда и очень небольшой разницей логических уровней. Причем, на одном кристалле можно размещать цифровые и аналоговые схемы. Примером такой схемы может служить выпускаемая серийно микросхема 541. Кроме того, были созданы схемы И3Л (серия 583ВГ2) . Однако широкого применения они еще не получили. В последние годы активно разрабатываются и широко применяются микросхемы с диодами Шоттки – ТТЛШ и МОП-схемы с n-каналом, а также КМОМ, совместимые с цоколевками массовых серий ТТЛ. Одним из новых направлений является развитие интегральной схемотехники на основе арсенида галлия.

8.2 Базовый ЛЭ сверхбыстродействующих ИС К6500

Микросхемы К6500 представляют собой цифровые схемы сверхвысокого быстродействия, выполненные на основе арсенид-галлиевых полевых транзисторов с затвором Шоттки.

Микросхемы К6500 по сравнению с ИС К500, К1500 имеют в 4 – 6 раз меньшую мощность потребления на один ЛЭ и в 3¸8 раз большую частоту переключения триггера и меньшую задержку на ЛЭ.

В серии используются следующие основные параметры логических сигналов: максимальная частота функционирования Pmax не менее 1000 МГц; длительность фронта (среза) выходного сигнала 0,16-0,3 нс; выходное напряжение при Rн = 50 Ом низкого уровня – 0,2-0,1 В, высокого уровня (U0H) 0,9-1,5 В; входной ток низкого уровня не менее – 0,5 мА, высокого уровня (IIH) не более 1 мА; помехозащищенность низкого и высокого уровня не менее 0,1 В. Микросхемы выполнены в плоских планарных металлокерамических корпусах с числом выводов 16, 24, 42. При обозначении ИС К6500 микросхемы эксплуатируются в диапазоне температур – 100 ¸ + 70 0С, а при обозначении 6500: – 600 ÷ + 125 0С.

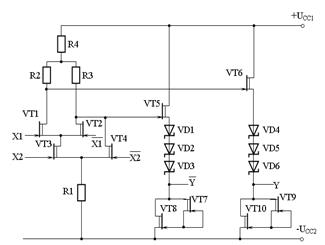

Микросхемы К6500 построены на основе базовых ЛЭ истоково-связанной логики на полевых транзисторах с управляющим затвором Шоттки. Один из основных вариантов реализации базового ЛЭ на полевом транзисторе Шоттки приведен на рисунке 8.1.

В структурной схеме ЛЭ имеются входные и выходной формирователи сигналов и сам базовый ЛЭ. Базовый элемент построен по схеме переключателя тока на основе дифференциальных пар транзисторов VT1, VT2 и VT3, VT4, резистора R1, определяющего ток истока, значения нагрузочных резисторов R2, R3 и резистора смещения R4 для согласования по уровням напряжения выходов истокового переключателя тока и выходных истоковых повторителей на транзисторах VT5, VT6. Диоды Шоттки VD1 – VD8 и транзисторы VT7¸VT10 в цепях истоков выходных транзисторов необходимы для согласования с выходным формирователем и стабилизации выходного напряжения.

Питание ЛЭ и формирователей осуществляется от двух источников напряжения: UCC1 = (4 ± 0,2) В и UCC2 = (– 2,45 + 0,12) В. Цепи питания UCC1 выходного формирователя и остальной части схемы разделены.

Входные формирователи предназначены для согласования внешних цепей с напряжениями сигналов 0 -1 В с базовым ЛЭ, в котором сигналы Х1, Х2 имеют уровни 0,5 В для прямых и – 0,5 В для инверсных значений. Схема входного формирователя близка к схеме базового элемента: она состоит из переключателя тока и выходных истоковых повторителей. На другой вход поступает внешний сигнал с логическим перепадом около 1 В. Формирователь преобразует этот сигнал в парафазный Х,  с уровнем ± 0,5 В.

с уровнем ± 0,5 В.

Выходной формирователь также построен на основе переключателя тока и мощного выходного ключевого элемента, обеспечивающего преобразование уровней внутренних сигналов Y,  в уровни внешних сигналов, а также необходимую нагрузочную способность ЛЭ. Выходной ток преобразователя равен 10 мА, а в пределе до 30 мА.

в уровни внешних сигналов, а также необходимую нагрузочную способность ЛЭ. Выходной ток преобразователя равен 10 мА, а в пределе до 30 мА.

Для перехода от маломощных внутренних цепей с токами до 1 мА к мощному выходному транзистору и обеспечения режима его переключения с частотой 1 ГГц требуется включить между внутренней логической схемой и выходом микросхемы два-три каскада усиления мощности. Потребляемая мощность 0,55…2,6 Вт для микросхем различной сложности. Энергопотребление определяется мощностью выходных формирователей.

Рисунок 8.1 – Типовой базовый логический элемент ИС 6500

Длительность фронта и среза не более 0,25 нс при работе на коаксиальные линии с волновым сопротивлением 50 Ом и сопротивлением нагрузки 50 Ом.

8.3 Логические элементы, регистры, счетчики

Цифровые микросхемы К6500 предназначены для обработки цифровых сигналов с тактовой частотой до 1000 МГц в контрольно-измерительных приборах, аппаратуре связи и ЭВМ. При эксплуатации ИС К6500 имеют предельно допустимые режимы, приведенные ниже. В состав серии 6500 входят: два логических элемента ЛР1 и ЛР2, счетный триггер ТТ1, 4-разрядный ИР1 и 8-разрядный ИР2 сдвигающие регистры и два двоичных счетчика – ИЕ2 (4-разрядный), ИЕ3 (8-разрядный).

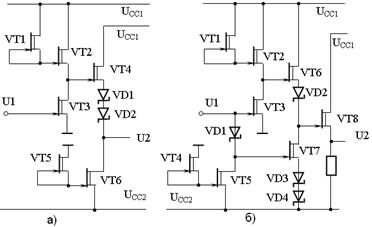

Логические элементы. Логические элементы и выходные каскады, которые лежат в основе построения элементов типа ЛР, триггеров и регистров показаны на рисунке 8.2.

а − ЛР1,ЛР2 ТТ1, ИР1; б − ИР2

Рисунок 8.2 – Логический элемент и выходной каскад ИС 6500

Простейший логический элемент выполнен на основе инвертора на транзисторе VT1 и истоковом повторителе на транзисторе VT4, в истоке которого стоят два последовательно включенных диода, понижающих уровень лог. 1.

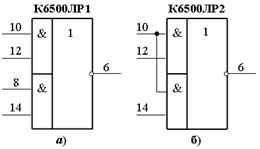

Основой второго логического элемента является фазорасщепляющий каскад на VT3 и сложный истоковый повторитель на VT6 и VT7, работающий на простой истоковый повторитель на VT8. Условные графические обозначения четырехвходового 2И-ИЛИ-НЕ ИС К6500ЛР1 и трехвходового ЛЭ 2И-ИЛИ-НЕ ИС К6500ЛР2 приведены на рисунке 8.3. Микросхема К6500 ЛР1 реализует функцию  , где a, b, c, d – входные переменные. В зависимости от входных аргументов микросхема может реализовать разнообразные функции, включая

, где a, b, c, d – входные переменные. В зависимости от входных аргументов микросхема может реализовать разнообразные функции, включая  ,

,  , равнозначности и неравнозначности. Задержка распространения сигнала 0,42 нс, потребляемая мощность – 0,55 Вт. Микросхема К6500 ЛР2 реализует функцию

, равнозначности и неравнозначности. Задержка распространения сигнала 0,42 нс, потребляемая мощность – 0,55 Вт. Микросхема К6500 ЛР2 реализует функцию  . Ее функциональные возможности несколько меньше, чем у ЛР1.

. Ее функциональные возможности несколько меньше, чем у ЛР1.

а −ИС К6500ЛР1; б −К6500ЛР2

Рисунок 8.3 – Условное графическое обозначение

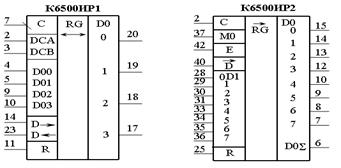

Регистры. Условное графическое обозначение и функциональная схема универсального сдвигового регистра К6500 ИР1 приведены на рисунке 8.4. Регистр имеет следующие режимы работы: сдвиг вправо (в сторону старших разрядов); сдвиг влево (в сторону младших разрядов); параллельная загрузка; режим хранения информации; установка низкого напряжения на выходах (сброс).

При установке микросхемы необходимо подключать сопротивление нагрузки к выводам 18 и 19 со значением 50 Ом, а к выводам 17 и 20–25 Ом. Тактирование (сдвиг) информации происходит по спаду синхронизирующего импульса на входе С.

Восьмиразрядный сдвиговый регистр (ИС К6500ИР2 – рисунок 8.4) может работать в режиме последовательной записи информации, синхронизированной по срезу тактового сигнала, имеет режимы сброса и установки, а также обеспечивает режим циклирования (кольцевого сдвига).

Микросхема имеет выход полусумматора, позволяющий формировать псевдослучайную последовательность длиной 27 – 1. Микросхема может управляться от ТТЛШ ИС, для этого значения напряжений логических уровней по входам 25, 28 – 31, 33 – 37 соответствуют ТТЛ и ТТЛШ.

Рисунок 8.4−Условное графическое обозначение ИС

Счетчики. В серии ИС 6500 выпускаются два двоичных счетчика: ИЕ2 и ИЕ3. Микросхема 6500 ИЕ2 - четырехразрядный синхронный двоичный счетчик имеет следующие основные режимы работы: преобразование времени в цифровой код (ПВК), преобразование длительности в цифровой код (ПДК), деление частоты с коэффициентами 2, 4, 8, 16.

Задержка распространения сигнала не более 1,5 нс.

Микросхема ИС 6500ИЕ3 – восьмиразрядный двоичный счетчик, который может быть использован в качестве счетчика, делителя и преобразователя, длительность – код.

9 ШИФРАТОРЫ

Шифратор (CODER) – это устройство, осуществляющее преобразование десятичных чисел (позиционный код) в двоичный код. Шифратор имеет m входов, пронумерованных десятичными числами (0, 1, 2... m – 1) и n выходов, причем 2n ³ m . Подача управляющего сигнала на один из входов приводит к появлению на выходе n-разрядного двоичного числа, соответствующего номеру возбужденного входа. Строятся шифраторы, как правило, на небольшое число (до 8) входов, а при большом числе входов пользуются вычислительными приемами, позволяющими перевести любое десятичное число в двоичный код.

Шифраторы широко применяются в устройствах автоматики, особенно в устройствах ввода/вывода информации. На клавиатуре ввода имеются клавиши с десятичными цифрами, буквенный алфавит, а при нажатии клавиши позиционный код должен преобразоваться в двоичный.

Рассмотрим вариант построения восьмивходового полного шифратора с нулевыми активными значениями входных сигналов. Закон функционирования такого шифратора представлен в таблице 9.1.

Решение задачи в общем виде в случае восьми переменных представляется весьма трудным. Однако можно заметить, что исходная функция принимает нулевое значение в каждой строке всего лишь один раз, что упрощает решение задачи. Нетрудно заметить, что логическая единица на выходе y3 получается в случае, если перемножить аргументы x4, x5, x6 и x7, а результат проинвертировать:

.

.

Для остальных сигналов  ,

,  .

.

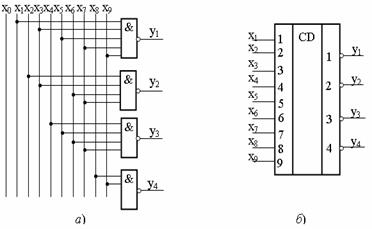

Для реализации данного шифратора требуется три ЛЭ 4И-НЕ (рисунок 9.1, а).Судя по полученным выражениям, входной сигнал x0 не участвует в формировании выходного кода. Отсутствие сигнала на любом из остальных выходов x1 - x7 указывает на то, что установлен нулевой набор. На рисунке 9.1, б представлено условное графическое обозначение данного шифратора, здесь символ CD образован из букв, входящих в английское слово CODER. На входах показано инверсное управление, поскольку активным уровнем является лог. 0.Следует отметить, что шифратор может иметь и инверсные выходы. В этом случае выходные сигналы в соответствии с законом отрицания могут быть описаны следующими выражениями:

Таблица 9.1

| N | Входные сигналы | Выходной код | |||||||||

| x0 | x1 | x2 | x3 | x4 | x5 | x6 | x7 | y3 | y2 | y1 | |

Рассмотрим вариант построения шифратора для случая, когда при нажатии кнопки вырабатывается сигнал с активным уровнем, соответствующим лог. 1. Имеем десятичный позиционный код x0, x1, ... x9, образуемый набором из 10 клавиш, пронумерованных 0 – 9. Необходимо получить нормально взвешенный код 8-4-2-1 – y4, y3, y2, y1, соответствующий номеру нажатой кнопки. Чтобы получить логические выражения для выходных сигналов, воспользуемся таблицей истинности (таблица 9.2.).

По приведенным в таблице 9.2. соответствиям входного позиционного и выходного двоичного кода можно записать выражение для любой переменной yi. Например, переменная y1 принимает значение лог. 1 в том случае, когда такое же значение устанавливается на одном из входов x1, x3, x5, x7 или x9, следовательно,

y1 = x1 V x3 V x5 V x7 V x9.

На остальных входах y2 = x2 V x3 V x6 V x7, y3 = x4 V x5 V x6 V x7, y4 = x8 V x9. При реализации шифратора на элементах ИЛИ-НЕ, выходные сигналы окажутся инвертированными (рисунок 9.2, а). Условное графическое изображение этого шифратора будет таким, как показано на рисунке. 9.2.

а − Функциональная схема; б − условное графическое обозначение шифратора

Рисунок 9.1 – Обозначение шифратора

Входной сигнал x0 на условном изображении шифратора отсутствует, поскольку не участвует в формировании сигналов выхода. В серии К555 представлены ИС К555 ИВ1, ИВ2 и ИВ3.

Таблица 9.2

| N | Входные сигналы | Выходной код | ||||||||||||

| x0 | x1 | x2 | x3 | x4 | x5 | x6 | x7 | x8 | x9 | y4 | y3 | y2 | y1 | |

а − Функциональная схема; б − условное графическое обозначение шифратора

Рисунок 9.2 – Обозначение шифратора

Приоритетный шифратор К555 ИВ1 (рисунок 9.3, а) осуществляет преобразование из восьми каналов в три. Приоритетность шифрации означает то, что при одновременном запросе с нескольких каналов (одновременном нажатии нескольких кнопок) на выходе будет сформирован код старшего канала. Выявление приоритета существенно усложняет функциональную схему. Схема шифратора включает две ступени. Первая ступень выполнена на инверторах и обеспечивает сигналы адреса шифрованного кода на входах второй ступени шифратора. Вторая – на ЛЭ И-ИЛИ-НЕ, позволяет осуществлять адреса шифрованного кода на схемах И и передачу полученного кода схемой ИЛИ на выход канала. Вход старшего разряда шифратора является входом разрешения следующего шифратора при их объединении для наращивания разрядности. Выход разрешения  является выходом схемы И входных схем шифратора. Выход разрешения

является выходом схемы И входных схем шифратора. Выход разрешения  объединенный со входом выбора

объединенный со входом выбора  , обеспечивает на выходе ЛЭ признак выбора

, обеспечивает на выходе ЛЭ признак выбора  следующей группы. Входные сигналы шифратора обозначены

следующей группы. Входные сигналы шифратора обозначены  , а выходной код

, а выходной код  (в обоих случаях активным уровнем является лог. 0.).

(в обоих случаях активным уровнем является лог. 0.).

Микросхема К555 ИB2 отличается от предыдущей лишь наличием трех состояний выхода.

Рисунок 9.3 – Условное графическое обозначение шифратора: а −ИС К555ИВ2; б − К555 ИВ3

Микросхема К555 ИB3 – шифратор приоритетов десяти входов – четырех выходов, предназначен для преобразования сигналов в четырехразрядный двоично-десятичный код (рисунок 9.3, б). Активным уровнем для шифратора на входе и выходе является напряжение низкого уровня. Ноль кодируется в том случае, когда все девять информационных входов имеют высокий уровень напряжения. В сериях КМОП имеется шифратор К1564 ИB3.

ДЕШИФРАТОРЫ

Дешифратором называется комбинационное цифровое устройство с несколькими входами и выходами, у которого каждой комбинации входных сигналов соответствует активное значение только одного определенного выходного сигнала. Дешифраторы широко используются для преобразования двоичных кодов в управляющие сигналы различных цифровых устройств. Они используются в качестве коммутаторов распределителей информационных каналов и синхроимпульсов, для организации адресной логики в запоминающих устройствах, при выводе символов на печать, для преобразования двоично-десятичного кода в десятичный при управлении цифровыми индикаторами и т.д.

Переключательные функции полного дешифратора имеют следующий вид:

Если число входных равно m, то максимально возможное число выходных шин равно N, где N = 2m, и такой дешифратор называется полным. Различные способы вычисления конъюнкций дают возможность получать разнообразные структуры дешифраторов: линейные, прямоугольные, матричные, пирамидальные. Рассмотрим принцип построения линейного дешифратора.

Дата добавления: 2020-03-17; просмотров: 1134;