На основе базовых ЛЭ спроектированы все микросхемы, входящие в состав серий КМОП: 561, К561, 564, 564В, К564, Н564, КР1561, 1564.

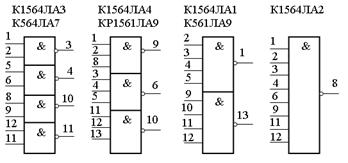

В состав КМОП ИС входят простейшие ЛЭ, реализующие функции И-НЕ (ИС типа ЛА), ИЛИ-НЕ (ИС типа ЛЕ), И (ИС типа ЛИ), НЕ (ИС типа ЛН), комбинированные (ИС типа ЛП, ЛС), триггеры Шмитта (ИС типа ТЛ), ключи (ИС типа КТ). Микросхемы типа И-НЕ являются наиболее распространенными ЛЭ и выпускаются в виде набора 2-3-4-8 -входовых ячеек в корпусе одной микросхемы. На рисунке 6.7 приведены условные изображения микросхем такого типа. Микросхемы типа ЛА реализуют функцию m И-НЕ, где m – количество входов. Поскольку в ИС типа ЛА необходимо последовательное соединение МОП-транзисторов, выходные напряжения  , в условиях номинальной нагрузки и наличия помех, имеют несколько отличные значения выходных уровней от простейшего МОП-инвертора (отличия выражаются в более высоком уровне

, в условиях номинальной нагрузки и наличия помех, имеют несколько отличные значения выходных уровней от простейшего МОП-инвертора (отличия выражаются в более высоком уровне  , и более низком уровне

, и более низком уровне  ).

).

Рисунок 6.7 – Микросхемы типа К1564ЛА

Для того чтобы при последовательном соединении m транзисторов напряжение  не превышало допустимого уровня, ширина каналов этих транзисторов увеличена в m раз. МОП-транзисторы с большей шириной канала имеют более высокую крутизну характеристик и обеспечивают меньшее сопротивление открытого канала. Логические элементы И-НЕ с открытым стоком. Микросхема 564ЛА10 имеет особенность, состоящую в том, что на ее выходе включен не КМОП-ннвертор, а МОП-транзистор с каналом п-типа, сток которого соединен с ЛЭ (рисунок 6.8 ). Эта логическая схема называется «с открытым стоком» (по аналогии с ТТЛ ИС с открытым коллектором). Она может использоваться для подключения любой нагрузки между выходом и положительным источником питания с номинальным током 16 – 34 мА при Un = 5 – 10 В (например, элементов индикации и др.). Выходной транзистор открыт только при высоком напряжении на его затворе, т.е. когда на вход ЛЭ И-НЕ поступят две лог. 1.

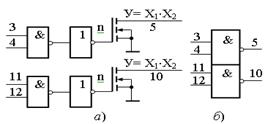

не превышало допустимого уровня, ширина каналов этих транзисторов увеличена в m раз. МОП-транзисторы с большей шириной канала имеют более высокую крутизну характеристик и обеспечивают меньшее сопротивление открытого канала. Логические элементы И-НЕ с открытым стоком. Микросхема 564ЛА10 имеет особенность, состоящую в том, что на ее выходе включен не КМОП-ннвертор, а МОП-транзистор с каналом п-типа, сток которого соединен с ЛЭ (рисунок 6.8 ). Эта логическая схема называется «с открытым стоком» (по аналогии с ТТЛ ИС с открытым коллектором). Она может использоваться для подключения любой нагрузки между выходом и положительным источником питания с номинальным током 16 – 34 мА при Un = 5 – 10 В (например, элементов индикации и др.). Выходной транзистор открыт только при высоком напряжении на его затворе, т.е. когда на вход ЛЭ И-НЕ поступят две лог. 1.

а − функциональная схема; б − условное изображение

Рисунок 6.8 – Микросхема 564ЛА10

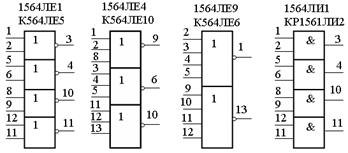

В других случаях выходной транзистор заперт, что соответствует высокоимпедансному состоянию Z. Следовательно, на его выходе можно применять монтажную логику. Микросхемы типа ИЛИ-НЕ представлены 2-3-4-входовыми ЛЭ типа ЛЕ (рисунок 6.9). Они выполняют логическую функцию m ИЛИ-НЕ, где m – количество входов. Этот тип микросхем также имеет более высокий уровень  и более низкий уровень

и более низкий уровень  , по сравнению с простейшими КМОП- инверторами. Чтобы величина

, по сравнению с простейшими КМОП- инверторами. Чтобы величина  не была ниже предельного уровня, ширина каналов МОП-транзисторов с каналом р-типа больше в m раз, чем у МОП-транзисторов с каналом n-типа. Микросхемы типа ЛИ являются неинвертирующим ЛЭ.

не была ниже предельного уровня, ширина каналов МОП-транзисторов с каналом р-типа больше в m раз, чем у МОП-транзисторов с каналом n-типа. Микросхемы типа ЛИ являются неинвертирующим ЛЭ.

Рисунок 6.9 − Микросхемы типа К561ЛЕ

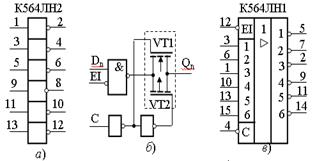

В качестве примера на рисунке 6.9 показана микросхема 1564ЛИ1 (КР1561ЛИ2), содержащая 4 ЛЭ 2И. Прямой выходной сигнал получают путем дополнительного инвертирования выходного сигнала элемента 2И-НЕ. Микросхемы типа ЛН являются либо инверторами, либо повторителями входного сигнала и могут иметь дополнительные управляющие входы. Микросхема 564ЛН2 содержит 6 буферных инверторов (рисунок 6.10, а). Для микросхемы необходимо только одно напряжение питания, поэтому она используется, как транслятор логических уровней от КМОП к ТТЛ. Если на вывод 14 подать напряжение питания 5 В, то можно передавать уровни от КМОП к ТТЛ, причем нагрузочная способность инвертора – 2 ТТЛ входа (т.е.  ³ 3,2 мА при выходном напряжении низкого уровня не менее 0,4 В). Время задержки распространения не более 80 нс.

³ 3,2 мА при выходном напряжении низкого уровня не менее 0,4 В). Время задержки распространения не более 80 нс.

Микросхема 564ЛН1 содержит шесть стробируемых инверторов (рисунок 6.10, в). Каждый инвертор (точнее, двухвходовой элемент ИЛИ-НЕ) имеет вход Dn и выход Qn (рисунок 6.10, б). Кроме того, на вторые входы всех шести инверторов от общего выхода EI (разрешение по входу) подается разрешающий сигнал с активным низким уровнем. Если Е1 = 1, то входы Dn запрещаются, а все выходы Qn имеют низкий уровень. Второй общий вход управления ЕО(разрешение по выходу) при высоком входном уровне переводит все выходы в состояние Z (выходное сопротивление более 10 МОм).

Рисунок 6.10 – Условное графическое изображение: а − К564ЛН2; в − К564ЛН1; б − принципиальная схема одного ЛЭ

Третье состояние упрощает работу выходов на шину данных. Нагрузочная способность каждого инвертора – 2 ТТЛ входа. Напряжение питания микросхем от 5 до 15 В. Максимальное быстродействие обеспечивается при Un = 15 В: время задержки распространения составляет 65 нс, время перехода от Z-состояния к высокому выходному уровню 40 нс. При напряжении питания Un = 5 В все переходные процессы затягиваются в 3 раза.

6.8 Рекомендации по применению ИС КМОП

Для обеспечения высокой надежности работы устройств на КМОП- структурах необходимо применять дополнительные меры защиты от воздействия статического электричества, от воздействия импульсных полей и др. Электростатический разряд возникает, если электростатический заряд с высоким потенциалом относительно земли попадает на выходы ИС. Если микросхема хотя бы однажды подвергалась воздействию статического электричества, она становится менее надежной. Уровень безопасного электростатического потенциала ИС К564, обеспечиваемого схемой защиты, составляет 100 В. Второй вид пробоя – это тиристорная защелка, которая приводит к перегоранию микросхем, расплавлению и металлизации. Защелка формируется двумя паразитными биполярными транзисторами, образующими четырехслойную структуру – тиристор. Большой импульсный ток переводит тиристор в положение «Включено». Если тиристор пробудет во включенном состоянии хотя бы сотые доли миллисекунды, то ток включенного тиристора может разрушить микросхему. Поэтому все входные сигналы не должны выходить за пределы напряжения питания Un. Тиристор срабатывает при кратковременном замыкании на Un или заземлении, либо от импульсов фототока, создающего прямое смещение на переходе. Если проектируются мультивибраторы на ИС КМОП, в них следует ограничивать токи перезарядки конденсаторов микроамперными уровнями, включая последовательные резисторы. Входы КМОП не должны оставаться неприсоединенными. Опасны случаи разъединения печатных плат, находящихся под питанием. При совместной работе ТТЛ на нагрузку КМОП рекомендуется подключать резисторы утечки между питанием и входом КМОП (1–10 кОм). Если требуется параллельное соединение входов и выходов элементов, то они должны быть из одной микросхемы. Нельзя применять нагрузки Сн > 5000 пФ для буферных и высоковольтных оконечных элементов, потому что такой незаряженный конденсатор равноценен короткому замыканию. Устойчивость переключения синхронных устройств зависит от длительности фронтов нарастания и спада тактового импульса, которые должны быть меньше 5 – 15 мкс. При затянутых фронтах КМОП инвертор долгое время находится в активном режиме, через него течет сквозной ток, отчего структура может перегреться и разрушиться.

Дата добавления: 2020-03-17; просмотров: 1640;