Инверторы КМОП с тремя выходными состояниями.

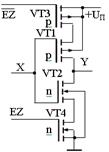

Такой инвертор можно получить, если последовательно с транзисторами логики включить дополнительные ключевые транзисторы VT3, VT4 (рисунок 6.3). С помощью этих транзисторов можно отключать транзисторы ключа VT1 и VT2 от источника питания или от общей шины (земли). При высоком напряжении на входе  транзистор р-типа VT3 заперт и оба транзистора VT1 и VT2 отключены от источника питания. Каналы этих транзисторов оказываются в непроводящем состоянии, а выход – в состоянии Z. При

транзистор р-типа VT3 заперт и оба транзистора VT1 и VT2 отключены от источника питания. Каналы этих транзисторов оказываются в непроводящем состоянии, а выход – в состоянии Z. При  = 0 транзистор VT3 подключает транзисторы логики к источнику питания (на входе EZ должен быть высокий уровень напряжения) и инвертор переходит в обычный режим работы. Управление третьим состоянием можно осуществлять по входу EZ. На входе

= 0 транзистор VT3 подключает транзисторы логики к источнику питания (на входе EZ должен быть высокий уровень напряжения) и инвертор переходит в обычный режим работы. Управление третьим состоянием можно осуществлять по входу EZ. На входе  устанавливается лог.0, при EZ = 1 транзистор VT4 открыт и ключ VT1, VT2 находится в рабочем состоянии. При EZ = 0 транзистор VT4 запирается и выход отключается от земли (переводится в третье состояние).

устанавливается лог.0, при EZ = 1 транзистор VT4 открыт и ключ VT1, VT2 находится в рабочем состоянии. При EZ = 0 транзистор VT4 запирается и выход отключается от земли (переводится в третье состояние).

Рисунок 6.3 – Схема инвертора

КМОП-инверторы с тремя состояниями выхода используются в качестве самостоятельных элементов или в составе некоторых типов логических элементов и более сложных устройств.

6.4 Основные характеристики инвертора

Энергитические характеристики. Одной из основных характеристик КМОП ИС является мощность потребления. Суммарная мощность потребления складывается из статической и динамической. Статическая мощность потребления:

PC = (IC + IУ) UП,

где UП – напряжение питания; IС – сквозной ток транзисторов; IУ – токи утечки обратно смещенных p-n – переходов.

Динамическая составляющая мощности потребления присуща микросхемам при функционировании на рабочей частоте F и определяется тремя факторами: емкостью нагрузки СН, внутренней емкостью схемы СВН. и токами переключения (сквозными токами):

PД = СД U 2П F + Σ (CН U 2П FО),

где СД – средняя эффективная емкость, устанавливаемая для расчета мощности потребления суммарной нагрузки, обусловленной внутренними емкостями и переходными токами переключения, F0 – частота переключения каждого выхода МСХ (частота сигналов на выходе может отличаться от входной для схем отличных от инвертора).

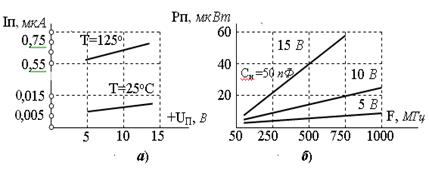

В статическом состоянии один из транзисторов КМОП-структуры, р-или n-МОП, закрыт и теоретически существует непроводящий канал между питанием и «землей». Однако наблюдается тепловое движение неосновных носителей заряда через обратно смещенные переходы, которое создает очень малый ток утечки между шиной питания и «землей». На статический ток потребления оказывают влияние три фактора: температура, сложность схемотехники, напряжение питания (рисунок 6.4, а).

Динамическая составляющая мощности потребления растет с увеличением частоты в основном за счет перезарядки емкости нагрузки. С ростом частоты увеличивается влияние внутренних паразитных емкостей схемы. Токи переключения или сквозные токи возникают в период перехода микросхем из одного логического состояния в другое, когда оба транзистора выходного каскада открыты, т.е. во время нарастания и спада импульса. Среднее значение этих токов растет линейно с увеличением частоты переключения. Типовая зависимость динамической мощности потребления от частоты переключения при разных напряжениях питания и емкости нагрузки СН = 50 пФ для ИС К564ЛЕ5 приведена на рисунке 6.4, б.

Рисунок 6.4 – Типовые зависимости для ИС К564ЛЕ5:

а – статического тока потребления от напряжения питания и температуры; б − динамической мощности потребления от частоты переключения

С увеличением тактовой частоты до предельных значений резко возрастает потребляемая мощность, что приводит к увеличению выделяемого тепла и ухудшению условий эксплуатации. Быстродействие схемы ограничивается временами заряда (разряда) входных емкостей Свх логического элемента, а также временами нарастания (спада) напряжения на емкости нагрузки. Значение емкости одного входного элемента обычно 5-15 пФ. Следовательно, длительность фронта и среза входного импульса ЛЭ: t0,1 = t1,0 = 2,2 Rpk Cвх = 2,2 Rnk Свх,

где. Rpk, Rnk – сопротивления каналов выходных транзисторов типа р и n, которые полагаем равными.

При Rk = 2.5 кОм длительность нарастания и спада будет, примерно 25-75 нс. Длительность фронтов выходного сигнала будет определяться емкостью нагрузки:

t0,1 = t1,0 = 2,2 Rрk Cн = 2,2 Rnk Сн,

Кроме того, временные параметры ИС КМОП характеризуются задержкой распространения сигнала от входа к выходу. При включении, когда входной сигнал приводит к изменению состояния на выходе с 0/1, задержка появления сигнала  . При обратном переключении 1/0 задержка распространения

. При обратном переключении 1/0 задержка распространения  . Задержки

. Задержки  и

и  в общем случае даже для ИС одного типа оказываются различными в виду различия параметров открытых р- и n- канальных транзисторов. При напряжении питания UП = 5 В и СН = 15 пФ задержка распространения у простых инверторов при включении и выключении одинакова и равна примерно 60 нс. При СН = 100 пФ задержка распространения при включении возрастает до 200 нс, а при выключении – 300 нс.

в общем случае даже для ИС одного типа оказываются различными в виду различия параметров открытых р- и n- канальных транзисторов. При напряжении питания UП = 5 В и СН = 15 пФ задержка распространения у простых инверторов при включении и выключении одинакова и равна примерно 60 нс. При СН = 100 пФ задержка распространения при включении возрастает до 200 нс, а при выключении – 300 нс.

Помехоустойчивостьдля высокого уровня сигнала и низкого примерно одинакова и составляет почти 50% от Uп. Пропорциональность сохраняется для напряжений питания 5 – 15 В.

Температурная стабильность ИС КМОП очень высокая - колебания температуры в диапазоне от – 550 до + 1250С весьма слабо влияют на передаточные характеристики. В подобных же условиях пороговое напряжение биполярных приборов может измениться на 40%. Однако, с точки зрения надежности следует ограничивать верхний диапазон температуры + 650С.

Входной токКМОП ИС весьма мал. Основное влияние на входной ток оказывает диодная схема защиты, стоящая на входе ИС. Максимальное значение входного тока для всех интегральных микросхем не превышает 0.05 мкА при температуре t = + 250 С и 1 мкА при t = + 1250 С.

Выходной ток характеризует нагрузочную способность ИС по постоянному току. Ток  представляет собой ток, входящий в ИС при открытом n- канальном и закрытом р-канальном транзисторе выходного каскада.

представляет собой ток, входящий в ИС при открытом n- канальном и закрытом р-канальном транзисторе выходного каскада.  – ток выходящий из ИС при закрытом n-канальном и открытом р-канальном транзисторе выходного каскада. Для раз личных типов ИС токи

– ток выходящий из ИС при закрытом n-канальном и открытом р-канальном транзисторе выходного каскада. Для раз личных типов ИС токи  и

и  могут отличаться в десятки раз из-за сильного различия каналов транзисторов выходного каскада. Для микросхем общего назначения выходные токи I0вых и I1вых не превышают 1 мА. Лишь инверторы с повышенной нагрузочной способностью имеют величину выходных токов несколько мА. Например, ИС 564ЛН2 имеет I0вых = 1,25 мА и I1вых = 8 мА.

могут отличаться в десятки раз из-за сильного различия каналов транзисторов выходного каскада. Для микросхем общего назначения выходные токи I0вых и I1вых не превышают 1 мА. Лишь инверторы с повышенной нагрузочной способностью имеют величину выходных токов несколько мА. Например, ИС 564ЛН2 имеет I0вых = 1,25 мА и I1вых = 8 мА.

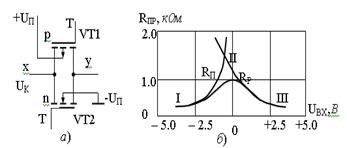

6.5 Тактируемый двунаправленный ключ

Тактируемый двунаправленный ключ состоит из двух МДП-транзисторов с каналами разного типа проводимости. Сток п-канального транзистора соединен с истоком р-канального транзистора и является входом ключа. Сток р-канального транзистора соединен с истоком п-канального транзистора и является выходом (рисунок 6.5). Управляется ключ двумя взаимоинверсными сигналами Ти`Т, которые поступают на затворы транзисторов, причем изменение входных управляющих сигналов допустимо только от – Un до + Un. Питающие напряжения подаются на выводы подложек: + Un для р-канального транзистора, – Un для п-канального. Входное коммутируемое напряжение должно быть положительным относительно подложки n-канального транзистора (т.е. относительно шины питания – Un). Оба транзистора открыты, когда потенциал затвора транзистора n-типа равен или близок к + Un и потенциал затвора транзистора р-типа близок к минус Un. Проводящие каналы обоих транзисторов имеют небольшое сопротивление (100 ¸ 1000 Ом) и обладают двусторонней проводимостью. Двусторонняя проводимость обеспечивается благодаря тому, что МОП-транзисторы сохраняют работоспособность, если стоки и истоки меняются местами. Рисунок 6.5 поясняет нелинейный характер изменения сопротивления ключа в зависимости от напряжения исток-подложка. Рассмотрим три наиболее характерных состояния ключа: Uвх = 0, n‑канальный транзистор открыт, р-канальный закрыт большим напряжением смещения исток-подложка. На рисунке 6.5, б показана зависимость сопротивления ключа от Uвx, это состояние соответствует области I. Un > Uвх > 0, n-канальный транзистор постепенно закрывается возрастающим напряжением смещения исток-подложка, р-канальный при этом открывается.

Оба транзистора при этом частично открыты (область II, рисунок 6.5). Uвх » Un, n-канальный транзистор полностью закрыт, р-канальный транзистор открыт (область III, рисунок 6.5).

а − электрическая принципиальная схема; б − изменение сопротивления ключа в зависимости от напряжения исток-подложка

Рисунок 6.5 – Тактируемый двунаправленный ключ

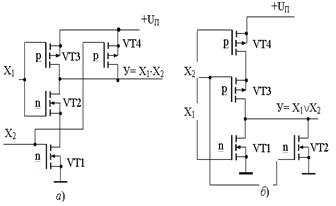

6.6 Логические элементы КМОП типа И-НЕ, ИЛИ-НЕ

Логический элемент И-НЕ. Для построения логического элемента И-НЕ на m входов, требуется последовательное включение m транзисторов n-типа (рисунок 6.6, а) и параллельное включение m транзисторов р-типа (положительная логика).

Открытое состояние схемы (на выходе напряжение низкого уровня) обеспечивается, если на все входы подано напряжение высокого уровня, при этом все n-канальные транзисторы открыты, а р-канальные закрыты. Закрытое состояние схемы (на выходе напряжение высокого уровня) обеспечивается, если хотя бы на один из входов подано напряжение низкого уровня.

При этом один из параллельно соединенных р-канальных транзисторов, соотвествующий данному входу, открыт, а соответствующий ему n-канальный транзистор в последовательной цепи закрыт.

Логический элемент ИЛИ-НЕ. Для построения схемы ИЛИ-НЕ (рисунок 6.6, б) на т входов потребуется последовательное включение т транзисторов р-типа и параллельное включение т транзисторов n-типа. Открытое состояние схемы (на выходе напряжение низкого уровня) обеспечивается, если хотя бы на один из входов подано напряжение низкого уровня. При этом один из n-канальных транзисторов, соответствующий данному входу, открыт, а соответствующий ему один из р-канальных транзисторов в последовательной цепи закрыт.

а − элемент И-НЕ; б – элемент ИЛИ-НЕ

Рисунок 6.6 – Принципиальная электрическая схема ЛЭ

Закрытое состояние схемы (на выходе напряжение высокого уровня) обеспечивается, если на все входы подано напряжение низкого уровня. При этом все р-канальные транзисторы открыты, а все n-канальные закрыты.

6.7 Разновидности простых ЛЭ КМОП

Дата добавления: 2020-03-17; просмотров: 1550;