Логические элементы ИЛИ-НЕ

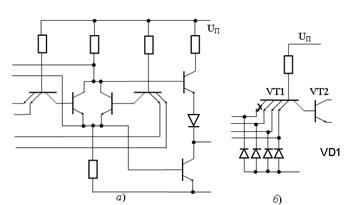

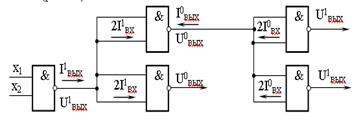

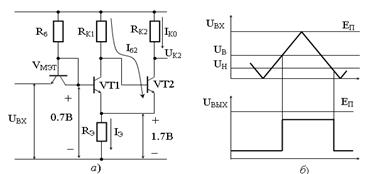

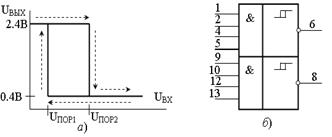

Схемотехнически почти все ЛЭ, входящие в состав серий ТТЛ, могут быть образованы комбинированием двух базовых схем: элемента И-НЕ (рисунок 4.1) и расширителя по ИЛИ (рисунок 4.6, б). Схема логического элемента И-ИЛИ-НЕ (ИЛИ-НЕ) получается путем подключения параллельно ключевому транзистору VT2 дополнительных транзисторов, как показано на рисунке 4.6, а (половина ИС К155ЛР1). В результате имеем логический элемент 2И-2И-2ИЛИ, реализующий функцию y =  . Причем, если входы х1 и х2, а также х3, х4 попарно перемкнуть, то получим двухвходовую схему ИЛИ. Если же на один из входов подать уровень лог.0, то схема реализует двухвходовую схему И-НЕ:

. Причем, если входы х1 и х2, а также х3, х4 попарно перемкнуть, то получим двухвходовую схему ИЛИ. Если же на один из входов подать уровень лог.0, то схема реализует двухвходовую схему И-НЕ:

y =  =

=  .

.

Присоединением логического расширителя по ИЛИ (рисунок 4.6, б) можно расширить функциональные возможности логического элемента. Логический расширитель подключается к выводам К – Э транзистора VT2 основного ЛЭ. Для всех ТТЛ, имеющих возможность расширения по ИЛИ, максимальное число объединений равно восьми. При присоединении одного расширителя задержка распространения схемы увеличивается примерно на 5 нс, а потребляемая мощность – на 5 мВт.

Рисунок 4.6 – Логический элементы:

а − И-ИЛИ-НЕ; б − расширитель по ИЛИ

В составе серий 155, 133 имеются более сложные микросхемы структуры И-ИЛИ-НЕ: ЛР3 – логический элемент 2-2-2-3И – 4ИЛИ-НЕ с возможностью расширения по ИЛИ. Такие микросхемы обладают большой функциональной гибкостью. Кроме того, в составе этих серий имеются логические элементы типа ЛЕ, реализующие логическую функцию ИЛИ-НЕ. Например, К155ЛЕ1 содержит четыре логических элемента 2ИЛИ-НЕ, К155ЛЕ2 - два логических элемента ИЛИ-НЕ со стробированием на одном элементе и возможностью расширения по ИЛИ на другом и другие.

4.3 Логические элементы с открытым коллектором и

тремя состояниями выхода

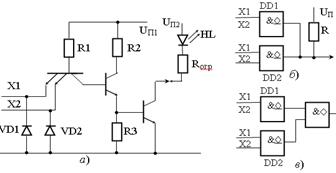

Физические параметры и функциональные возможности ЛЭ существенно зависят от схемы включения выходного каскада. На практике встречается пять основных видов выходных каскадов: со стандартным выходом, с открытым коллектором, с открытым эмиттером, с тремя состояниями выхода и с мощным выходным каскадом на выходе. Стандартные микросхемы имеют два состояния выхода: высокий уровень напряжения на выходе U1вых, когда открыт верхний транзистор и диод, а выходной ток I1вых небольшой (рисунок 4.1). Низкий уровень напряжения U0вых, когда открыт нижний транзистор, который обеспечивает достаточно большой выходной ток I0вых. Работают выходные каскады всегда в противофазе, причем вместо верхнего транзистора и диода может использоваться составной транзистор. ЛЭ со стандартным выходом имеет нагрузочную способность n = 10 (n = 20 для 555 серии, n = 33 для 1531 серии); такой же выходной каскад с повышенной нагрузочной способностью может иметь значения n до 300. Выходы некоторых микросхем выполнены так, что верхний транзистор и относящиеся к нему элементы отсутствуют. В качестве выходного каскада используется транзистор, выход которого не подключен к нагрузке (рисунок 4.7, а).

а − принципиальная схема с внешней нагрузкой; б − «монтажное И»; в − условное графическое изображение; à – открытый коллектор; à – монтажное соединение

Рисунок 4.7 – Логический элемент ТТЛ

Эти транзисторы изготавливаются на разное допустимое напряжение питания: + 5, + 15, + 30, + 35 В и др. Выходы таких ЛЭ подключаются с помощью внешнего резистора и обеспечивают большой ток выхода I0вых (втекающий в коллектор). Поэтому в выходную цепь транзистора можно включить элементы индикации, исполнительные механизмы, электромагнитные реле и т.д.Логические элементы с открытым коллектором допускают параллельное подключение нескольких выходов к общей нагрузке и реализацию с их помощью логических функций, называемых «монтажное ИЛИ» и «монтажное И». Выходное напряжение может принять уровень логической единицы только в том случае, если все выходные транзисторы закрыты:

Эти транзисторы изготавливаются на разное допустимое напряжение питания: + 5, + 15, + 30, + 35 В и др. Выходы таких ЛЭ подключаются с помощью внешнего резистора и обеспечивают большой ток выхода I0вых (втекающий в коллектор). Поэтому в выходную цепь транзистора можно включить элементы индикации, исполнительные механизмы, электромагнитные реле и т.д.Логические элементы с открытым коллектором допускают параллельное подключение нескольких выходов к общей нагрузке и реализацию с их помощью логических функций, называемых «монтажное ИЛИ» и «монтажное И». Выходное напряжение может принять уровень логической единицы только в том случае, если все выходные транзисторы закрыты:

.

.

Если хотя бы на одном выходе будет логический 0, то на выходе всей системы будет низкий потенциал. Для обозначения ЛЭ с открытым коллектором используют ромб с чертой снизу à. Для обозначения псевдоэлемента «монтажное И, ИЛИ» рядом со знаком & или 1 ставится ромбик – à. При использовании ЛЭ в режиме «монтажной логики» каждая МСХ теряет свою самостоятельность.

1. Логические элементы, выходные каскады которых выполнены с открытым эмиттером, отличаются тем, что эмиттер выходного каскада не подключен внутри ИС к общей шине, а оформлен в виде отдельного вывода, а на коллектор подано напряжение источника питания. Такие ЛЭ используются в интерфейсных устройствах (например, 559ИП4, 1102АП2 и др.) и работают как эмиттерные повторители. Они обеспечивают малое выходное сопротивление и большой ток выхода I1вых вытекающий из эмиттера. На условных изображениях схемы с открытым эмиттером обозначаются специальным значком  (ромбик с черточкой сверху).

(ромбик с черточкой сверху).

2. В интерфейсных устройствах используются выходные каскады, представляющие собой изолированные мощные транзисторы, электроды которых (эмиттер, коллектор, база) подключены к внешним выводам ИС. Выходные каскады с изолированными транзисторами используются в логических элементах типа передатчиков (155ЛП7, 1102АП5...) и обеспечивают выходной ток до 300 мА. На условных графических обозначениях ЛЭ с мощным выходом обозначается треугольником (  ).

).

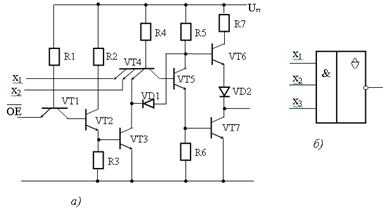

3. Логические элементы с тремя состояниями выхода отличаются от стандартных микросхем тем, что могут переводиться в высокоимпедансное состояние – состояние Z, когда выход отключен от источника питания и от общей шины (рисунок 4.8). ЛЭ имеет встроенную цепь управления, содержащую транзисторы VT1,VT2,VT3, диод VD1 и имеет вход OE (Output Enable – разрешение выхода). При OE равном лог. 0 ЛЭ работает как устройство со стандартным выходом, так как на базе VT2 низкий уровень напряжения, транзистор VT3 и диод VD1 находятся в непроводящем состоянии. При OE равном лог 1 по цепи UП – R1 – БЭVT2 – БЭVT3 протекает ток, транзистор VT3 входит в насыщение и диод VD1 оказывается подключенным к общей шине через транзистор VT3. В результате на коллекторе и базе транзистора VT5 устанавливается низкое напряжение и выходные каскады VT6, VT7 запираются, ток утечки этих транзисторов составляет 20-40 мкА.

а − принципиальная схема; б − условное обозначение

Рисунок 4.8 – Логический элемент с тремя состояниями выхода

Выходы ИС с тремя состояниями можно объединять, что расширяет функциональные возможности MCX. Необходимо лишь обеспечить условие, чтобы в активном состоянии в данный момент находился лишь один выход.

4.4 Разветвление и объединение выходов и входов

логических схем

Для обеспечения работоспособности логических микросхем различных серий друг от друга при условии сохранения параметров MCX, оговоренных в технических условиях на них, следует выполнять требования по уровням выходных напряжений и токов при формирования уровней лог.0 и лог.1, а также по значения суммарной емкостной нагрузки.

Выходные напряжения ЛЭ – источников сигналов в открытом и закрытом состоянии при определенной нагрузке должны соответствовать входным пороговым напряжениям закрытого и открытого состояния ЛЭ – нагрузки с учетом величины напряжения помехи:

где U0вых, U1вых – выходные напряжения ЛЭ в открытом и закрытом состоянии; U0пор, U1пор – порог отпирания и запирания ЛЭ соответственно; U0n, U1n – допустимое напряжение помехи на отпирание и запирание ЛЭ нагрузки.

Уровень помехи, как правило, заранее неизвестен и может быть определен лишь на этапе экспериментального макетирования.Значение суммарных токов всех ЛЭ – нагрузок не должно превышать значений выходных токов MCX – источника в открытом и закрытом состояниях (рисунок 4.9):

Рисунок 4.9 – Разветвление выходов ЛЭ

где I0вых, I1вых – соответственно выходные токи в открытом и закрытом состоянии; I0вх, I1вх – входные токи для одного элемента нагрузки при U0вх, U1вх соответственно; Kраз – число логических входов, подключаемых к выходу MCX – источника.

Суммарная емкость, подключаемая к источнику сигнала, не должна превышать емкость ЛЭ – источника Cн, при которой гарантируются временные параметры, т.е.

где  – максимальная емкость входа ЛЭ (примерно 3пФ);

– максимальная емкость входа ЛЭ (примерно 3пФ);  – емкость монтажных соединений одного входа нагрузки.

– емкость монтажных соединений одного входа нагрузки.

Коэффициент разветвления по выходу определяется следующими выражениями:

K0раз = I0вых / I0вх, н ; K1раз = I1вых / I1вх, н ; Kс = (Сн –См ) / Свх, н ,

где K0раз, K1раз – нагрузочная способность ЛЭ – источника сигнала в открытом состоянии, соответственно; Kс – емкостная нагрузочная способность ЛЭ источника. Наименьший из вычисленных коэффициентов принимается за Kраз для нагружаемой MCX. Если требуется определить допустимое значение единичных нагрузок ИС других серий, расчет ведут аналогичным образом, подставляя значения входных токов I0вх I1вх соответствующей серии. Ниже приводятся таблицы входных и выходных токов различных серий (таблица 4.1). Отметим, что токи I0вых и I1вых в таблице имеют те значения, при которых ТУ гарантируются значения логических уровней U0вых. Превышение выходных токов допустимых значений приводит к изменению U0вых ,U1вых, что в целом снижается помехоустойчивость ИС.

При использовании ИС различных серий в одном устройстве следует учитывать взаимную нагрузочную способность (таблица 4.2). Все серии ИС содержат, кроме элементов со стандартным выходом, элементы с повышенной нагрузочной способностью (буферы). В таблице первое число указывает нагрузочную способность для элемента со стандартным выходом, а второе – для буфера Шоттки.

Таблица 4.1 − Входные и выходные токи ЛЭ различных серий

| Серия | I0вх, мА | I1вх, мА | I0вых, мА | I1вых, мА |

| – 1,6 | 0,04 | – 0,4 | ||

| – 2 | 0,05 | – 1 | ||

| – 0,36 | 0,02 | – 0,4 | ||

| – 0,2 | 0,02 | – 0,4 |

При объединении выходов с открытым коллектором необходимо обеспечить логические уровни выходных напряжений, соответствующие уровням устройств со сложным выходом: U1вых ³ 2,4 В и U0вых £ 0,4 В. Для этого надо рассчитать величину нагрузочного сопротивления Rн при выбранном Uн, обеспечить заданные уровни лог.0 и лог.1 при данной конфигурации схемы и используемых серий ЛЭ.

Таблица 4.2 −Нагрузочную способность ИС различных серий

| Серии ИС | Вход ИС серий | ||||||

| SN | SN 74LS | SN 74S | SN74ALS | SN 74AS | SN 74F | ||

| SN74 | 10/30 | 40/120 | 8/24 | 80/24 | 30/240 | 26/80 | |

| SN 74LS | 5/15 | 20/60 | 4/12 | 40/120 | 40/120 | 13/40 | |

| SN74S | 12/30 | 50/120 | 10/24 | 100/240 | 100/240 | 30/100 | |

| КР | SN74ALS | 5/15 | 20/60 | 4/12 | 40/120 | 40/120 | 13/40 |

| SN 74AS | 12/35 | 50/150 | 10/30 | 100/300 | 100/300 | 30/80 | |

| КР | SN 74F | 12/40 | 50/150 | 10/25 | 100/250 | 100/250 | 30/100 |

При выборе сопротивления нагрузки, следует учитывать, что максимальное быстродействие обеспечивается при минимальном сопротивлении, однако при этом возрастает потребление мощности. При увеличении RH увеличивается время заряда паразитных емкостей.

Триггер Шмитта

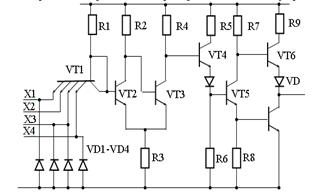

Триггер Шмитта является двухкаскадным усилителем постоянного тока, охваченного положительной обратной связью (через общую эмиттерную цепь RЭ). Название триггера – это дань традиции, поскольку настоящий триггер Шмитта был выполнен на двухкаскадном ламповом триодном усилителе с общим резистором противосвязи в цепи катода. Управление осуществлялось через разделительный конденсатор импульсами разной полярности. Транзисторный вариант триггера Шмитта – несимметричный триггер – реализует ту же схемотехническую идею, с той лишь разницей, что в цепях управления появились значительные токи (базовые) и управление триггером осуществляется потенциальными сигналами. В таком исполнении «триггер Шмитта» является просто двухкаскадным усилителем постоянного тока, имеющим передаточную характеристику со значительным гистерезисом. Поэтому триггер Шмитта не обладает памятью, не может использоваться для обработки и хранения информации, как симметричный триггер. Несимметричные триггеры выпускаются как готовые изделия в сериях интегральных микросхем ТТЛ, ТТЛШ, КМОП. На рисунке 4.10 показана принципиальная схема 155ТЛ1, содержащая в одном корпусе два самостоятельных инвертора 4И-НЕ, обладающих гистерезисной передаточной характеристикой. Каждое устройство содержит несимметричный триггер Шмитта, выполненный на транзисторах VT2, VT3, входную цепь управления на многоэмиттерном транзисторе VT1и выходной формирователь. Транзистор VT4 играет роль эмиттерного повторителя, VT5 – фазорасщепляющий каскад и VT6 – сложный эмиттерный повторитель.

Выявим причину появления гистерезиса в триггерах Шмитта. Для чего ознакомимся с принципом его работы по схеме приведенной на рисунке 4.11, а. При низком входном напряжении (UВХ = 0) на эмиттере VTМЭТ напряжение на его базе не более 0,7 В и транзистор VT1 заперт. Транзистор VT2 открыт, через RЭ протекает эмиттерный ток IЭ2 = Iб2 + IК2, и падение напряжения на нем равняется примерно 1,7 В.

При постепенном повышении входного напряжения до уровня 1,7 В на базе транзистора VT1 напряжение станет равным примерно 2,4 В (UВХ + UБЭМЭТ), этот транзистор откроется и войдет в насыщение. Напряжение UКЭ1 насыщенного транзистора не более 0,4 В, и VT2 закроется. Напряжение на эмиттере уменьшиться в два раза и станет равным 0,9 В, поскольку RК1 = 2RК2 и коллекторный ток IК1 примерно в два раза меньше IК2. Процесс переключения происходит релаксационно, за счет положительной обратной связи, возникающей между транзисторами в момент переключения, когда оба транзистора находятся в активном режиме. Новое состояние (VT1 открыт и насыщен, VT2 заперт) будет сохраняться до тех пор, пока напряжение на входе будет превышать значение UН (рисунок 4.11, б).

Рисунок 4.10 – Микросхема К155ТЛ1 – принципиальная

схема одного триггера

При снижении входного напряжения до уровня UН = 0,8 – 0,9 В транзистор VT1 вновь закроется, а VT2 «скачкообразно» перейдет в насыщенный режим. Напряжение гистерезиса составит величину 0,9 В, что существенно улучшает помехозащищенность схемы. Триггеры Шмитта широко используются для формирования прямоугольных импульсов, имеющих пологие фронты. Широко распространенные серии MCX, как правило, содержат в одном корпусе несколько логических элементов: четыре ЛЭ типа 2И или 2И-НЕ, три ЛЭ типа 3И или 3И-НЕ, два – 4И или 4И-НЕ и один восьмивходовой ЛЭ И-НЕ.

Рисунок 4.11 – Принципиальная схема:

а − триггер Шмитта; б – эпюры напряжений

Выпускаются различные разновидности триггеров Шмитта, например, К555ТЛ1 – это шесть инверторов в одном корпусе (ТШ-НЕ ×6).

Рисунок 4.12 – Передаточная характеристика:

а – ИС К155ТЛ1; б – условное обозначение

4.6 Рекомендации по применению логических элементов ТТЛ

При практической реализации принципиальной схемы возникают ситуации, когда не все входы оказываются задействованы и встает вопрос о том, как правильно распорядиться ими. Неиспользованные ЛЭ рекомендуется включать так, чтобы их выходы имели высокий потенциал, для чего на входы элементов И-НЕ, ИЛИ-НЕ подают уровень лог. 0 (заземляют). При этом уменьшается рассеиваемая мощность, а сами выходы можно использовать в качестве лог. 1 для входов других ЛЭ. Незадействованные входы одного логического элемента используют следующим образом: – объединяют с другими входами ЛЭ, учитывая что при этом возрастает нагрузка на источник сигнала и увеличивается входная емкость; – если на неиспользованном входе должен быть уровень лог. 0, то данный вход можно просто заземлить. Если на неиспользованном входе должен быть уровень лог. 1, то этот вход можно подключить к выходу другого ЛЭ, на котором постоянно установлен высокий уровень 2,4-3,6 В, либо через резистор 1-2 кОм можно подключить к источнику питания до 20 неиспользуемых входов. Формально неиспользуемый вход можно оставить свободным, однако при этом снижается помехоустойчивость ЛЭ, поскольку на него наводятся сигналы помех. Особое внимание следует уделить фильтрации питания по низкой и высокой частоте. Рекомендуется у каждой MCX ставить высокочастотный керамический конденсатор 0,01-0,1 мкФ, а на шину питания электролитический конденсатор емкостью в нескольких десятков мкФ. Микросхемы разных серий непосредственно согласуются между собой по электрическим уровням, однако следует учитывать особенности каждой серии. Микросхемы с повышенным высоким быстродействием имеют малое входное и выходное сопротивление и в моменты переключений создают кратковременные броски тока в цепи питания, которые проявляются в виде помех. Причем у быстродействующих серий крутизна фронтов настолько велика, что вызывает высокочастотные наводки в сигнальных целях. При сопряжении быстродействующих MCX с микросхемами среднего быстродействия (К155, 133, К555, 533) следует учитывать, что последние более восприимчивы к помехам, поскольку имеют более высокие входные и выходные сопротивления. Маломощные ИС с диодами Шоттки особенно чувствительны к наводкам, и их следует отделять от быстродействующих схем. Здесь целесообразно применять раздельное питание и заземление, следует отделять сигнальные шины маломощных MCX от выходных линий быстродействующих. Все входы и выходы, имеющие определенное функциональное назначение, должны обозначаться латинскими буквами, взятыми из английских слов, отражающих данное функциональное назначение. Буквенные обозначения, указанные на левом и правом дополнительных полях, должны быть без инверсий. Инверсные и выходные сигналы обозначаются указателем инверсии (кружок), который указывает, кроме того, активный уровень входных и выходных сигналов, имеющих строго определенное функциональное назначение.

Дата добавления: 2020-03-17; просмотров: 2296;