Глава 9. Цифровые устройства последовательностного типа.

Триггеры.

Цифровое устройство называется последовательностным (ПЦУ), если его выходные сигналы зависят не только от значений входных сигналов в данный момент времени, но и от значений входных сигналов, поступивших в предшествующие моменты времени. Иными словами, ПЦУ должно отслеживать последовательность поступления входных сигналов для формирования результата на своем выходе. Отсюда очевиден термин «последовательностое». В структуре ПЦУ обычно имеется комбинационная схема, и всегда присутствуют элементы, способные удерживать (фиксировать) устойчивые состояния ПЦУ в отсутствии внешних воздействий. Такие элементы обладают как бы эффектом памяти. Поэтому говорят, что ПЦУ обладают памятью. Простейший бинарный элемент памяти может принимать одно из двух состояний – логическую единицу или логический нуль. Это состояние может сохраняться сколь угодно долго до тех пор, пока не будет заменено на новое. ПЦУ называются еще цифровыми автоматами, конечными автоматами или автоматами с памятью. ПЦУ является основой тактируемых устройств, функционирование которых можно разбить на некоторые стадии во времени, поочередно сменяющиеся друг за другом. Такой принцип работы характерен для большинства измерительных цифровых схем. Например, почти все методы аналого-цифрового преобразования требуют реализации последовательных во времени циклических стадий. Совокупность правил, определяющих последовательность переключения состояний и последовательность выходных сигналов в зависимости от последовательности входных сигналов, принято называть законом функционирования ПЦУ.

Роль элемента памяти в ПЦУ выполняет триггер, способный фиксировать и хранить значение логического нуля или единицы. Триггер представляет собой устройство с двумя устойчивыми состояниями. Устойчивым называется состояние, в котором устройство в отсутствии внешних воздействий может прибывать сколько угодно долго. В общем случае триггер имеет два выхода: прямой  и инверсный

и инверсный  . Состояние триггера принято определять по значению потенциала на прямом выходе. В основу классификации триггеров положены два основных признака: функциональный и способ записи информации в триггер.

. Состояние триггера принято определять по значению потенциала на прямом выходе. В основу классификации триггеров положены два основных признака: функциональный и способ записи информации в триггер.

Функциональная классификация является наиболее общей и представляет собой классификацию триггеров по виду логического уравнения, характеризующего состояния входов и выходов триггера в момент времени до его срабатывания tn и после tn+1. В соответствии с функциональной классификацией различают RS-, D-, T- и JK-триггеры.

Классификация по способу записи информации характеризует временную диаграмму работы триггера, т.е. определяет ход процесса записи информации в триггер. По этой классификации триггеры подразделяются на асинхронные и тактируемые. Отличительной особенностью асинхронных триггеров является то, что запись информации в них осуществляется статическим способом, т.е. непосредственно с поступлением информационного сигнала на его вход. Запись информации в тактируемый триггер, имеющий информационные и тактовые входы, осуществляется только при подаче разрешающего или тактирующего импульса. Среди тактируемых триггеров различают триггеры, срабатывающие по уровню (в момент прихода тактирующего сигнала или, что одно и то же, по его переднему фронту), и триггеры с внутренней задержкой, срабатывающие после окончания тактирующего сигнала (по заднему фронту). Такое управление тактируемыми триггерами называется динамическим. Кроме того, тактируемые триггеры подразделяются на однотактные и многотактные в зависимости от числа тактирующих сигналов, необходимых для перевода триггера из одного состояния в другое.

При проектировании устройств с применением триггеров, кроме значения функции, выполняемой триггером, необходимо знать его основные схемотехнические параметры. К таким параметрам относятся как стандартные параметры любой логической микросхемы – это нагрузочная способность, коэффициент объединения по входу, время задержки и т.д., так и индивидуальные:

- минимальная длительность входного сигнала, при которой еще происходит переключение триггера из одного состояния в другое;

- максимальная частота переключения триггера, определяющая минимально допустимый временной интервал между двумя последовательными сигналами минимальной длительности.

Закон функционирования триггера, да и вообще ПЦУ, удобно отображать с помощью так называемых таблиц переходов, в которых даются состояния входов и выходов триггера в момент времени до его срабатывания tn и после tn+1. При этом выходное состояние может обозначаться следующим образом:

0 - триггер находится в состоянии Q=0;

1 - триггер находится в состоянии Q=1;

Q - состояние триггера не изменяется при изменении информации на входе;

- состояние триггера изменяется на противоположное при изменении информации на входе;

- состояние триггера изменяется на противоположное при изменении информации на входе;

Х - неопределенное состояние триггера, характеризующееся тем, что в процессе действия информационного сигнала на входе логические уровни выходов триггера одинаковы (  или

или  ), а после окончания действия информационного сигнала триггер может оказаться в состояние Q=1 или Q=0 с равной вероятностью.

), а после окончания действия информационного сигнала триггер может оказаться в состояние Q=1 или Q=0 с равной вероятностью.

RS-триггер.

Триггером RS-типа называется логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S (от англ. «reset» - сбросить и «set» - установить), такие, что при S=1 и R=0 триггер принимает единичное состояние, а при S=0, R=1 - нулевое. Принцип работы RS-триггера можно задать таблицей переходов (таблица 9.1), где Qn – исходное состояние триггера:

Таблица 9.1.

| tn | tn+1 | |

| Rn | Sn | Qn+1 |

| Qn | ||

| X |

Для того, чтобы найти логическое уравнение RS-триггера, преобразуем таблицу переходов к виду таблицы истинности (таблица 9.2), в которой состояние Qn определим конкретными значениями и представим его в виде входной переменной:

Таблица 9.2.

| tn | tn+1 | ||

| Rn | Sn | Qn | Qn+1 |

| 0 | |||

| X | |||

| X |

На основании данных таблицы заполним диаграмму Вейча, в которой отметим также неопределенные значения функции Qn+1 (рис. 9.1,а). Из диаграммы видно, что в результате склейки минтермов можно получить две простые импликанты  и

и  . Так как функция Qn+1 является частично определенной, то можно доопределить ее неопределенные состояния единичными значениями с целью получения еще более минимального вида логического уровнения (рис. 9.1,б). МДНФ после проделанных действий примет вид, который и будет соответствовать логическому уравнение RS-триггера:

. Так как функция Qn+1 является частично определенной, то можно доопределить ее неопределенные состояния единичными значениями с целью получения еще более минимального вида логического уровнения (рис. 9.1,б). МДНФ после проделанных действий примет вид, который и будет соответствовать логическому уравнение RS-триггера:

.

.

Рис. 9.1. Диаграмма Вейча для МДНФ асинхронного RS-триггера с неопределенными состояниями (а) и с доопределенными состояниями (б).

Полученное уравнение задает работу асинхронного RS-триггера. Состояние такого триггера определяется только значениями сигналов R и S. Асинхронный RS-триггер можно построить на логических элементах И-НЕ, ИЛИ-НЕ. Для реализации триггера на элементах ИЛИ-НЕ выполним следующие преобразования, используя закон де Моргана и двойного отрицаня:

.

.

Схема, реализующая полученную зависимость, представлена на рис.9.2,а. Для реализации RS-триггера на элементах И-НЕ, необходимо выполнить следующие преобразования:

.

.

Схема асинхронного RS-триггера, соответствующая полученному уравнению, изображена на рис. 9.2,б. а условное графическое обозначение – на рис. 9.2,в. Из рисунка видно, что на вход триггера на элементах И-НЕ сигналы R и S необходимо подавать в инверсном виде.

Рис. 9.2. Схемы асинхронного RS-триггера на базе элементов ИЛИ-НЕ (а), И-НЕ (б) и его УГО с инверсными входами (в).

В качестве самостоятельных устройств асинхронные RS-триггеры находят ограниченное применение, но являются базовыми схемами для более сложных триггерных устройств. В устройствах цифровой обработки находят применение тактируемые RS-триггеры, которые называются еще синхронными. Эти триггеры, кроме входов установки R и S, имеют еще вход разрешения записи C. Срабатывание синхронного триггера происходит только при наличии активного сигнала на этом входе. Работа синхронного RS-триггера задается таблицей переходов 9.3:

Таблица 9.3.

| tn | tn+1 | ||

| Cn | Rn | Sn | Qn+1 |

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

| X |

Из таблицы видно, что до тех пор, пока сигнал Cn имеет значение логического нуля, триггер сохраняет свое состояние неизменным. Как только Cn становится равным логической единице, работа синхронного триггера разрешается, и его состояния соответствуют состояниям асинхронного триггера. Алгоритм нахождения МДНФ синхронного RS-триггера аналогичен алгоритму нахождения МДНФ асинхронного RS-триггера. Приведем результат поиска этой МДНФ - диаграмму Вейча для таблицы 9.3 с неопределенными состояниями (рис. 9.3,а) и с доопределенными состояниями (рис. 9.3,б).

Согласно диаграмме рис. 9.3,б запишем МДНФ и выполним следующее преобразование:

.

.

Полученная ФАЛ содержит два слагаемых. Первое слагаемое представляет собой логическою конъюнкцию инверсного значения сигнала тактирования  и состояния выхода триггера Q, а второе – логическую конъюнкцию прямого значения сигнала тактирования С и ФАЛ асинхронного RS-триггера. Эта форма записи логического уравнения синхронного RS-триггера считается общепринятой формализованной записью.

и состояния выхода триггера Q, а второе – логическую конъюнкцию прямого значения сигнала тактирования С и ФАЛ асинхронного RS-триггера. Эта форма записи логического уравнения синхронного RS-триггера считается общепринятой формализованной записью.

Рис. 9.3. Диаграмма Вейча для МДНФ синхронного RS-триггера с неопределенными состояниями (а) и с доопределенными состояниями (б).

Для реализации структурной схемы синхронного RS-триггера на элементах И-НЕ необходимо инверсные сигналы установки  и сброса

и сброса  асинхронного триггера стробировать сигналом разрешения C. Иными словами, на вход схемы асинхронного триггера необходимо подать не просто сигналы

асинхронного триггера стробировать сигналом разрешения C. Иными словами, на вход схемы асинхронного триггера необходимо подать не просто сигналы  и

и  , а их конъюнкцию с сигналом синхронизации C, т.е.

, а их конъюнкцию с сигналом синхронизации C, т.е.  и

и  . Для этого необходимо неинверсные сигналы S и R объединить с сигналом синхронизации C вентилями И-НЕ (рис. 9.4,а). Нужно заметить, что в этом случае сигналы установки и сброса, подаваемые на вход всей схемы, будут прямыми.

. Для этого необходимо неинверсные сигналы S и R объединить с сигналом синхронизации C вентилями И-НЕ (рис. 9.4,а). Нужно заметить, что в этом случае сигналы установки и сброса, подаваемые на вход всей схемы, будут прямыми.

Аналогично для реализации структурной схемы синхронного RS-триггера на элементах ИЛИ-НЕ необходимо прямые сигналы установки S и сброса R асинхронного триггера стробировать сигналом разрешения C, т.е. получить комбинацию сигналов  и

и  . Для этого выполним преобразования:

. Для этого выполним преобразования:

,

,

.

.

Из уравнений видно, что на вход схемы синхронного RS-триггера на элементах ИЛИ-НЕ все входные сигналы нужно подавать в инверсном виде. Схема такой реализации представлена на рис.9.4,б.

Рис. 9.4. Схема синхронного RS-триггера в базисе И-НЕ (а) и ИЛИ-НЕ (б).

Часто синхронные триггеры любых типов имеют дополнительные входы асинхронной установки в ноль или единицу. Схема такого синхронного RS-триггера приведена на рис. 9.5,а, а его условное графическое обозначение на рис. 9.5,б. Поскольку триггер, изображенный на структурной схеме, реализован на элементах И-НЕ, то сигналы асинхронной установки R и S должны иметь инверсные активные уровни. Кроме того, поскольку сигналы асинхронной установки подаются непосредственно на выходной каскад (асинхронный RS-триггер), то они имеют больший приоритет перед остальными сигналами триггера.

Рис. 9.5. Схема синхронного RS-триггера с входами асинхронной установки (а) и его условное графическое обозначение (б).

D-триггер.

D-триггер представляет собой синхронный запоминающий бинарный элемент с одним информационным входом D и входом синхронизации C. D-триггер осуществляет запись информационного разряда по активному уровню сигнала C с последующим его хранением. Отсюда D-триггер имеет другие названия: триггер-защелка (data-триггер) и триггер задержки (delay-триггер), что объясняет происхождение символа «D» в его названии. Работа D-триггера задается таблицей переходов 9.4:

Таблица 9.4.

| tn | tn+1 | |

| Cn | Dn | Qn+1 |

| Qn | ||

| Qn | ||

Проделав операции, как и в случае с RS-триггером, можно составить логическое уравнение D-триггера, соответствующее приведенной таблице переходов:

.

.

Если RS-триггер относится к классу парафазных триггеров (для установки его в ноль или единицу необходимо подавать на входы R и S сигналы с противоположными значениями), то D-триггер является однофазным триггером. Из этого следует, что D-триггер можно реализовать на базе синхронного RS-триггера, задействовав вход S как вход D, а на вход R подав сигнал D через инвертор (рис.9.6,а). Можно реализовать D-триггер на базе RS-триггера и без дополнительного инвертора, несколько изменив связи в его внутренней структуре. Для этого выполним следующие преобразования над логическим уравнением D-триггера:

.

.

Полученное уравнение совпадает по своей структуре с уравнением для асинхронного RS-триггера, при условии, что  , а

, а  . Тогда очевидно, что D-триггер можно реализовать на базе RS-триггера, на информационные входы которого необходимо подавать сигналы в соответствии с полученными выражениями. Поскольку сигналы R и S на вход асинхронного RS-триггера на базе элементов И-НЕ должны подаваться в инверсном виде, то для получения D-триггера на входы RS-триггера необходимо подавать

. Тогда очевидно, что D-триггер можно реализовать на базе RS-триггера, на информационные входы которого необходимо подавать сигналы в соответствии с полученными выражениями. Поскольку сигналы R и S на вход асинхронного RS-триггера на базе элементов И-НЕ должны подаваться в инверсном виде, то для получения D-триггера на входы RS-триггера необходимо подавать  и

и  . Преобразуем выражение для

. Преобразуем выражение для  к виду:

к виду:

.

.

С учетом полученных выражений, схема D-триггера может быть представлена совокупностью двух каскадов (рис. 9.6,б). Первый выполняет функцию формирование сигналов  и

и  , а второй – асинхронного RS-триггера. На рис. 9.6,в показано условное графическое обозначение D-триггера.

, а второй – асинхронного RS-триггера. На рис. 9.6,в показано условное графическое обозначение D-триггера.

Рис. 9.6. Схема D-триггера на основе синхронного RS-триггера с внешним инвертором (а), на основе структуры RS-триггера без внешнего инвертора (б), условное графическое обозначение D-триггера (в).

Рассмотренные ранее способы подачи входных сигналов характеризуются тем, что их активными уровнями являются статические состояния, т.е. сами уровни напряжения логического нуля или логической единицы. Такая форма управления цифровым устройством называется статической. Для тактируемых устройств эта форма управления в большинстве случаев является неудобной, поскольку в течение всего времени действия импульса сигнала синхронизации, устройство будет реагировать на любые изменения входных информационных сигналов. Таким образом, необходимо, чтобы информационные сигналы оставались неизменными на протяжении действия импульса синхронизации. Это значительно усложняет схему устройства, а в некоторых случаях и вовсе является не решаемой задачей, поскольку информационные сигналы могут носить характер последовательностей импульсов со случайным характером. Для устранения указанного недостатка используется принцип динамического управления. Согласно этому принципу, активным считается не статический уровень напряжения логической единицы или логического нуля, а процесс перехода из одного уровня в другой. Этот процесс представляет собой передний или задний фронт тактирующего импульса и, следовательно, характеризуется малым временным промежутком. Поэтому задача синхронизации значительно упрощается и представляет собой фиксацию входных информационных сигналов в строго определенный момент подачи или снятия импульса синхронизации. На рис. 9.7 на примере D-триггера показана организация динамического управления входом записи C по схеме трех триггеров.

Рис. 9.7. Схема D-триггера с динамическим управлением.

Хранение информации в схеме на рис.9.7 осуществяет каскадом асинхронного RS-триггера на вентилях И-НЕ D5 и D6, имеющего инверсные входы установки и сброса. Два других каскада триггеров на вентилях D1, D2, D3 и D4 реализуют механизм динамического управления и коммутации информационного сигнала D и сигнала записи (синхронизации) C. Элемент D4 формирует инверсное значение сигнала  , которое подается на входы элементов D1 и D3. На выходе элемента D1 формируется прямое значение сигнала D. Если считать, что на входе D присутствует единица, то в момент подачи единицы на вход C, на входе

, которое подается на входы элементов D1 и D3. На выходе элемента D1 формируется прямое значение сигнала D. Если считать, что на входе D присутствует единица, то в момент подачи единицы на вход C, на входе  основного триггера сформируется ноль, а на

основного триггера сформируется ноль, а на  - единица. Весь триггер, таким образом, будет установлен в единичное состояние. Поскольку на верхнем входе элемента D3 будет присутствовать ноль (значение сигнала

- единица. Весь триггер, таким образом, будет установлен в единичное состояние. Поскольку на верхнем входе элемента D3 будет присутствовать ноль (значение сигнала  ), то этот элемент заблокирует схему, и она не будет реагировать на изменение сигнала на входе D. При наличии на входе D нуля и подачи на вход C единицы включается элемент D3 и сбрасывает основной триггер в ноль. Если теперь, во время действия единичного уровня сигнала на входе C, на вход D поступит единица, то удерживаемый на линии

), то этот элемент заблокирует схему, и она не будет реагировать на изменение сигнала на входе D. При наличии на входе D нуля и подачи на вход C единицы включается элемент D3 и сбрасывает основной триггер в ноль. Если теперь, во время действия единичного уровня сигнала на входе C, на вход D поступит единица, то удерживаемый на линии  нулевой уровень (верхний вход элемента D4) не даст схеме изменить свое состояние. Таким образом, в изображенной на рисунке схеме, реакция на входной информационный сигнал D будет происходить только по переднему фронту импульса C. Данный триггер будет иметь прямое динамическое управление. На рис.9.8 показано обозначение входов с динамическим управлением на УГО элементов на примере входа синхронизации C.

нулевой уровень (верхний вход элемента D4) не даст схеме изменить свое состояние. Таким образом, в изображенной на рисунке схеме, реакция на входной информационный сигнал D будет происходить только по переднему фронту импульса C. Данный триггер будет иметь прямое динамическое управление. На рис.9.8 показано обозначение входов с динамическим управлением на УГО элементов на примере входа синхронизации C.

Рис. 9.8. Обозначения входов с динамическим управлением на УГО элементов.

T-триггер.

Асинхронный триггер T-типа является одновходовым устройством с двумя устойчивыми состояниями, изменяющимися каждый раз на противоположные при подаче на вход Т управляющего сигнала. Работа асинхронного Т-триггера задается таблицей переходов 9.5:

Таблица 9.5.

| tn | tn+1 |

| Tn | Qn+1 |

| Qn | |

|

Составленное по таблице переходов СДНФ для Qn+1 уже имеет минимальный вид:

.

.

Характерной особенностью T-триггера является то, что частота изменения потенциала на его выходах в два раза меньше частоты сигналов на входе T (рис. 9.9). Это свойство используется при построении двоичных счетчиков. Отсюда второе название T-триггера – счетный триггер. Вход Т принято называть счетным.

Рис. 9.9. Диаграммы входного и выходного потенциалов T-триггера.

Структуру асинхронного T-триггера можно определить путем преобразования его логической функции к удобному виду для синтеза в заданном базисе. Однако, из анализа работы асинхронного RS-триггера очевидно, что в том случае, если он находился в единичном состоянии (  и

и  ), то для сброса его в нулевое состояние необходимо сигнал с прямого выхода Q подать на вход сброса R, а с инверсного выхода

), то для сброса его в нулевое состояние необходимо сигнал с прямого выхода Q подать на вход сброса R, а с инверсного выхода  - на вход установки S. Если же RS-триггер изначально находился в нулевом состоянии (

- на вход установки S. Если же RS-триггер изначально находился в нулевом состоянии (  и

и  ), то для приведения его в единичное состояние необходимо сигнал с инверсного выхода

), то для приведения его в единичное состояние необходимо сигнал с инверсного выхода  подать на вход установки S, а с прямого выхода Q - на вход сброса R. Достигается это путем введения обратных связей (рис. 9.10,а). При этом роль входа Т будет выполнять вход разрешения C синхронного RS-триггера.

подать на вход установки S, а с прямого выхода Q - на вход сброса R. Достигается это путем введения обратных связей (рис. 9.10,а). При этом роль входа Т будет выполнять вход разрешения C синхронного RS-триггера.

Рис.9.10. Схема одноступенчатого асинхронного T-триггера на основе RS-триггера (а) и D-триггера (б)

Т-триггер можно построить и на базе D-триггера. Если в логическом уравнении синхронного D-триггера принять  , тогда уравнение запишется в виде:

, тогда уравнение запишется в виде:

.

.

Полученное выражение является ни чем иным, как логическим уравнением T-триггера при условии, что функцию входа T выполняет вход разрешения C D-триггера. При этом, на вход D необходимо подавать сигнал с инверсного выхода  (рис.9.10,б).

(рис.9.10,б).

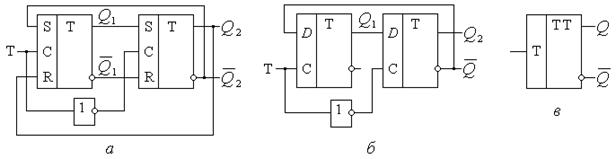

Рассмотренные на рис.9.10 структуры Т-триггера являются практически неработоспособными. Действительно, в течение всего времени, пока на входе T присутствует активный уровень сигнала, будет происходить непрерывная смена его состояний на противоположные с частотой, равной обратной величине удвоенного времени срабатывания триггера. В результате возникнет автоколебательный процесс. Триггер будет постоянно перебрасывать сам себя в период действия активно сигнала на входе T. Причина этого явления объясняется тем, что Т-триггер, обладая обратными связями, принимает информацию как из внешней среды, так и со своих собственных выходов. Поэтому для устойчивой работы Т-триггера необходимо разделить во времени функции приема тактирующего сигнала Т и фиксации на входах R, S или D сигналов с соответствующих выходов Q и  . Для этого в структуру Т-триггера вводится дополнительный второй запоминающий элемент на базе RS- или D-триггера. На синхронизирующий вход этого элемента тактовый сигнал подается в инверсном виде по отношению к тактовому сигналу первого запоминающего элемента. Подобная организация структур триггерных устройств называется двухступенчатой. Пример двухступенчатого Т-триггера на базе двух синхронных RS-триггеров приведен на рис. 9.11,а, а на основе двух D-триггеров – на рис. 9.11,б. Из рисунка видно, что когда на синхронизирующем входе первого триггера в двухступенчатой структуре действует нулевой уровень тактирующего сигнала Т, он хранит свое состояние Q1 и

. Для этого в структуру Т-триггера вводится дополнительный второй запоминающий элемент на базе RS- или D-триггера. На синхронизирующий вход этого элемента тактовый сигнал подается в инверсном виде по отношению к тактовому сигналу первого запоминающего элемента. Подобная организация структур триггерных устройств называется двухступенчатой. Пример двухступенчатого Т-триггера на базе двух синхронных RS-триггеров приведен на рис. 9.11,а, а на основе двух D-триггеров – на рис. 9.11,б. Из рисунка видно, что когда на синхронизирующем входе первого триггера в двухступенчатой структуре действует нулевой уровень тактирующего сигнала Т, он хранит свое состояние Q1 и  . В это время на синхронизирующий вход второго триггера поступает инвертированный сигнал Т, т.е. имеющий уровень логической единицы. В результате второй триггер принимает состояние первого, т.е. Q1=Q2 и

. В это время на синхронизирующий вход второго триггера поступает инвертированный сигнал Т, т.е. имеющий уровень логической единицы. В результате второй триггер принимает состояние первого, т.е. Q1=Q2 и  =

=  . Запись в первый триггер при этом запрещена. Как только тактирующий сигнал Т примет уровень логической единицы, произойдет запись информации из второго триггера в первый. В результате состояние первого триггера изменится на противоположное. При этом запись во второй триггер производиться не будет, поскольку на его входе будет действовать нулевой уровень сигнала разрешения записи. Процесс будет повторяться с приходом каждого тактирующего импульса, что обеспечит устойчивую работу устройства. В условных графических обозначениях всех двухступенчатых триггеров принято в обозначении триггерной функции элемента указывать два символа «ТТ», как это показано на примере УГО двухступенчатого Т-триггера (рис. 9.11,в).

. Запись в первый триггер при этом запрещена. Как только тактирующий сигнал Т примет уровень логической единицы, произойдет запись информации из второго триггера в первый. В результате состояние первого триггера изменится на противоположное. При этом запись во второй триггер производиться не будет, поскольку на его входе будет действовать нулевой уровень сигнала разрешения записи. Процесс будет повторяться с приходом каждого тактирующего импульса, что обеспечит устойчивую работу устройства. В условных графических обозначениях всех двухступенчатых триггеров принято в обозначении триггерной функции элемента указывать два символа «ТТ», как это показано на примере УГО двухступенчатого Т-триггера (рис. 9.11,в).

Рис. 9.11. Двухступенчатый T-триггер на базе синхронных RS-триггеров (а), D-триггеров (б) и его условное графическое обозначение (в).

JK-триггер.

JK-триггер относится к двухвходовым устройствам и функционирует по правилам, похожим на правила функционирования RS-триггера. Отличие состоит в том, что в JK-триггере все состояния являются определенными. Можно провести аналогию входов JK- и RS-триггеров: вход K (от англ. «kill» – убить) JK-триггера выполняет функцию входа сброса R RS-триггера, а вход J (от англ. «jump» – прыгнуть) JK-триггера – функцию входа установки S RS-триггера. При этом, если в RS-триггере комбинация единичных значений входов R и S является запрещенной, то в случае аналогичной комбинации входов J и K, JK-триггер меняет свое состояние на противоположное. Правило работы синхронного JK-триггера можно сформулировать таблицей переходов 9.6:

Таблица 9.6.

| tn | tn+1 | ||

| Cn | Kn | Jn | Qn+1 |

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

|

Соответствующее таблице логическое выражение имеет вид:

.

.

Поскольку при подаче единицы на входы J- и K триггер инвертирует свое состояние, т.е. выполняет функцию Т-триггера, то логично предположить, что структура синхронного JK-триггера должна повторять структуру T-триггера, т.е. она должна быть двухступенчатой. В принципе схема JK-триггера будет отличаться от схемы T-триггера только тем, что входные стробирующие вентили, входящие в состав RS-триггера первой ступени, должны содержать дополнительные выводы для синхронизируемых входов J и K. Т.е. входной каскад формирования стробированных сигналов  и

и  должен строиться на трехвходовых вентилях И-НЕ (рис.9.12,а). В остальном схема JK-триггера подобна схеме T-триггера на базе синхронных RS-триггеров и работает по точно такому же принципу. Также в этой схеме показаны инверсные входы асинхронной установки

должен строиться на трехвходовых вентилях И-НЕ (рис.9.12,а). В остальном схема JK-триггера подобна схеме T-триггера на базе синхронных RS-триггеров и работает по точно такому же принципу. Также в этой схеме показаны инверсные входы асинхронной установки  и сброса

и сброса  , дополняющие каскад выходного асинхронного RS-триггера второй ступени. Условное графическое обозначение синхронного двухступенчатого JK-триггера с входами асинхронной установки приведено на рис. 9.12,б.

, дополняющие каскад выходного асинхронного RS-триггера второй ступени. Условное графическое обозначение синхронного двухступенчатого JK-триггера с входами асинхронной установки приведено на рис. 9.12,б.

Рис. 9.12. Структура синхронного JK-триггера с входами асинхронной установки (а) и его условное графическое обозначение (б).

Триггер JK-типа относится к разряду универсальных, поскольку на его основе можно получить схемы, выполняющие функции RS-, D- и T-триггеров. Поскольку правила функционирования JK-триггера не нарушают правил функционирования RS-триггера, а только дополняют его неопределенное состояние конкретным, то для реализации функций RS-триггера JK-триггер можно использовать без каких либо изменений. Достаточно сигнал S подать на вход J, а сигнал R – на вход K (рис. 9.13,а). Для реализации на базе JK-триггера функций D-триггера необходимо избавиться от свойства парафазности JK-триггера, установив дополнительный инвертор, формирующий инверсное значение сигнала  для подачи его на вход K (рис. 9.13,б). Для получения T-триггера достаточно объединить входы J и K, подав на них постоянный уровень логической единицы и задав, таким образом, режим, когда JK-триггер будет инвертировать свое состояние. Само же инвертирование будет происходить лишь при поступлении на вход C разрешающих импульсов. Вход C будет выполнять функции счетного входа T (рис. 9.13,в). Кроме того, существуют микросхемы синхронных T-триггеров, которые формируются из JK-триггеров, объединенные входы J и K которых используются как вход Т, а вход синхронизации С - как самостоятельный дополнительный синхронизирующий вход (рис9.13,г).

для подачи его на вход K (рис. 9.13,б). Для получения T-триггера достаточно объединить входы J и K, подав на них постоянный уровень логической единицы и задав, таким образом, режим, когда JK-триггер будет инвертировать свое состояние. Само же инвертирование будет происходить лишь при поступлении на вход C разрешающих импульсов. Вход C будет выполнять функции счетного входа T (рис. 9.13,в). Кроме того, существуют микросхемы синхронных T-триггеров, которые формируются из JK-триггеров, объединенные входы J и K которых используются как вход Т, а вход синхронизации С - как самостоятельный дополнительный синхронизирующий вход (рис9.13,г).

Рис. 9.13. Реализация на базе синхронного JK-триггера функций синхронного RS-триггера (а), D-триггера (б), асинхронного T-триггера (в) и синхронного T-триггера (г).

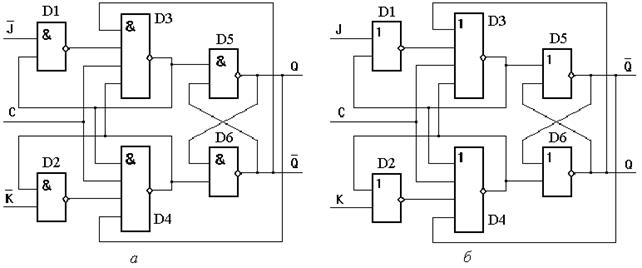

Также как и в случае D-триггера, в JK- и T-триггерах часто вход синхронизации C реализуется по принципу динамического управления. Пример построения схемы синхронного JK-триггера с динамическим управлением на основе элементов И-НЕ приведен на рис.9.14,а, а на основе элементов ИЛИ-НЕ – на рис.9.14,б. Обе схемы идентичны и построены по принципу трех триггеров, как и схема рис.9.7. Хранение записаной информации осуществляется асинхронным RS-триггером на вентилях D5 и D6, а коммутация входных сигналов и динамическое управление - триггерами на вентилях D1, D2, D3 и D4. В первой схеме срабатывание триггера будет осуществляться по переднему фронту сигнала С, а на второй – по заднему.

Рис.9.14. Схема синхронного JK-триггера с динамическим управлением на элементах И-НЕ (а) и ИЛИ-НЕ (б).

В маркировке микросхем для обозначения функции RS-триггера используют комбинацию символов «ТР», функции D-триггера - комбинацию символов «ТМ» и функции JK-триггера – комбинацию символов «ТВ». Микросхемы триггеров T-типа встречаются редко, поскольку они легко получаются из JK-триггеров.

Счетчики.

Счетчики представляют собой последовательностые цифровые устройства и предназначены для выполнения операций счета и хранения кода числа подсчитанных импульсов. Счетчики занимают важное место в качестве элементой базы цифровой измерительной аппаратуры, поскольку на их основе строятся делители частоты, счетные и интегрирующие аналого-цифровые преобразователи, частотомеры, фазометры и прочие устройства. Существуют различные схемы счетчиков, отличающихся назначением, типом используемых триггеров, организацией связи между ними, порядком смены состояний. По порядку изменения состояний счетчики бывают с естественным и произвольным порядком счета. В первых значение кода каждого последующего состояния счетчика отличается на единицу от кода предыдущего состояния. В счетчиках с произвольным порядком счета значения кодов соседних состояний могут отличаться более чем на единицу. Счетчики также подразделяются на простые и реверсивные. Простые счетчики делятся на суммирующие и вычитающие. В суммирующих счетчиках код последующего состояния имеет большее значение, чем код предыдущего состояния, а в вычитающих – меньшее значение. Реверсивные счетчики могут работать как в режиме суммирования, так и в режиме вычитания.

Основными параметрами счетчика являются:

- модуль счета или коэффициент пересчета Ксч;

- быстродействие счетчика.

Модуль счета Ксч характеризует число устойчивых состояний счетчика, т.е. предельное число импульсов, которое может быть им сосчитано. После поступления Ксч входных импульсов счетчик возвращается в исходное состояние. Такие счетчики называются также делителями на число, равное Ксч.. По модулю счета счетчики подразделяются на двоичные, у которых  , и недвоичные, у которых

, и недвоичные, у которых  , где m – положительное целое число.

, где m – положительное целое число.

Быстродействие счетчика в свою очередь определяется двумя величинами:

- разрешающей способностью  , т.е. минимальным допустимым интервалом времени между подачей двух входных импульсов, при котором не происходит потеря счета;

, т.е. минимальным допустимым интервалом времени между подачей двух входных импульсов, при котором не происходит потеря счета;

- временем установки tуст кода счетчика, т.е. интервалом времени между моментом поступления входного сигнала и моментом завершения перехода счетчика в новое устойчивое состояние.

Поскольку счетчики представляют собой класс ПЦУ, то и синтез их целесообразно выполнять на основе базовых элементов ПЦУ, т.е. триггерах. Количество триггеров для двоичных счетчиков определяется формулой:

.

.

Для недвоичных счетчиков количество триггеров следует выбирать из условия:

,

,

где  - двоичный логарифм заданного коэффициента пересчета, округленный до ближайшего (большего) целого числа.

- двоичный логарифм заданного коэффициента пересчета, округленный до ближайшего (большего) целого числа.

Двоичные счетчики.

Наиболее удобным базовым элементом для построения счетчиков является счетный триггер Т-типа. Такой триггер по сути является простейшим счетчиком с  . Соединив несколько Т-триггеров определенным образом в последовательную структуру, можно получить схему многоразрядного счетчика. Если в качестве базовых используются Т-триггеры с прямым динамическим счетным входом, то для построения трехразрядного суммирующего двоичного счетчика их необходимо объединить так, как это показано на рис. 9.15,а. Поскольку срабатывание всех триггеров с прямым динамическим счетным входом происходит по переднему фронту счетного импульса, то для реализации операции суммирования необходимо на триггеры Т2 и Т3 информацию подавать с инверсных выходов

. Соединив несколько Т-триггеров определенным образом в последовательную структуру, можно получить схему многоразрядного счетчика. Если в качестве базовых используются Т-триггеры с прямым динамическим счетным входом, то для построения трехразрядного суммирующего двоичного счетчика их необходимо объединить так, как это показано на рис. 9.15,а. Поскольку срабатывание всех триггеров с прямым динамическим счетным входом происходит по переднему фронту счетного импульса, то для реализации операции суммирования необходимо на триггеры Т2 и Т3 информацию подавать с инверсных выходов  предыдущих триггеров. Временная диаграмма работы триггеров в такой счетной схеме показана на рис.9.15,б (крестиком на импульсах показано срабатывание по переднему фронту). Состояния выходов Q1, Q2 и Q3 сгруппируем в зависимости от номера счетного импульса в таблице 9.7. Из рисунка и таблицы очевидно, что двоичный код, задаваемый логическими состояниями выходов счетчика соответствует порядковому номеру входного счетного импульса С. Пр

предыдущих триггеров. Временная диаграмма работы триггеров в такой счетной схеме показана на рис.9.15,б (крестиком на импульсах показано срабатывание по переднему фронту). Состояния выходов Q1, Q2 и Q3 сгруппируем в зависимости от номера счетного импульса в таблице 9.7. Из рисунка и таблицы очевидно, что двоичный код, задаваемый логическими состояниями выходов счетчика соответствует порядковому номеру входного счетного импульса С. Пр

Дата добавления: 2022-02-05; просмотров: 637;