Недвоичные счетчики.

Как было сказано раньше, недвоичные счетчики имеют модуль счета  , где m – положительное целое число, равное разрядности выходного кода счетчика. Принцип их построения заключается в исключении некоторых избыточных состояний обычного двоичного счетчика. Избыточные состояния исключаются обычно двумя способами. Первый способ характеризуется введением обратных связей с выходов триггеров только определенных разрядов на входы обнуления триггеров всех разрядов. В результате этого счетчик возвращается в нулевое исходное состояние с приходом счетного импульса с номером, меньшим чем 2m. Второй способ характеризуется предварительной записью в триггеры счетчика определенного числа, такого, что исходное состояние счетчика является не нулевым, а иным, равным значению этого числа. В любом случае, для реализации недвоичного счетчика потребуется количество триггеров

, где m – положительное целое число, равное разрядности выходного кода счетчика. Принцип их построения заключается в исключении некоторых избыточных состояний обычного двоичного счетчика. Избыточные состояния исключаются обычно двумя способами. Первый способ характеризуется введением обратных связей с выходов триггеров только определенных разрядов на входы обнуления триггеров всех разрядов. В результате этого счетчик возвращается в нулевое исходное состояние с приходом счетного импульса с номером, меньшим чем 2m. Второй способ характеризуется предварительной записью в триггеры счетчика определенного числа, такого, что исходное состояние счетчика является не нулевым, а иным, равным значению этого числа. В любом случае, для реализации недвоичного счетчика потребуется количество триггеров  , округленное до большего целого значения

, округленное до большего целого значения  .

.

Наибольший интерес среди недвоичных счетчиков представляют двоично-десятичные счетчики с Ксч=10, которые строятся на основе четырех счетных триггеров. Важность этого класса счетчиков заключается в том, что с их помощью легко может быть осуществлен вывод содержимого счетчика в десятичном коде. Действительно каждый двоично-десятичный счетчик имеет десять устойчивых состояний и соответствует одному разряду десятичной системы счисления. Пример организации схемы асинхронного двоично-десятичного суммирующего счетчика показан на рис.9.22. Для того, чтобы счетчик имел модуль счета Ксч=10, необходимо его обнулить десятым счетным импульсом, т.е. из выходного кода 10102 сформировать обратную связь, обнуляющую все триггеры счетчика. Такой сигнал обратной связи будет сформирован схемой совпадения единиц (вентилем И) второго и четвертого разрядов. Этот же сигнал будет являться сигналом переноса P в счетчик следующей старшей десятичной декады при построении многорязрядного двоично-десятичного счетчика. Вентиль ИЛИ в схема используется для пропускания на триггеры как сигнала сброса по обратной связи, так и внешнего сигнала сброса R.

Рис.9.22. Схема асинхронного двоично-десятичного суммирующего счетчика.

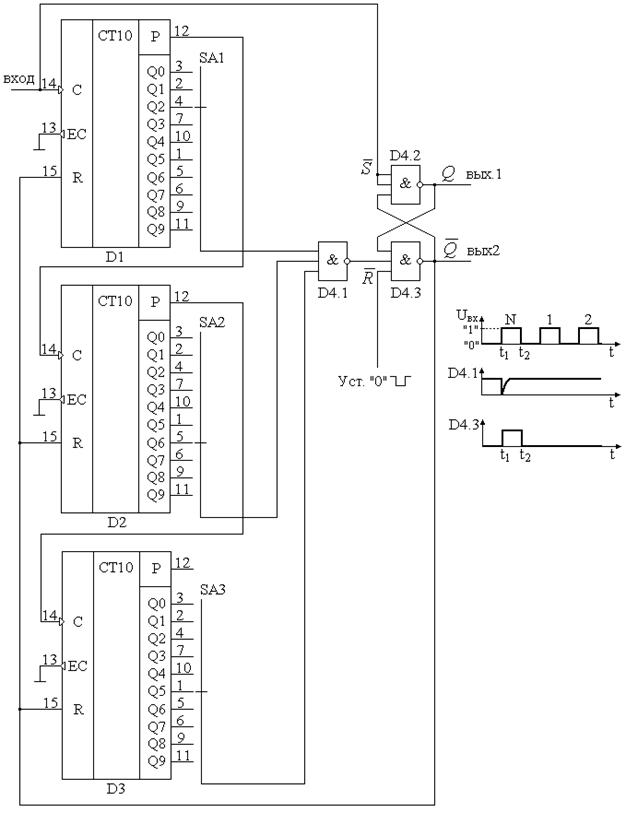

Аналогично рис.9.22 можно строить счетчики с любым модулем счета как суммирующие, так и вычитающие, как синхронные, так и асинхронные. В условном графическом обозначении функция двоичного счетчика определяется символами «СТ» или «СТ2». В случае если счетчик не двоичный, то его модуль счета в УГО определяется соответствующей цифрой рядом с обозначением «СТ». В маркировке микросхем счетчики кодируются символами «ИЕ». Существуют микросхемы счетчиков, в которых интегрирован выходной дешифратор. В таких счетчиках выходной код будет унитарным. Двоично-десятичный счетчик с внутренним дешифратором называется десятичным. В качестве примера можно привести микросхему ИЕ8 десятичного счетчика КМОП-серии (напрмер, К176ИЕ8 и К561ИЕ8). Интересно использование данной микросхемы в схеме делителя частоты с переключаемым коэффициентом деления (рис.9.23). Сама микросхема работает следующим образом. При подаче сигнала высокого уровня на вход сброса R высокий потенциал устанавливается на выходе Q0 и на выходе переноса Р, на остальных выходах устанавливаются логические нули. Работа счетчика осуществляется положительными перепадами на входе С. В этом случае, вход ЕС является входом разрешения счета, и счет будет осуществляться при подаче на него логического нуля. При подаче на вход ЕС логической единицы счет прекращается, и состояние счетчика сохраняется. Можно подавать счетные импульсы и на вход ЕС. В этом случае вход С становится входом разрешения счета. Счет будет производиться при логической единице на входе С по отрицательным перепадам на входе ЕС. По мере счета логическая единица последовательно перемещается по выходам от выхода Q0 до Q9, после чего снова на выход Q0 и весь цикл повторяется. На выходе переноса Р низкий уровень появляется в момент, когда логическая единица появляется на выходе Q5. Снова логическая единица на выходе переноса Р появляется в момент появления логической единице на выходе Q0. Выход переноса Р используется для наращивания разрядности путем последовательного соединения счетчиков друг с другом.

Рис.9.23. Схема делителя частоты с переключаемым коэффициентом деления и временная диаграмма работы триггера.

Переключателем SA1 в схеме устанавливают единицы необходимого коэффициента деления, переключателем SA2 – десятки и переключателем SA3 – сотни. Когда микросхемы устанавливаются в состояния, набранные на переключателях, на выходе элемента D4.1 появляется логический ноль. До этого момента асинхронный RS-триггер на элементах И-НЕ D4.2 и D4.3 счетными импульсами, подаваемыми на вход  с входа всего делителя, установился в единичное состояние, т.е. на выходе 1 (выходе Q) была сформирована логическая единица, а на выходе 2 (выходе

с входа всего делителя, установился в единичное состояние, т.е. на выходе 1 (выходе Q) была сформирована логическая единица, а на выходе 2 (выходе  ) – логический ноль. В момент времени t1 равенства кода подсчитанных импульсов установленному коду переключателями SA, триггер сигналом сброса с элемента D4.1 переходит в состояние, когда на выходе 1 формируется логический ноль, а на выходе 2 – логическая единица. Причем такое состояние триггера сохраняется до момента t2, когда низким уровнем на входе делителя триггер снова вернется в исходное состояние. Использование триггера гарантирует сброс счетчиков в нулевое состояние.

) – логический ноль. В момент времени t1 равенства кода подсчитанных импульсов установленному коду переключателями SA, триггер сигналом сброса с элемента D4.1 переходит в состояние, когда на выходе 1 формируется логический ноль, а на выходе 2 – логическая единица. Причем такое состояние триггера сохраняется до момента t2, когда низким уровнем на входе делителя триггер снова вернется в исходное состояние. Использование триггера гарантирует сброс счетчиков в нулевое состояние.

При большом разбросе длительности переходных процессов и порогов срабатывания счетчиков D1 - D3 по входам R возможен случай, когда одна из микросхем устанавливается в нуль раньше других и сигнал низкого уровня на выходе D4.1 снимается раньше, чем остальные микросхемы установятся в нуль. В случае же использования триггера на элементах D4.2 и D4.3 длительность сигнала на входах сброса в нуль всех микросхем счетчиков равна длительности положительного импульса на входе делителя, т.е. t2-t1.

Принцип организации недвоичного модуля счета путем предварительной записи в триггеры счетчика определенного числа проиллюстрируем схемой рис.9.24. В схеме используются микросхемы параллельных двоично-десятичных реверсивных счетчиков К155ИЕ6 (D1, D2, D3). Микросхемы снабжены входами D1…D4 предварительной установки выходного кода, на которые подается параллельный четырехразрядный двоично-десятичный код модуля счета всего делителя частоты. Передача этого кода на соответствующие выходы 1, 2, 4, 8 микросхем осуществляется логическим нулем на входе L. Положительный счет в микросхеме К155ИЕ6 осуществляется подачей тактовых импульсов на прямой динамический вход «+1». При этом на входе «–1» и L должны быть логические единицы. Если счетные импульсы подавать на прямой динамический вход «–1», а на входы «+1» и L – логические единицы, то счетчик будет выполнять операцию обратного счета. При каждом десятом импульсе будет формироваться короткий выходной нулевой импульс на выходе «=9» в режиме суммирования и на выходе «=0» в режиме вычитания.

Рис.9.24. Схема делителя частоты с цифровым управлением модулем счета.

Таким образом, если соединить выходы «=0» счетчиков предыдущих разрядов с входами «–1» последующих разрядов, а на входы «+1» подать логическую единицу (подключить к потенциалу питания через ограничительный резистор R1), счетчики делителя будут работать в режиме декремента. На объединенные входы предварительной записи L всех микросхем счетчиков подается сигнал с выхода переноса микросхемы счетчика декады сотен, благодаря чему при достижении нулевого значения в цикле отрицательного счета во все микросхемы будет записываться двоично-десятичный код модуля счета. Цикл счета будет начинаться не с максимального значения 999, а с заданного двоично-десятичным кодом. При необходимости обнуления делителя микросхемы счетчиков снабжены прямым статическим входом сброса R. Резистор R2 подтягивает потенциал входов сброса микросхем счетчиков к пассивному нулевому уровню в отсутсвии сигнала их обнуления. Подобная схема удобна в тех случаях, когда модулем счета необходимо управлять цифровым кодом с выхода какого-либо устройства, например, микроконтроллера.

Регистры.

Регистрами называются последовательностные цифровые устройства, выполняющие функции приема, хранения и передачи информации. Информация в регистре хранится в виде двоичного кода, т.е. представлена комбинацией сигналов логического нуля и логической единицы. Каждому разряду кода, записанному в регистр, соответствует свой разряд регистра, выполненный, на основе триггеров RS-, D- или JK-типов. Регистры выполняют роль запоминающих устройств размером в одно n-разрядное слово, буферных элементов и преобразователей последовательно-параллельных кодов в цифровой аппаратуре, в том числе и измерительного назначения. Основным классификационным признаком, по которому различают регистры, является способ записи информации или кода числа в регистр. По этому признаку можно выделить регистры следующих типов:

- параллельные;

- последовательные;

- последовательно-параллельные.

В параллельные регистры запись (считывание) числа осуществляется параллельным кодом, т.е. во все разряды регистра одновременно. Последовательные регистры характеризуются последовательной записью (считыванием) кода числа, начиная с младшего разряда или старшего путем последовательного сдвига кода тактирующими импульсами. В последовательно-параллельных регистрах ввод или вывод информации может осуществляться как в параллельном, так и в последовательном кодах. Время ввода числа в регистр параллельного типа равно времени ввода одного разряда. Время ввода числа в регистр последовательного типа равно nT, где n - число разрядов вводимого числа, а T - период следования тактирующих сигналов, осуществляющих ввод (вывод) информации.

По способу представления вводимой информации различают регистры однофазного и парафазного типов. В однофазных регистрах информация вводится по одному каналу (прямому или инверсному). Информация на выходе регистра представляется в прямом, обратном или в обоих кодах. В парафазных регистрах ввод информации осуществляется по двум каналам одновременно (прямому и инверсному), т.е. информация на входе должна быть представлена одновременно в прямом и обратном кодах. Информация на выходе парафазного регистра, как правило, также представляется в прямом и инверсном кодах. В условном графическом обозначении функция регистра задается символами «RG», а в маркировке микросхем – символами «ИР».

Дата добавления: 2022-02-05; просмотров: 578;