Сумматор параллельного действия.

Состоит из отдельных разрядов, каждый из которых содержит одноразрядный сумматор. Поэтому такой сумматор называют ещё двоичным комбинационным многоразрядным сумматором.

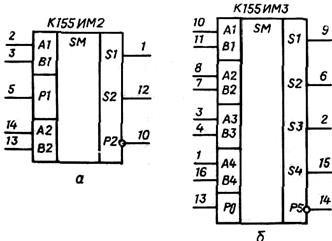

Условное обозначение сумматоров параллельного действия

В сериях ИС есть одно-, двух- и четырехразрядные сумматоры, которые можно объединять для получения сумматоров с любой разрядностью. Например, сумматоры из 155 серии К155ИМ1, К155ИМ2 и др. На Рис. 9 приведены условные обозначения двухразрядного К155ИМ2 и четырехразрядного К155ИМЗ сумматоров. ИС К155ИМ2 на выходе Sl формирует сумму младших разрядов A1, B1, а выходе S2 — старших разрядов А2, В2. ИС К155ИМЗ— быстродействующий сумматор. На входы А1…А4 и В1…В4 принимаются два четырехразрядных числа. Суммы разрядов входных чисел появляются на выходах S1…S4. На выходе Р5 формируется сигнал переноса. Сумматор может работать с двоичными числами как положительной, так и отрицательной логики.

Рис. 9 Условные обозначения сумматоров ИС К155ИМ2 (а) и К155ИМЗ (б)

Принцип работы.

При подаче слагаемых цифры их разрядов поступают на соответствующие одноразрядные сумматоры. Каждый из одноразрядных сумматоров формирует на своих выходах цифру соответствующего разряда суммы и перенос, передаваемый на вход одноразрядного сумматора следующего, более старшего разряда.

Функциональная схема двоичного комбинационного многоразрядного сумматора имеет вид, представленный на :Рис. 10.

Если значения слагаемых и суммы являются числами без знака (абсолютными числами) или числами со знаком в дополнительном коде, то один из входов младшего разряда сумматора (S0) не используется, на него должен быть подан постоянно сигнал логического нуля. Вместо полного сумматора в этом случае в младшем разряде можно использовать полусумматор.

Если слагаемые и сумма представляются в обратном коде, то выход переноса из старшего разряда Sn-1 соединяется с одним из входов младшего разряда сумматора S0 (на рисунке эта цепь показана пунктиром).

Для обеспечения высокого быстродействия параллельные сумматоры должны строиться на элементах, также имеющих высокое быстродействие. Трудности в достижении высокого быстродействия сумматора, построенного по схеме на Рис. 10, связаны с тем, что процесс распространения переносов в нём носит последовательный характер. Импульс переноса в каждом разряде формируется после того, как будет сформирован импульс переноса из предыдущего разряда. В наиболее неблагоприятном случае возникший в младшем разряде перенос может последовательно вызывать переносы во всех остальных разрядах. Для устранения данного недостатка пользуются рядом приёмов, как, например, использование блока ускоренного переноса.

Рис. 10 Схема двоичного комбинационного многоразрядного сумматора

Данный блок производит формирование переносов в параллельной форме, т.е. одновременно для всех разрядов. Переносы из этого блока поступают во все разрядные сумматоры одновременно. При этом, разрядные сумматоры не содержат цепей формирования переносов. Они формируют только суммы и значения слагаемых, для которых формирование переносов не требуется.

Таким образом, для построения многоразрядных сумматоров необходимы одноразрядные двоичные сумматоры.

Основное применение сумматоров – арифметико-логические устройства.

2. Арифметико-логическое устройство.

Арифметико-логическое устройство (АЛУ) - многокаскадное устройство функционального назначения, предназначенное для выполнения арифметических и логических операций над одним или двумя операндами.

Назначение.

Арифметико-логическое устройство любой вычислительной системы предназначено для выполнения арифметических и логических операций над двоично-кодированными операндами. В общем случае в АЛУ выполняются операции сложения, вычитания, умножения и деления двух чисел, операции поразрядного логического сложения и логического умножения, сдвиговые операции, преобразования кодов и некоторые другие операции.

Классификация.

1. По способу действия над операндами:

- последовательные (операнды представляются в последовательном коде, а операции производятся последовательно во времени разряд за разрядом; требуют меньших аппаратурных затрат);

- параллельные (операнды представляются параллельным кодом и операции выполняются параллельно над всеми разрядами операнда; более быстродействующие и, в связи с этим более широко используемые).

2. По способу организации работы:

- синхронные (имеют меньший объем оборудования за счет простоты устройства, но менее быстродействующие)

- асинхронные (имеют специальные устройства для определения момента фактического завершения операции).

3. По структуре:

- АЛУ с непосредственными связями (сумматор, схемы для выполнения логических операций и сдвигов, а также схемы передачи информации соединены непосредственно с выходами соответствующих регистров. При этом операнды, участвующие в микрооперации, снимаются с определенных регистров и результаты образуются также в определенных регистрах);

- АЛУ с магистральной структурой (входы схем для выполнения сложения, логических операций и сдвигов соединены с магистральными шинами данных или шиной данных, на которые с помощью мультиплексора может быть подключена информация с любого регистра АЛУ, а выходы этой аппаратуры подключены через мультиплексор по входным цепям регистров. При этом операнды для выполнения микрооперации могут быть взяты из любых регистров и результат также может быть передан в любой регистр).

4. По способу представления чисел

- АЛУ для чисел с фиксированной запятой;

- АЛУ для чисел с плавающей запятой;

- АЛУ для десятичных чисел.

5. По характеру использования основных узлов

- АЛУ блочного типа (имеется несколько блоков для выполнения основных операций; более предпочтительны);

- АЛУ многофункционального типа (все операции выполняются одним блоком за счет изменения его структуры посредством коммутационных схем).

Устройство:

В состав АЛУ входят следующие элементы:

1. Операционный блок, т.е. блок выполнения операции. В него входят: сумматоры, один или несколько регистров и логические схемы, устанавливающие фактические связи между составными частями АЛУ в зависимости от вида выполняемой операции.

2. Логические схемы, вырабатывающие признак результата (ПР).

3. Блок местного управления (БМУ) (служит для выработки управляющих сигналов, под действием которых реализуется операция в АЛУ. При отсутствии этого блока управление АЛУ осуществляется устройством управления вычислительной машины.).

4. Блок местной памяти (БМП) небольшой емкости.

Наибольшую смысловую нагрузку несёт операционное устройство, в состав которого входят:

- суммирующий блок или суммирующая часть АЛУ (выполняет простые арифметические операции (сложение, вычитание, вычитание модулей) и логические операции);

- блок умножения или блок умножения-деления (реализует сложные арифметические операции (деление и умножение)).

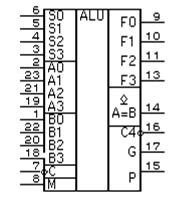

Условное обозначение:

АЛУ выполняться в виде отдельных микросхем или же может входить в состав одной СБИС - микропроцессора.

Специализированные микросхемы АЛУ, выполняют в соответствии с программой арифметические или логические операции над двумя двоичными числами. Примером условного обозначения микросхемы является ИМС типа К155ИП3. УГО данной микросхемы имеет вид (Рис. 11).

Рис. 11 УГО АЛУ

Данное АЛУ предназначено для действий с двумя четырехразрядными двоичными словами: A = A3A2A1A0 , B = B3B2B1B0. Конкретный вид операции, выполняемой микросхемой, задается 5-разрядным кодом на входах M S3 S2 S1 S0. Всего АЛУ может выполнить 32 операции: 16 логических (И, И-НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ и др.) и 16 арифметических (сложение, вычитание, удвоение, сравнение чисел и др.). Операции сложения и вычитания проводятся с ускоренным переносом из разряда в разряд. Кроме того, имеется вход приема сигнала переноса С. На выходах F0 , F1 , F2 , F3 формируются результаты логических преобразований и арифметических действий. На выходе переноса С4 образуется сигнал для старшего (пятого) разряда при выполнении арифметических операций. Дополнительные выходы - образования ускоренного переноса G и распространения ускоренного переноса P, используются при организации многоразрядных АЛУ в случае их сочетания с блоком ускоренного переноса типа К155ИП4. Вход А=В показывает равенство двух слов.

Схема АЛУ

Обобщенная структурная схема АЛУ приведена на Рис. 12. Здесь же показаны связи АЛУ с остальными устройствами машины.

Рис. 12 Обобщенная структурная схема АЛУ

Принцип работы:

Из ЗУ в АЛУ поступают операнды, над которыми производится та или иная операция. Действия над операндами сводятся к выполнению последовательности микроопераций, по которым осуществляется прием операндов в АЛУ, их преобразование и выдача результатов. Сигналы, определяющие состав и последовательность каждой группы микроопераций, выдает БМУ, если таковой имеется, или УУ. В процессе выполнения операции схема выработки признаков результата обеспечивает выдачу в БМУ сигнала «Признак результата операции», обеспечивающего в определенных ситуациях автоматическое изменение порядка следования микроопераций. В случае необходимости сигнал «Признак результата операции» передается в УУ.

Суммирующая схема АЛУ

Рассмотрим принцип действия и структуру суммирующей части АЛУ последовательного типа.

Упрощенная структурная схема суммирующей части последовательного АЛУ приведена на Рис. 13.

Рис. 13 Суммирующая часть АЛУ последовательного типа

Состав и назначение элементов схемы.

В состав схемы входят:

1. Одноразрядный комбинационный сумматор, имеющий три входа и два выхода.

Сумматор осуществляет суммирование трех цифр: двух цифр суммируемых кодов и цифры переноса, образовавшегося при сложении цифр предыдущего разряда.

2. Регистр-накопитель (РН).

Данный регистр является сдвиговым. В нём хранится одно из чисел до операции, а после выполнения операции—ее результат. Обычно данный регистр представляет собой закольцованный «бегущий» регистр. Хранящееся в нем число в каждом такте работы сдвигается на один разряд (бежит по регистру) в сторону младших разрядов.

3. Схема задержки.

Обеспечивает задержку переноса на выходе Р на интервал t., для обеспечения одновременной подачи на вход сумматора одноименных разрядов чисел при их сложении.

4. Логические схемы.

Обеспечивают выполнение заданной операции под действием управляющих сигналов, поступающих из УУ.

5. Схема выработки признаков результата.

Служит для выработки признака переполнения j и признака знака результата w.

Сигнал j вырабатывается в момент подачи на входы сумматора знаковых разрядов числа по правилу j=1, если оба числа положительные и при этом имеется перенос в знаковый разряд или оба числа отрицательные и при этом нет переноса в знаковый разряд; в противном случае j=0.

Сигнал w вырабатывается в момент появления знакового разряда результата на выходе сумматора (w=1, если результат отрицателен; w=0, если результат положителен, т. е. w соответствует значению знака).

Вывод:

Таким образом, основным элементом, определяющим работу суммирующей части АЛУ, является сумматор. Остальные схемы играют вспомогательную роль.

Заключение:

1. Сумматоры предназначены для суммирования двоичных и десятичных чисел.

2. Для построения многоразрядных сумматоров необходимы одноразрядные двоичные сумматоры.

3. АЛУ это многокаскадное устройство функционального назначения, предназначенное для выполнения арифметических и логических операций над одним или двумя операндами.

4. В связи со сложностью арифметических операций умножения и деления АЛУ состоит из отдельных блоков суммирования и умножения-деления.

Дата добавления: 2017-11-21; просмотров: 8264;