Полный двоичный одноразрядный комбинационный сумматор.

Одноразрядным комбинационным сумматором называется ЦУ, предназначенное для суммирования трех одноразрядных двоичных чисел: значений одноименных цифровых разрядов аi, bi и сигнала переноса из соседнего младшего разряда pi, выработки значения суммы в данном разряде Si, и переноса pi+1 в старший разряд.

Таким образом, одноразрядный комбинационный сумматор имеет три входа — аi, bi и рi и два выхода — Si и рi+1 (Рис. 5).

Другими словами, сумматор, имеющий три входа, называется полным сумматором.

Назначение полного сумматора.

Предназначен для поразрядного сложения двух многоразрядных чисел, когда в качестве третьего слагаемого приходится учитывать перенос из младшего разряда.

Условное графическое обозначение сумматора представлено ниже на Рис. 5.

Сумматор такого типа так же исполняется в различных сериях микросхем. Например, в 155 серии К155ИМ1. Здесь И – элемент арифметических и дискретных устройств; М – сумматор.

Рис. 5 УГО Одноразрядным комбинационным сумматором

Принцип действия и функционирование.

Одноразрядный комбинационный сумматор функционирует согласно таблице истинности (табл. 2).

Таблица 2

| ai | bi | pi | Si | pi+1 |

Используя таблицу истинности, запишем ПФ для суммы Si и переноса pi+1 в СДНФ:

Si=

pi+

pi+  bi

bi  +ai

+ai

+aibipi ,

+aibipi ,

pi+1=  bipi+ai

bipi+ai  pi+aibi

pi+aibi  aibipi .

aibipi .

ПФ для рi+1 можно минимизировать путем добавления двух слагаемых вида aibipi и попарного склеивания соседних слагаемых

pi+1 =bipi+aipi+aibi .

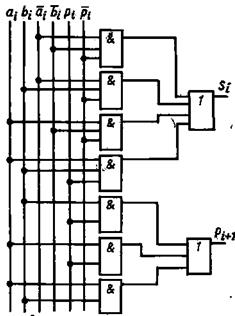

Схема одноразрядного комбинационного сумматора.

На Рис. 6 приведена функциональная схема одноразрядного комбинационного сумматора, реализованного по полученным формулам на ЛЭ И и ИЛИ. При реализации схем одноразрядных комбинационных сумматоров на других типах ЛЭ, как и при реализации схем комбинационных устройств, необходимо осуществить преобразование ПФ к виду, удобному для реализации на заданных типах ЛЭ.

Рис. 6 Вариант реализации одноразрядного комбинационного сумматора на ЛЭ И и ИЛИ

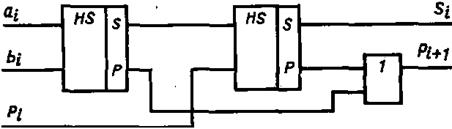

Одноразрядный комбинационный сумматор можно реализовать, используя два одноразрядных комбинационных полусумматора Рис. 7, схема ИЛИ служит для развязки выходов переносов обоих полусумматоров.

Рис. 7 Вариант реализации одноразрядного комбинационного сумматора на одноразрядных комбинационных полусумматорах

Таким образом, чаще всего используется двоичный одноразрядный комбинационный сумматор, который является составной частью многоразрядных сумматоров.

МНОГОРАЗРЯДНЫЙ СУММАТОР

В зависимости от способа ввода кодов слагаемых многоразрядные сумматоры делятся на два типа: последовательного и параллельного действия. В сумматоры первого типа коды чисел вводятся в последовательной форме, т.е. разряд за разрядом (младшим разрядом вперед), в сумматоры второго типа каждое слагаемое подается в параллельной форме, т.е. одновременно всеми разрядами.

Дата добавления: 2017-11-21; просмотров: 2982;