Логические элементы ТТЛ–технологии

Логические элементы (узлы) предназначены для выполнения различных логических (функциональных) операций над дискретными сигналами при двоичном способе их представления.

Преимущественное распространение получили логические элементы потенциального типа. В них используются дискретные сигналы, нулевому значению которых соответствует уровень низкого потенциала, а единичному значению – уровень высокого потенциала (отрицательного или положительного). Связь потенциального логического элемента с предыдущим и последующими узлами в системе осуществляется непосредственно, без применения реактивных компонентов. Благодаря этому преимуществу именно потенциальные логические элементы нашли почти исключительное применение в интегральном исполнении в виде микросхем. С позиций использования логических микросхем потенциального типа и проводится далее рассмотрение логических элементов.

Логические биполярные микросхемы чаще выполняют на транзисторах типа п-р-п снапряжением питания Ек> 0. Этим объясняется, что используемые здесь сигналы имеют положительную полярность. Уровню высокого положительного потенциала («1») на выходе соответствует закрытое состояние транзистора, а уровню низкого потенциала («0») – его открытое состояние. С этой точки зрения, в частности, и следует понимать действие сигнала на входе логического элемента, имеющего непосредственную связь с другими элементами в конкретной схеме. Для упрощения уровень низкого потенциала сигнала полагаем равным нулю, а процесс перехода транзистора из одного состояния в другое – достаточно быстрым.

Логические интегральные микросхемы являются элементами, на основе которых выполняются схемы цифровой техники.

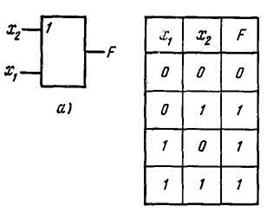

Логический элемент ИЛИ. Логический элемент ИЛИ имеет несколько входов и один общий выход. Его условное обозначение показано на рис. 6.1, а.

Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкции):

F = х1+ х2+ х3+ … + хn,

где F – функция;

х1 х2, х3,..., хn – аргументы (переменные, двоичные сигналы на входах).

Здесь функция F = 0, когда все ее аргументы равны нулю, и F = 1 при одном, нескольких или всех аргументах, равных единице.

Работу схемы двухвходового логического элемента ИЛИ иллюстрирует таблица истинности.

|

Рис. 6.1. УГО элемента ИЛИ (а), его таблица истинности

На практике возможны случаи, когда число входов используемого логического элемента ИЛИ превышает количество входных сигналов. Неиспользуемые входы заземляют. Тем самым исключается возможность прохождения помех через элемент ИЛИ от наводок по неиспользованным входам.

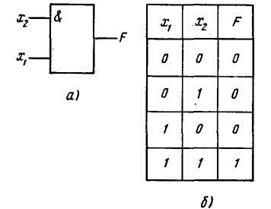

Логический элемент И. Логический элемент И также имеет несколько входов и один выход. Его условное обозначение показано на рис. 6.2, а.

Логический элемент И выполняет операцию логического умножения (конъюнкции):

F = х1• х2• х3• … • хn.

Здесь функция F = 0, когда хотя бы один из ее аргументов равен нулю, и F = 1 при всех аргументах, равных единице.

Рис. 6.2. Условное обозначение логического элемента И (а),

его таблица истинности

Работу схемы двухвходового логического элемента И иллюстрирует таблица истинности. Элемент И является схемой совпадения: сигнал «1» на выходе появляется при совпадении сигналов «1» на всех входах.

В случае применения логического элемента И, имеющего число входов, большее количества входных сигналов, неиспользуемые входы элемента соединяют с шиной «+» источника питания (подают сигнал логической «1»). Это уменьшает вероятность прохождения помех на выход элемента И от наводок по неиспользованным входам. Поведение логического элемента будет зависеть от комбинации входных сигналов.

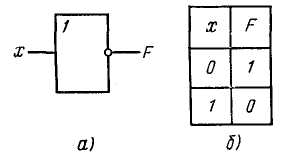

Логический элемент НЕ. Логический элемент НЕ имеет один вход и один выход. Его условное обозначение показано на рис. 6.3, а.

Рис. 6.3. Условное обозначение логического элемента НЕ (а),

его таблица истинности

Элемент НЕ выполняет операцию инверсии (отрицания), в связи, с чем его часто называют логическим инвертором. Им реализуется функция

F = х.

F = х.

Сигналу х = 0 на входе соответствует F = 1 и, наоборот, при х = 1 F = 0.

Работу схемы логического элемента НЕ иллюстрируют таблица истинности.

Логический элемент НЕ представляет собой ключевую схему на транзисторе (рис. 6.4.). Открытое состояние транзистора обеспечивается заданием тока базы, вводящего транзистор в режим насыщения.

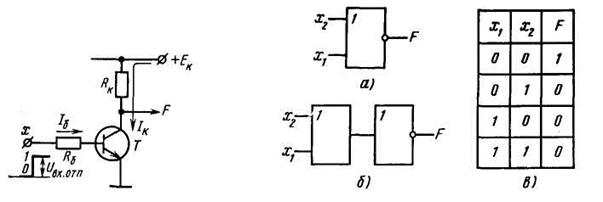

Рис. 6.4. Схема логического элемента НЕ. Условное обозначение логического элемента ИЛИ – НЕ (а), его функциональный эквивалент (б)

и таблица истинности (в)

Логический элемент ИЛИ – НЕ. Условное обозначение логического элемента ИЛИ – НЕ показано на рис. 6.5, а. Он объединяет элементы ИЛИ и НЕ с очередностью проведения операций, показанной на рис. 6.5 , б. В связи с этим входным сигналам, равным единице, соответствует логический «0» на выходе, а при нулевых сигналах на всех входах F = 1. Для двухвходового элемента ИЛИ – НЕ соотношение иллюстрирует таблица истинности, приведенная на рис. 6.5, в.

Функциональная операция, выполняемая элементом ИЛИ – НЕ при n входах, определяется выражением

F = xl + x2+ x3 + … + хn.

F = xl + x2+ x3 + … + хn.

На рис. 6.6 приведена схема логического элемента ИЛИ – НЕ, представляющая собой последовательное соединение элемента ИЛИ на диодах и элемента НЕ. Логические схемы подобного сочетания определяют, в частности, класс элементов так называемой д и о д н о-транзисторной логики (ДТЛ).

Рис. 6.6

Логический элемент И – НЕ. Условное обозначение логического элемента И – НЕ показано на рис. 6.7, а. Ему эквивалентна структурная схема, показанная на рис 6.7, б. Логической «1» на всех информационных входах соответствует логический «0» на выходе элемента. При логическом «0» на одном из входов создается логическая «1» на выходе. Для двухвходового элемента И – НЕ сказанное отражено в таблице истинности на рис. 6.7, в. Логическая функция элемента И – НЕ при п входах отвечает выражению

F = xl • x2• x3 • … • хn.

F = xl • x2• x3 • … • хn.

Рис. 6.7.

|

На рис. 6.8 приведена другая схема элемента И–НЕ, реализованная на транзисторах Схемы такого типа образуют класс элементов так называемой транзисторно-транзисторной логики (ТТЛ).

Рис. 6.8.

Основой этого класса элементов является использование многоэмиттерного транзистора Тм. Функция многоэмиттерного транзистора сводится к замене диодной части схемы элемента И–НЕ. Подобная замена технологически выгодна, поскольку изготовление многоэмиттерного транзистора в микросхемах не намного сложнее, чем изготовление обычного транзистора, а площадь, занимаемая многоэмиттерным транзистором в кристалле полупроводника, меньше диодной части элемента И–НЕ ДТЛ. От обычного транзистора многоэмиттерный транзистор отличается наличием нескольких (например, трех) эмиттерных областей с общими для всего транзистора базовым и коллекторным слоями,

Наличие усилительного элемента – транзистора – в логических микросхемах ИЛИ–НЕ и И–НЕ классов ДТЛ и ТТЛ определяет такое их важное преимущество, как сохранение неизменного уровня напряжения, соответствующего логической «1», в процессе передачи сигнала при их последовательном соединении. В связи о этим указанные элементы, а также элемент НЕ являются базовыми в микросхемотехнике. В общем корпусе выпускаемых микросхем обычно содержится несколько элементов одного типа.

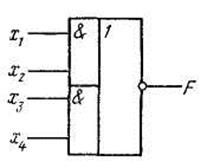

Комбинированные логические элементы. Существуют логические элементы в микросхемном исполнении, представляющие комбинацию ранее рассмотренных элементов и позволяющие осуществлять более сложные логические операции. На рис. 6.9.приведен элемент 2И–ИЛИ–НЕ.

Рис. 6.9.

Рис. 6.9.

Параметры логических элементов. К основным параметрам логических элементов (логических микросхем) относятся функциональные возможности элемента, быстродействие, потребляемая мощность и помехоустойчивость.

Функциональные возможности логического элемента определяются коэффициентом разветвления n по выходу и коэффициентом объединения m no входу. Под коэффициентом разветвления п логического элемента понимают количество входов аналогичных элементов, которое может быть подключено к его выходу, а под коэффициентом объединения т – число входов, которое может иметь элемент. Иными словами, коэффициент п характеризует нагрузочную способность микросхем.

Чем выше коэффициенты п и т, тем меньшее количество микросхем потребуется для создания конкретного устройства. Препятствием к увеличению коэффициента п является ухудшение других показателей элемента (помехоустойчивости, быстродействия) или нарушение нормального режима его работы.

Нагрузочная способность активного логического элемента существенно зависит от типа используемого в нем выходного транзисторного каскада (инвертора). Как правило, для большинства типов интегральных микросхем коэффициент п не превышает 4–10. Для увеличения нагрузочной способности к выходу элемента в случае необходимости подключают так называемый буферный усилитель с мощным многотранзисторным инвертором.

Быстродействие характеризует время реакции логического элемента на изменение сигналов на входах.

Показателем быстродействия логических микросхем является среднее время задержки прохождения сигнала через элемент: tз = (tз1 + tз2)/2.

Логические микросхемы подразделяются на сверхбыстродействующие (4.с <. 0,01 мкс), быстродействующие (4.с *в 0,01ч- 0,03 мкс), среднего быстродействия (t3.c < 0,03ч- 0,3 мкс), низкого быстродействия (4.с > 0,3 мкс).

Существенным параметром логических элементов является также потребляемая мощность от источника питания +£„• В зависимости от типа (серии) мощность, потребляемая логической микросхемой, составляет 250 мВт — 1 мкВт. Ее обычно определяют по средней мощности, потребляемой элементом в состояниях «0» и «1». Потребляемая мощность связана с быстродействием микросхем. В частности, микросхемы, потребляющие большую мощность, отличаются, как правило, и высоким быстродействием.

Снижение потребляемой мощности при сохранении высокого быстродействия является одной из важнейших задач микроэлектроники. Имеются два пути ее решения. Первый путь предполагает снижение мощности за счет уменьшения токов и напряжений питания. По такому пути идет развитие микросхем на биполярных транзисторах. Второй путь связан с созданием логических элементов, потребляющих мощность только в режиме переключения и не потребляющих ее в статических состояниях («0», «1»). Такие элементы основываются на применении дополняющих МДП-транзисторов.

Помехоустойчивость характеризует меру невосприимчивости логических элементов к изменению своих состояний под воздействием напряжения помех. Помехи, действующие на входе логической микросхемы, подразделяются на статические и импульсные (статическая и импульсная помехоустойчивость). Статическими называют помехи, напряжение которых остается постоянным в течение времени, значительно превышающего длительность переходных процессов в схеме Причиной их появления являются падения напряжения в проводниках, соединяющих микросхемы в устройстве. Статическая помехоустойчивость характеризуется максимальным напряжением помехи ип.стат, которое может быть подано на вход логического элемента, не вызывая при этом его ложного срабатывания.

Импульсные помехи обусловливаются различными наводками от окружающих работающих установок. По аналогии со статической помехоустойчивостью импульсная помехоустойчивость характеризуется напряжением импульса Uп.и. величина которого зависит от формы и длительности импульса.

К действию помех наиболее чувствительны микросхемы, имеющие низкий перепад логических уровней. На помехоустойчивость оказывают влияние вид схемы, режим работы транзисторов, напряжение источников питания и т. д.

Для уменьшения влияния помех необходимо рационально компоновать корпусы микросхем на печатных платах, осуществлять соответствующие развязки по целям напряжений питания, а в некоторых случаях экранировать цепи связи между элементами или отдельные блоки.

Элементной базой, используемой при построении ЦУ являются интегральные, логические элементы (ИЛЭ). В настоящее время выпускается широкая номенклатура ИЛЭ в составе различных серий интегральных микросхем на основе биполярных и полевых транзисторов. При построении ЦУ с заданными характеристиками выбор необходимых ИЛЭ производится в соответствии с определенным набором их параметров. Рассмотрим важнейшие из них.

Коэффициент разветвления по выходу Краз. Определяет число входов однотипных ИЛЭ, которые одновременно могут быть подключены к выходу данного логического элемента при сохранении его работоспособности в заданных условиях эксплуатации. Для различных элементов составляет от нескольких единиц до нескольких десятков.

Коэффициент объединения по входу Коб. Определяет число входных сигналов логического элемента, которые участвуют в формировании заданной логической функции.

Вид реализуемой логической функции. Используется широкий набор ИЛЭ: И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ. Перед обозначением логического элемента обычно указывается число его входов, по которым реализуется соответствующая логическая функция (т.е. коэффициент объединения по входу). В одной ИМС может быть несколько логических элементов, поэтому для сокращения обозначения состава микросхемы перед помещенным в круглые скобки наименованием элемента иногда указывают число этих элементов в одном корпусе микросхемы. Например, обозначению 4 (2И-НЕ) соответствует ИМС в составе четырех логических элементов И-НЕ с двумя входами каждый.

Статические характеристики: входная, определяющая зависимость входного тока от входного напряжения; выходная, задающая связь между выходными напряжениями и током; передаточная, которая определяет зависимость выходного напряжения от входного.

На рис. 6.10. приведена типовая передаточная характеристика ИЛЭ ТТЛ-типа. С ее помощью, например, можно оценить возможные уровни напряжения на всех входах и выходах логического элемента в том числе уровни напряжений, соответствующие состоянию логического нуля (U0) и логической единицы (U1), допустимые уровни статической помехи относительно этих уровней Uопом и U1пом, при которых еще не происходит ложного переключения логических элементов.

Временные (динамические) параметры

От них зависит быстродействие логического элемента. Чаще всего оценивается время перехода элемента из состояния единицы в состояние нуля t1,0 и перехода в обратное состояние t0,1 (рис. 6.11.).

Рис. 6.10.

Указанные временные интервалы измеряются на уровнях 0,1-0,9 от установившихся значений в цепочке из однотипных элементов. Другим важнейшим параметром, определяющим быстродействие, является время задержки распространения сигнала при включении t1,0здр. и выключении t0,1здр. логического элемента.

Рис. 6.11.

Измеряется на выходе по отношению к входу на уровнях 0,5 от установившихся значений. Во многих случаях удобно пользоваться средним временем задержки распространения сигнала tздр.ср., оцениваемым полусуммой t0,1здр. и t1,0здр.

Для построения ЦУ наиболее широкое применение находят ИДЭ на базе ТТЛ, ТТЛШ, ЭСЛ и КМОП-технологий.

| Технология ИЛЭ | Выполняемые функции | Краз | Коб | U, U, В | Tздр.ср. ИС |

| ТТЛ ТТЛШ ЭСЛ КМОП | И-НЕ, И-ИЛИ-НЕ, И, НЕ,ИЛИ И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ, И, НЕ ИЛИ-НЕ, ИЛИ,И ИЛИ-НЕ, И-НЕ, И-ИЛИ | 8-30 8-20 | 2-8 2-8 2-5 2-4 | £0,4 ³2,4 £0,5 ³2,7 -1,6 -1,0 0 Uп | 18-32 3-5 60-1200 |

Дата добавления: 2017-05-02; просмотров: 4156;