Организация блоков памяти.

В процессе конкретного выбора, чаще всего определяемого возможностями разработчика приобрести ту или иную БИС ЗУ и его симпатиями, возникает задача построить блок памяти большой емкости. При этом могут возникнуть следующие трудности.

1. Элементы памяти имеют недостаточное количество прямоадресуемых ячеек.

2. Элементы памяти обладают меньшей разрядностью ячеек, чем шина данных МПС.

3. Цикл "записи-чтения" элемента памяти больше программно-управляемого цикла обмена МП.

4. Элемент памяти динамичен.

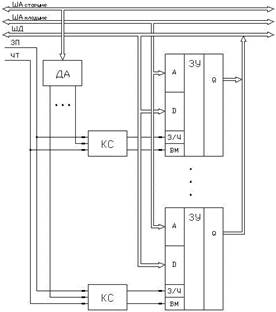

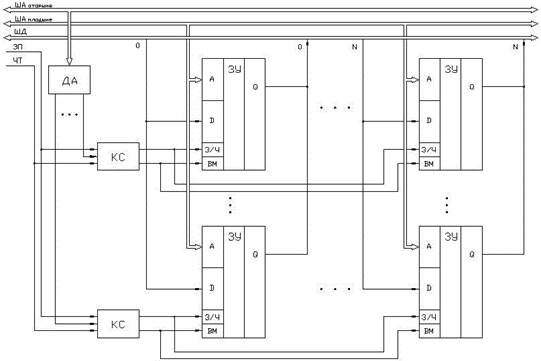

Рассмотрим последовательно пути преодоления указанных трудностей. В первом случае БИС ЗУ объединяются параллельно по младшим адресным шинам и шинам данных, имея разные комбинационные схемы логики управления, связанные с дешифратором адреса от старших адресных шин (см. рис.33.

|

|

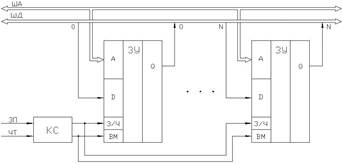

| Рис.33 | Рис.34 |

В случае нехватки разрядов БИС ЗУ объединяются параллельно по адресным шина, имея общую комбинационную схему управления (см. рис.34). Общий случай представлен на рисунке 35.

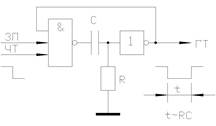

Для "медленных" ЗУ самым простым решением является использование асинхронного режима обмена с использованием управляющего сигнала "Готовность". Этот сигнал может быть сформирован по фронту управляющих сигналов "Запись" или "Чтение" с помощью схемы одновибратора (см. рис.36).

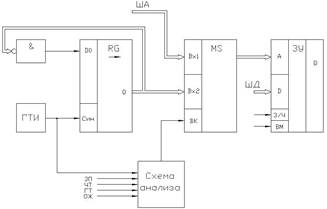

Блок сопряжения динамических ОЗУ несколько сложнее, так как требуется регенерация хранимой в них информации. Регенерация заключается в периодическом последовательном переборе входных шин адреса БИС ОЗУ. Регенерационная часть блока сопряжения строится на основе синхрогенератора (ГТИ), сдвигового регистра (RG) и мультиплексора (MS), который периодически отключает адресные шины БИС ОЗУ от магистрали и подсоединяет их к сдвиговому регистру. Регенерация может выполняться как с прерыванием обращения МП к ОЗУ, так и без него, если в цикле обращения к ОЗУ можно выделить достаточный временной интервал для работы мультиплексора (см. рис.37). Здесь "ВК" – выбор канала.

| |

| Рис.35 | |

|

|

| Рис.36 | Рис.37 |

Дата добавления: 2017-02-13; просмотров: 2465;