Цифровые узлы комбинационного типа

Интегральные логические элементы являются основой для построения цифровых устройств, выполняющих более сложные операции и относящихся к классу комбинационных устройств. Комбинационной называют логическую схему без запоминания переменных (логические схемы, не имеющие памяти), при этом выходные сигналы определяются комбинацией входных сигналов.

Основные из них:

· дешифраторы и шифраторы;

· мультиплексоры и демультиплексоры;

· двоичные сумматоры;

· цифровые компараторы

· преобразователи кодов и др.

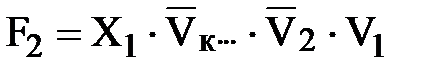

Дешифраторы . Это устройства, распознающие кодовые комбинации или схемы, используемые для преобразования n-разрядного двоичного кода в определенную комбинацию сигналов на выходе. Они строятся на базе конъюнкторов или других логических схем. Любую схему <<И>> можно рассматривать как элемент дешифратора. Для n-разрядного кода число кодовых комбинаций равно  . Поэтому полный дешифратор должен иметь n-входов и

. Поэтому полный дешифратор должен иметь n-входов и  выходов. Так как в код числа входят как единицы, так и нули, а схема “И” реагирует только на единичные уровни, то для работы конъюнкторов можно использовать инверсные сигналы.

выходов. Так как в код числа входят как единицы, так и нули, а схема “И” реагирует только на единичные уровни, то для работы конъюнкторов можно использовать инверсные сигналы.

Рассмотрим схему простейшего линейного дешифратора рис. 13.52. Данная схема имеет два прямых и два инверсных входа и четыре выхода. На выходе указаны комбинации входных сигналов, которые расшифровываются, – при этом на соответствующих выходах А1…А4 будет присутствовать единичный уровень.

Рис. 13.52

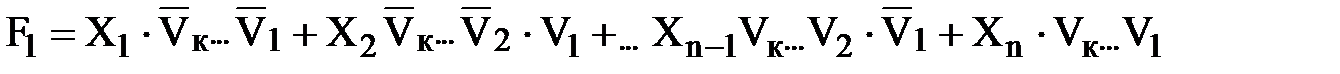

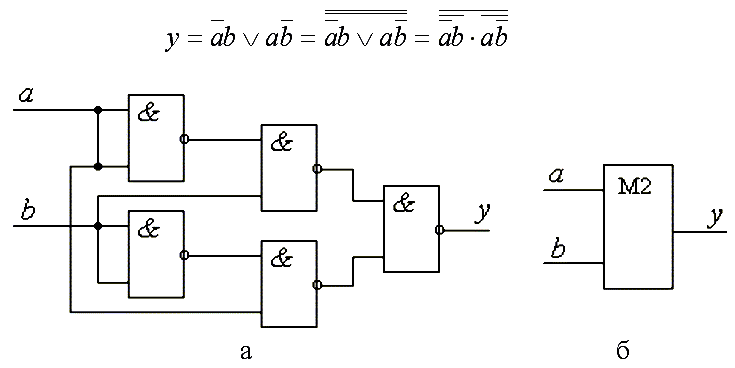

Мультиплексоры. В ряде случаев необходимо осуществить опрос логических состояний большого количества логических схем и передачи этих состояний на один выход. Устройство, это обеспечивающее, называется мультиплексором (коммутатором). Мультиплексор реализует логическую функцию

, 2.36)

, 2.36)

где V – адресные входы, X – информационные входы.

Для управления работой мулътиплексоров используются дешифраторы. Схема двухступенчатого мультиплексора на V = 2 и X = 4 показана на рис. 13.53.

Рис. 13.53

Мультиплексор построен как совокупность двухвходовых конъюнкторов (их число равно числу информационных входов), которые управляются дешифратором, имеющим количество выходов, равное числу информационных входов. Выходы конъюнкторов объединены схемой <<ИЛИ>>. Недостатком двухступенчатых схем является большое время задержки сигнала в дешифраторе и конъюнкторе.

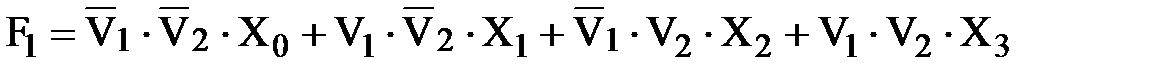

Схема мультиплексора, построенная по принципу линейного преобразования, приведена на рис. 13.54.

Рис. 13.54

Работа его описывается выражением

. (2.37)

. (2.37)

Если к примеру V1 = 0, V2 = 1, то

, (2.38)

, (2.38)

и т. д.

По рассмотренному принципу может быть построена любая логическая схема мультиплексора. С помощью n- адресных входов можно выбрать один из  информационных сигналов.

информационных сигналов.

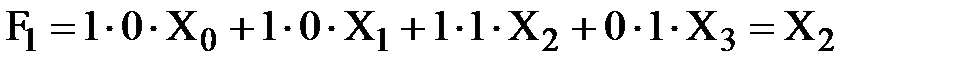

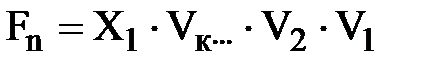

Демультиплексоры. Это схема, осуществляющая передачу одного информационного сигнала ( X1) на “n” информационных выходов. Она еще называется распределителем и осуществляет функцию, обратную функции мультиплексора. Работа демультиплексора описывается следующими логическими уравнениями:

(2.39)

(2.39)

(2.40)

(2.40)

(2.41)

(2.41)

(2.42)

(2.42)

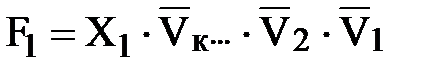

Если мультиплексор имеет “к” управляющих входов Vк…V1, то количество выходов  . Демультиплексор с прямыми и инверсными управляющими входами приведен на рис. 13.55.

. Демультиплексор с прямыми и инверсными управляющими входами приведен на рис. 13.55.

Рис. 13.55

Демультиплексоры можно использовать для преобразования последовательного кода в параллельный, а применение мультиплексора вместе с демультиплексором обеспечивает последовательную передачу информации с преобразованием параллельного кода в последовательный и последовательного в параллельный (рис. 13.56.)

Рис. 13.56

Сумматоры- это цифровые функциональные устройства, предназначенные для выполнения операции сложения чисел, представленных в различных кодах. По характеру действия сумматоры подразделяются на комбинационные, не имеющие элементов памяти, и накапливающие– запоминающие результаты вычислений при снятии входных сигналов.

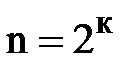

Сумматор по модулю два- Это устройство с двумя входами (а и b), на выходе у которого сигнал "1" появляется только в том случае, когда на входах действуют противоположные сигналы, т. е. "0" и "1". Сумматор не обладает памятью.

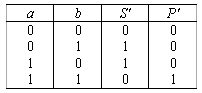

Eго таблица истинности имеют вид:

Название “по модулю два” этот сумматор получил потому, что y соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе И–НЕ схему сумматора по модулю два (рис. 13.30)

Рис. 13.59 Реализация сумматора по модулю два:

а – принципиальная схема; б – функциональная схема

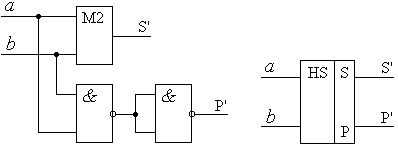

Полусумматор- Обеспечивает операцию сложения двух одноразрядных двоичных чисел a и b.

Так как при a = 1 и b = 1 получается перенос единицы в следующий разряд, полусумматор должен иметь два выхода: с одного снимается сигнал суммы по модулю два, а с другого - сигнал переноса P' = ab.

Таблица истинности полусумматора имеет вид:

Реализация полусумматора в базисе И–НЕ представлена на рис. 13.31

Условное обозначение полусумматора на схемах – HS (halfsum – полусумма), а полного сумматора – SM.

Рис.13.60. Схема полусумматора:

а – реализация в базисе И–НЕ; б – условное обозначение

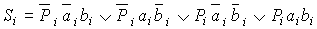

Полный сумматор- Это устройство для сложения трех одноразрядных двоичных чисел a, b, c, где c - сигнал переноса из предыдущего младшего разряда. Имеет два выхода S (сумма) и Р (перенос).

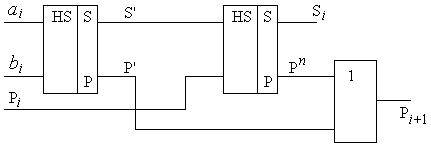

Полный сумматор можно построить из двух полусумматоров (рис. 13.32), отсюда и название – полусумматор, используя следующие логические уравнения

Рис. 13.61. Полный сумматор

На основе полного сумматора можно построить суммирующие устройства параллельного или последовательного действия для сложения многоразрядных двоичных чисел.

В цифровой схемотехнике операцию вычитания обычно заменяют сложением уменьшаемого с вычитаемым, представленным в дополнительном коде, поэтому вычитатели могут быть выполнены на основе сумматоров.

Дата добавления: 2019-09-30; просмотров: 696;