Последовательностные цифровые устройства

Триггер – простейшее последовательностное устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в другое под воздействием входных сигналов. Триггер является базовым элементом последовательностных логических устройств.

Триггеры классифицируют по следующим признакам:

· способу приема информации;

· принципу построения;

· функциональным возможностям.

Различают асинхронные и синхронные триггеры.

Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на входе синхронизации С (строб).

По функциональным возможностям триггеры разделяются на следующие классы:

· с раздельной установкой состояния 0 и 1 (RS – триггеры);

· универсальные (JK – триггеры);

· с приемом информации по одному входу D (D – триггеры, или триггеры задержки);

· со счетным входом Т (Т-триггеры).

Входы триггеров обычно обозначают следующим образом:

S – вход для установки состояния «1»;

R – вход для установки состояния «0»;

J – вход для установки в состояние «1» в универсальном триггере;

К – вход для установки в состояние «0» в универсальном триггере;

Т – счетный (общий) вход;

D – вход для установки в состояние «1» или в состояние «0»;

V – дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

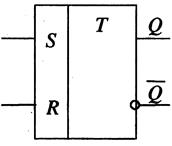

Рассмотрим асинхронный RS-триггер, имеющий условное графическое обозначение, приведенное на рис. 16.13. Триггер имеет два информационных входа: S и R. Закон функционирования триггеров удобно описывать таблицей переходов (таблицей истинности) (рис. 16.14). Через St, Rt, Qt обозначены соответствующие логические сигналы, имеющие место в некоторый момент времени t, а через Qt+1 – выходной сигнал в следующий момент времени t+1.

Рис. 16.13. RS-триггер Рис. 16.14. Таблица истинности

Комбинацию входных сигналов St=1, Rt=1 часто называют запрещенной, так как после нее триггер оказывается в состоянии (1 или 0), предсказать которое заранее невозможно. Подобных ситуаций следует избегать.

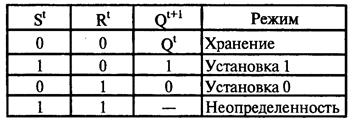

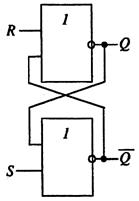

Рассмотренный триггер может быть реализован на двух элементах ИЛИ-НЕ (рис. 16.15). Микросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 16.16). При подаче на вход V низкого уровня выходы триггеров отключаются от выводов микросхем и переходят в третье, так называемое высокоимпедансное, состояние. При подаче на вход V логического сигнала «1» триггеры работают в соответствии с таблицей истинности (рис. 16.14).

Рис. 16.15. Триггер Рис. 16.16. Микросхема К564ТР2

на элементах ИЛИ-НЕ

Счетчики импульсов – это последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счета, заключающейся в изменении значения числа в счетчике на 1. По существу счетчик представляет собой совокупность соединенных определенным образом триггеров. Основной параметр счетчика – модуль счета. Это максимальное число единичных сигналов, которое может быть сосчитано счетчиком. Счетчики обозначаются через СТ.

Счетчики классифицируют:

по модулю счета:

· двоично-десятичные;

· двоичные;

· с произвольным постоянным модулем счета;

· с переменным модулем счета;

по направлению счета:

· суммирующие;

· вычитающие;

· реверсивные;

по способу формирования внутренних связей:

· с последующим переносом;

· с параллельным переносом;

· с комбинированным переносом;

· кольцевые.

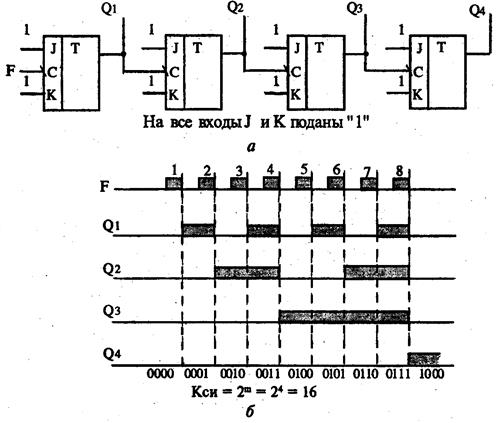

Рис. 16.17. Суммирующий счетчик на JK –триггерах

Рассмотрим суммирующий счетчик (рис. 16.17,а). Такой счетчик построен на четырех JK-триггерах, которые при наличии на обоих входах логического сигнала «1» переключаются в моменты появления на входах синхронизации отрицательных перепадов напряжения.

Временные диаграммы, иллюстрирующие работу счетчика, приведены на рис. 16.17,б. Через Ксн обозначен модуль счета (коэффициент счета импульсов). Состояние левого триггера соответствует младшему разряду двоичного числа, а правого – старшему разряду. В исходном состоянии на всех триггерах установлены логические нули. Каждый триггер меняет свое состояние лишь в тот момент, когда на него действует отрицательный перепад напряжения. Таким образом, данный счетчик реализует суммирование входных импульсов. Из временных диаграмм (рис. 16.17,б) видно, что частота каждого последующего импульса в два раза меньше, чем предыдущая, т.е. каждый триггер делит частоту входного сигнала на два, что и используется в делителях частоты.

Регистр – это последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Типичными является следующие операции:

· прием слова в регистр;

· передача слова из регистра;

· поразрядные логические операции;

· сдвиг слова влево или вправо на заданное число разрядов;

· преобразование последовательного кода слова в параллельный и обратно;

· установка регистра в начальное состояние (сброс).

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств.

Регистры классифицируются по следующим видам:

· накопительные (регистры памяти, хранения);

· сдвигающие.

В свою очередь сдвигающие регистры делятся:

· по способу ввода-вывода информации на

– параллельные;

– последовательные;

– комбинированные;

· по направлению передачи информации на

– однонаправленные;

– реверсивные.

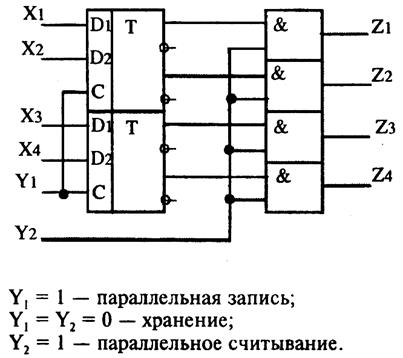

Рассмотрим накопительный регистр с параллельными вводом и выводом информации (рис. 16.18). Основой регистра являются D-триггеры, которые на своих выходах повторяют значения сигналов на входах Х1 – Х4 (информационные входы) при логическом сигнале 1 на входе синхронизации (т.е. осуществляется параллельный ввод входной информации в регистр).

Рис. 16.18. Накопительный регистр с параллельными вводом

и выводом информации

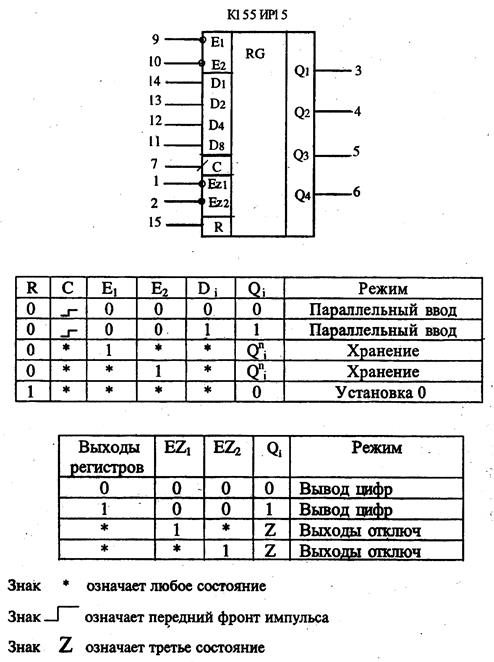

На четырех двухвходовых элементах «И» реализованы схемы совпадения, входные сигналы которых совпадают с выходными сигналами триггеров в том случае, когда на вход Y2 подана логическая единица. Таким образом осуществляется параллельный вывод информации. В качестве примера рассмотрим микросхему регистра К155ИР15. Приведем условное обозначение и таблицы внутренних и выходных состояний (рис. 16.19).

Рис. 16.19. Микросхема регистра К155ИР15

Дата добавления: 2016-11-29; просмотров: 2392;