Комбинационные цифровые устройства

Логические устройства разделяют на два класса: комбинационные и последовательностные.

Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени.

Иначе устройство называют последовательностным или конечным автоматом (цифровым автоматом, автоматом с памятью). В последовательностных устройствах обязательно имеются элементы памяти. Выходные сигналы последовательностных устройств определяются не только сигналами, имеющимися на входах в данный момент времени, но и состоянием элементов памяти. Таким образом, реакция последовательностного устройства на определенные входные сигналы зависит от предыстории его работы.

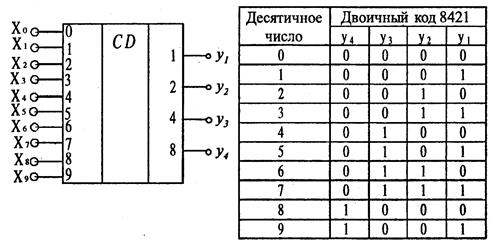

Шифратор – это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Число входов и выходов в полном шифраторе связано соотношением n=2m, где n – число входов, m – число выходов. Шифратор для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. Условное изображение такого шифратора и таблица соответствия кода приведены на рис. 11.1. Используя данную таблицу соответствия, запишем логические выражения, включая в логическую сумму те входные переменные, которые соответствуют единице некоторой выходной переменной. Так, на выходе y1 будет логическая «1» тогда, когда логическая «1» будет или на входе Х1, или Х2, или Х5, или Х7, или Х9, т.е. у1=Х1+Х3+Х5+Х7+Х9.

Рис. 16.1. Схема шифратора и таблица соответствия кода

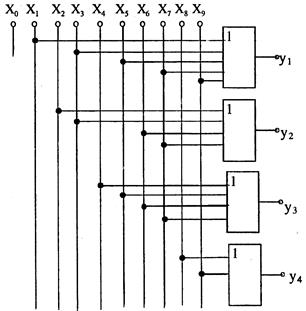

Представим на рис. 16.2 схему такого шифратора, используя элементы ИЛИ.

Рис. 16.2. Шифратор на логических элементах ИЛИ

Если на всех входах – логическая единица, то на всех выводах также логическая единица, что соответствует числу 0 в так называемом инверсном коде (1111). Если хотя бы на одном входе имеется логический ноль, то состояние выходных сигналов определяется наибольшим номером входа, на котором имеется логический ноль, и не зависит от сигналов на входах, имеющих меньший номер.

Основное назначение шифратора – преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе,

десятичный номер которого соответствует двоичному колу. Число входов и выходов в так называемом полном дешифраторе связано соотношением m=2n, где n – число входов, а m – число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет неполным, а если бы выходов было только 10, то он являлся бы полным.

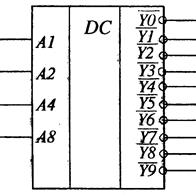

Обратимся для примера к дешифратору К555ИД6 серии К555 (рис. 16.3).

Рис. 16.3. Схема дешифратора

Дешифратор имеет 4 прямых входа, обозначенных через А1, …, А8. Аббревиатура А обозначает «адрес». Указанные входы называют адресным. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа. Дешифратор имеет 10 инверсных выходов  . Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах.

. Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах.

Дешифратор – одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств. Шифраторы и дешифраторы являются примерами простейших преобразователей кодов.

Преобразователями кодов называют устройства, предназначенные для преобразования одного кода в другой, при этом часто они выполняют нестандартные преобразования кодов. Преобразователи кодов обозначают через X/Y.

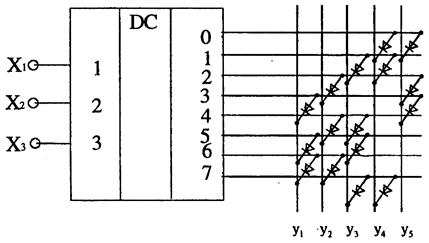

Рассмотрим особенности реализации преобразователя на примере преобразователя трехэлементного кода в пятиэлементный по таблице соответствия кодов, приведенной на рис. 16.4.

Рис. 16.4. Таблица соответствия кодов для преобразователя кодов

Здесь через N обозначено десятичное число, соответствующее входному двоичному коду. Преобразователи кодов создают по схеме дешифратор – шифратор. Дешифратор преобразует входной код в некоторое десятичное число, а затем шифратор формирует выходной код. Схема преобразователя, созданного по такому принципу, приведена на рис. 16.5.

Рис. 16.5. Схема преобразователя кодов

Мультиплексором называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX, а также через MS. Функционально мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов n и числом адресных входов m действует соотношение n=2m, то такой мультиплексор называют полным. Если n<2m, то мультиплексор называют неполным.

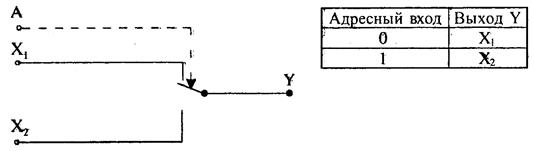

Рассмотрим функционирование двухвходового мультиплексора (2→1), который условно изображен в виде коммутатора, а состояние его входов Х1, Х2 и выхода Y приведено в таблице (рис. 16.6).

Рис. 16.6. Двухвходовый мультиплексор

Исходя из таблицы, можно записать следующее уравнение:

.

.

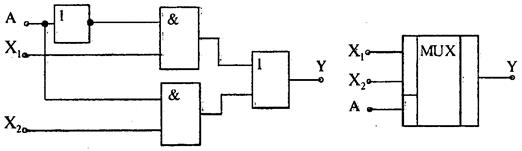

На рис. 16.7 показаны реализация такого устройства и его условное графическое обозначение. Основой данной схемы является являются две схемы совпадения на элементах И, которые при логическом уровне «1» на одном из своих входов повторяют на выходе то, что есть на другом входе.

Рис. 16.7. Реализация двухвходового мультиплексора

на логических элементах И

Мультиплексоры являются универсальными логическими устройствами, на основе которых создают различные комбинационные и последовательностные схемы. Мультиплексоры могут использовать в делителях частоты, триггерных устройствах, сдвигающих устройствах, для преобразования параллельного двоичного кода в последовательный и др.

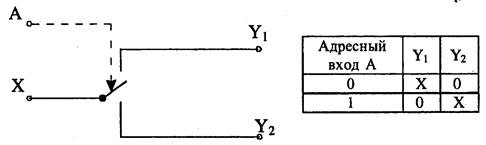

Демультиплексором называют устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS.

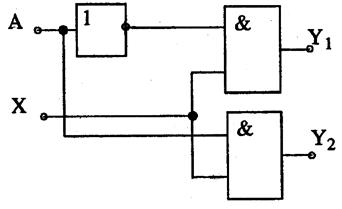

Рис. 16.8. Функциональная схема демультиплексора с двумя выходами

Если соотношение между числом выходов n и числом адресных входов m определяется равенством n=2m, то такой демультипликатор называют полным, при n<2m демультиплексор является неполным.

Рассмотрим функционирование демультипликатора с двумя выходами, который условно изображен в виде коммутатора, а состояние его входов приведено в таблице (рис. 16.8). Из этой таблицы следует:  , т.е. реализовать такое устройство можно так, как показано на рис. 16.9.

, т.е. реализовать такое устройство можно так, как показано на рис. 16.9.

Рис. 16.9. Реализация демультиплексора с двумя выходами

на логических элементах И

Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы – ИД. Выпускают дешифраторы (демультиплексоры) К155ИД3, К531ИД7 и др.

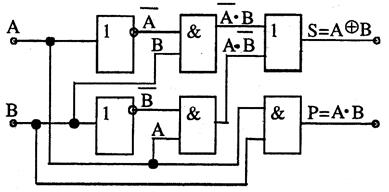

Сумматоры – это комбинационные устройства для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд P (рис. 16.10). Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями:  .

.

Очевидно, что по отношению к столбцу S реализуется логическая функция «исключающее ИЛИ», т.е. S=A  B.

B.

Рис. 16.10. Таблица истинности

Устройство, реализующее таблицу (рис. 16.10), называют полусумматором, и оно имеет логическую структуру, изображенную на рис. 16.11. Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде.

Рис. 16.11. Схема полусумматора

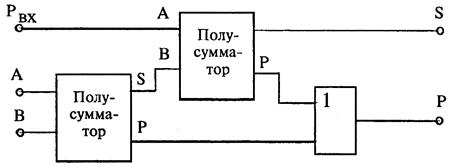

При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса.

Рис. 16.12. Схема полного сумматора

Такое устройство (рис. 16.12) называют полным сумматором и его можно представить как объединение двух полусумматоров (Рвх – дополнительный вход переноса).

Сумматор обозначают через SM.

Дата добавления: 2016-11-29; просмотров: 2285;